# agere

# FW323 05 1394A PCI PHY/Link Open Host Controller Interface

## **Features**

- 1394a-2000 OHCI link and PHY core function in single device:

- Enables smaller, simpler, more efficient motherboard and add-in card designs by replacing two components with one

- Enables lower system costs

- Leverages proven 1394a-2000 PHY core design

- Demonstrated compatibility with current *Microsoft* Windows<sup>®</sup> drivers and common applications

- Demonstrated interoperability with existing, as well as older, 1394 consumer electronics and peripherals products

- Feature-rich implementation for high performance in common applications

- Supports low-power system designs (CMOS implementation, power management features)

- Provides LPS, LKON, and CNA outputs to support legacy power management implementations

- OHCI:

- Complies with OHCI 1.1 WHQL requirements

- Complies with *Microsoft Windows* Logo Program System and Device Requirements

- Listed on Windows Hardware Compatibility List http://www.microsoft.com/hcl/results.asp

- Compatible with Microsoft Windows and MacOS<sup>®</sup> operating systems

- 4 Kbyte isochronous transmit FIFO

- 2 Kbyte asynchronous transmit FIFO

- 4 Kbyte isochronous receive FIFO

- 2 Kbyte asychronous receive FIFO

- Dedicated asynchronous and isochronous descriptor-based DMA engines

- Eight isochronous transmit contexts

- Eight isochronous receive contexts

- Prefetches isochronous transmit data

- Supports posted write transactions

- 1394a-2000 PHY core:

- Compliant with IEEE<sup>®</sup> 1394a-2000, Standard for a High Performance Serial Bus (Supplement)

- Provides three fully compliant cable ports, each supporting 400 Mbits/s, 200 Mbits/s, and 100 Mbits/s traffic

- Supports extended BIAS\_HANDSHAKE time for enhanced interoperability with camcorders

- While unpowered and connected to the bus, will not drive TPBIAS on a connected port even if receiving incoming bias voltage on that port

- Does not require external filter capacitor for PLL

- Supports PHY core-link interface initialization and reset

- Supports link-on as a part of the internal PHY core-link interface

- 25 MHz crystal oscillator and internal PLL provide transmit/receive data at 100 Mbits/s, 200 Mbits/s, and 400 Mbits/s, and internal link-layer controller clock at 50 MHz

- Interoperable across 1394 cable with 1394 physical layers (PHY core) using 5 V supplies

- Node power-class information signaling for system power management

- Supports ack-accelerated arbitration and fly-by concatenation

- Supports arbitrated short bus reset to improve utilization of the bus

- Fully supports suspend/resume

- Supports connection debounce

- Supports multispeed packet concatenation

- Supports PHY pinging and remote PHY access packets

- Reports cable power fail interrupt when voltage at CPS pin falls below 7.5 V

- Separate cable bias and driver termination voltage supply for each port

- Link:

- Cycle master and isochronous resource manager capable

- Supports 1394a-2000 acceleration features

# **Table of Contents**

#### Contents

| Features                                            | 1  |

|-----------------------------------------------------|----|

| FW323 Functional Overview                           | 7  |

| Other Features                                      | 7  |

| FW323 Functional Description                        | 7  |

| PCI Core                                            |    |

| Isochronous Data Transfer                           | 8  |

| Asynchronous Data Transfer                          | 8  |

| Asynchronous Register                               | 8  |

| Serial EEPROM Interface                             | 9  |

| Link Core                                           | 9  |

| PHY Core                                            | 9  |

| Pin Information                                     |    |

| Application Schematic                               | 18 |

| Internal Registers                                  |    |

| PCI Configuration Registers                         |    |

| Vendor ID Register                                  |    |

| Device ID Register                                  |    |

| PCI Command Register                                |    |

| PCI Status Register                                 |    |

| Class Code and Revision ID Register                 |    |

| Latency Timer and Class Cache Line Size Register    |    |

| Header Type and BIST Register                       |    |

| OHCI Base Address Register                          |    |

| PCI Subsystem Identification Register               |    |

| PCI Power Management Capabilities Pointer Register  |    |

| Interrupt Line and Pin Register                     |    |

| MIN_GNT and MAX_LAT Register                        |    |

| PCI OHCI Control Register                           |    |

| Capability ID and Next Item Pointer Register        |    |

| Power Management Capabilities Register              |    |

| Power Management Control and Status Register        |    |

| Power Management Extension Register                 |    |

| OHCI Registers                                      |    |

| OHCI Version Register                               |    |

| GUID ROM Register                                   |    |

| Asynchronous Transmit Retries Register              |    |

| CSR Data Register                                   |    |

| CSR Compare Register                                |    |

| CSR Control Register                                |    |

| Configuration ROM Header Register                   |    |

| Bus Identification Register                         |    |

| Bus Options Register                                |    |

| GUID High Register                                  |    |

| GUID Low Register                                   |    |

| Configuration ROM Mapping Register                  |    |

| Posted Write Address Low Register                   |    |

| Posted Write Address Low Register                   |    |

|                                                     |    |

| Vendor ID Register Host Controller Control Register |    |

|                                                     |    |

| Self-ID Count Register                              |    |

| Isochronous Receive Channel Mask High Register      | 02 |

#### Contents

## Page

| Isochronous Receive Channel Mask Low Register         |    |

|-------------------------------------------------------|----|

| Interrupt Event Register                              |    |

| Interrupt Mask Register                               |    |

| Isochronous Transmit Interrupt Event Register         |    |

| Isochronous Transmit Interrupt Mask Register          | 93 |

| Isochronous Receive Interrupt Event Register          |    |

| Isochronous Receive Interrupt Mask Register           |    |

| Fairness Control Register                             |    |

| Link Control Register                                 |    |

| Node Identification Register                          |    |

| PHY Core Layer Control Register                       |    |

| Isochronous Cycle Timer Register                      |    |

| Asynchronous Request Filter High Register             |    |

| Asynchronous Request Filter Low Register              |    |

| Physical Request Filter High Register                 |    |

| Physical Request Filter Low Register                  |    |

| Asynchronous Context Control Register                 |    |

| Asynchronous Context Command Pointer Register         |    |

| Isochronous Transmit Context Control Register         |    |

| Isochronous Transmit Context Command Pointer Register |    |

| Isochronous Receive Context Control Register          |    |

| Isochronous Receive Context Command Pointer Register  |    |

| Isochronous Receive Context Match Register            |    |

| FW323 Vendor Specific Registers                       |    |

| Isochronous DMA Control                               |    |

| Asynchronous DMA Control                              |    |

| Link Options                                          |    |

| Crystal Selection Considerations                      |    |

| Load Capacitance                                      |    |

| Board Layout                                          |    |

| Absolute Maximum Ratings                              |    |

| Electrical Characteristics                            |    |

| Timing Characteristics                                |    |

| ac Characteristics of Serial EEPROM Interface Signals |    |

| Internal Register Configuration                       |    |

| PHY Core Register Map for Cable Environment           |    |

| PHY Core Register Fields for Cable Environment        |    |

| Outline Diagrams                                      |    |

| 128-Pin TQFP                                          |    |

|                                                       |    |

## Figure

| Figure 1. FW323 Functional Block Diagram  | 7 |

|-------------------------------------------|---|

| Figure 2. PHY Core Block Diagram          |   |

| Figure 3. Pin Assignments for FW323       |   |

| Figure 4. Application Schematic for FW323 |   |

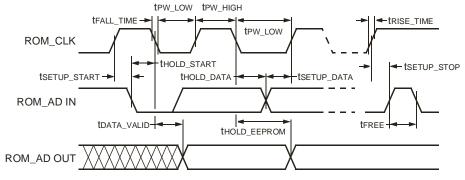

| Figure 5. Bus Timing                      |   |

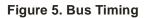

| Figure 6. Write Cycle Timing              |   |

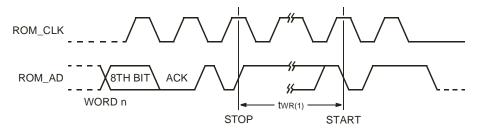

| Figure 7. Data Validity                   |   |

| Figure 8. Start and Stop Definition       |   |

| Figure 9. Output Acknowledge              |   |

|                                           |   |

## Table

| Table 1. Pin Descriptions                                              |    |

|------------------------------------------------------------------------|----|

| Table 2. Bit-Field Access Tag Description                              |    |

| Table 3. PCI Configuration Register Map                                |    |

| Table 4. Vendor ID Register                                            |    |

| Table 5. Device ID Register                                            |    |

| Table 6. PCI Command Register                                          |    |

| Table 7. PCI Command Register Description                              |    |

| Table 8. PCI Status Register                                           |    |

| Table 9. Class Code and Revision ID Register                           |    |

| Table 10. Class Code and Revision ID Register Description              |    |

| Table 11. Latency Timer and Class Cache Line Size Register             |    |

| Table 12. Latency Timer and Class Cache Line Size Register Description | 28 |

| Table 13. Header Type and BIST Register                                | 28 |

| Table 14. Header Type and BIST Register Description                    | 29 |

| Table 15. OHCI Base Address Register                                   | 30 |

| Table 16. OHCI Base Address Register Description                       | 31 |

| Table 17. PCI Subsystem Identification Register Description            | 32 |

| Table 18. PCI Power Management Capabilities Pointer Register           | 32 |

| Table 19. Interrupt Line and Pin Register                              | 33 |

| Table 20. Interrupt Line and Pin Register Description                  | 33 |

| Table 21. MIN_GNT and MAX_LAT Register                                 | 34 |

| Table 22. MIN_GNT and MAX_LAT Register Description                     | 34 |

| Table 23. PCI OHCI Control Register                                    |    |

| Table 24. PCI OHCI Control Register Description                        |    |

| Table 25. Capability ID and Next Item Pointer Register                 |    |

| Table 26. Capability ID and Next Item Pointer Register Description     |    |

| Table 27. Power Management Capabilities Register                       |    |

| Table 28. Power Management Capabilities Register Description           |    |

| Table 29. Power Management Control and Status Register                 |    |

| Table 30. Power Management Control and Status Register Description     |    |

| Table 31. Power Management Extension Register                          |    |

| Table 32. Power Management Extension Register Description              |    |

| Table 33. OHCI Register Map                                            |    |

| Table 34. OHCI Version Register                                        |    |

| Table 35. OHCI Version Register Description                            |    |

| Table 36. GUID ROM Register                                            |    |

| Table 37. GUID ROM Register Description                                |    |

| Table 38. Asynchronous Transmit Retries Register                       |    |

| Table 39. Asynchronous Transmit Retries Register Description           |    |

| Table 40. CSR Data Register                                            |    |

| Table 41. CSR Data Register Description                                |    |

| Table 42. CSR Compare Register                                         |    |

| Table 43. CSR Compare Register Description                             | 55 |

| Table 44. CSR Control Register                                         | 56 |

| Table 45. CSR Control Register Description                             |    |

| Table 46. Configuration ROM Header Register                            |    |

| Table 47. Configuration ROM Header Register Description                |    |

| Table 48. Bus Identification Register                                  |    |

| Table 49. Bus Identification Register Description                      |    |

| Table 50. Bus Options Register                                         |    |

| Table 50. Bus Options Register Description                             |    |

|                                                                        |    |

## Table

| Table 52. GUID High Register                                         |     |

|----------------------------------------------------------------------|-----|

| Table 53. GUID High Register Description                             |     |

| Table 54. GUID Low Register                                          |     |

| Table 55. GUID Low Register Description                              |     |

| Table 56. Configuration ROM Mapping Register                         |     |

| Table 57. Configuration ROM Mapping Register Description             |     |

| Table 58. Posted Write Address Low Register                          |     |

| Table 59. Posted Write Address Low Register Description              |     |

| Table 60. Posted Write Address High Register                         |     |

| Table 61. Posted Write Address High Register Description             |     |

| Table 62. Vendor ID Register                                         |     |

| Table 63. Vendor ID Register Description                             |     |

| Table 64. Host Controller Control Register                           |     |

| Table 65. Host Controller Control Register Description               |     |

| Table 66. Self-ID Buffer Pointer Register                            | 78  |

| Table 67. Self-ID Buffer Pointer Register Description                |     |

| Table 68. Self-ID Count Register                                     |     |

| Table 69. Self-ID Count Register Description                         |     |

| Table 70. Isochronous Receive Channel Mask High Register             |     |

| Table 71. Isochronous Receive Channel Mask High Register Description |     |

| Table 72. Isochronous Receive Channel Mask Low Register              |     |

| Table 73. Isochronous Receive Channel Mask Low Register Description  |     |

| Table 74. Interrupt Event Register                                   |     |

| Table 75. Interrupt Event Register Description                       |     |

| Table 76. Interrupt Mask Register                                    |     |

| Table 77. Interrupt Mask Register Description                        |     |

| Table 78. Isochronous Transmit Interrupt Event Register              |     |

| Table 79. Isochronous Transmit Interrupt Event Register Description  |     |

| Table 80. Isochronous Transmit Interrupt Mask Register               |     |

| Table 81. Isochronous Receive Interrupt Event Register               |     |

| Table 82. Isochronous Receive Interrupt Event Description            |     |

| Table 83. Isochronous Receive Interrupt Mask Register                |     |

| Table 84. Fairness Control Register                                  |     |

| Table 85. Fairness Control Register Description                      |     |

| Table 86. Link Control Register                                      |     |

| Table 87. Link Control Register Description                          |     |

| Table 88. Node Identification Register                               |     |

| Table 89. Node Identification Register Description                   |     |

| Table 90. PHY Core Layer Control Register                            |     |

| Table 91. PHY Core Layer Control Register Description                |     |

| Table 92. Isochronous Cycle Timer Register                           |     |

| Table 93. Isochronous Cycle Timer Register Description               |     |

| Table 94. Asychronous Request Filter High Register                   |     |

| Table 95. Asynchronous Request Filter High Register Description      |     |

| Table 96. Asynchronous Request Filter Low Register                   |     |

| Table 97. Asynchronous Request Filter Low Register Description       |     |

| Table 98. Physical Request Filter High Register                      |     |

| Table 99. Physical Request Filter High Register Description          |     |

| Table 100. Physical Request Filter Low Register                      |     |

| Table 101. Physical Request Filter Low Register Description          |     |

| Table 102. Asynchronous Context Control Register                     | 119 |

## Table

| Table 103. Asynchronous Context Control Register Description                 | .120 |

|------------------------------------------------------------------------------|------|

| Table 104. Asynchronous Context Command Pointer Register                     | .121 |

| Table 105. Asynchronous Context Command Pointer Register Description         |      |

| Table 106. Isochronous Transmit Context Control Register                     |      |

| Table 107. Isochronous Transmit Context Control Register Description         |      |

| Table 108. Isochronous Transmit Context Command Pointer Register             |      |

| Table 109. Isochronous Transmit Context Command Pointer Register Description | .126 |

| Table 110. Isochronous Receive Context Control Register                      | .127 |

| Table 111. Isochronous Receive Context Control Register Description          | .128 |

| Table 112. Isochronous Receive Context Command Pointer Register              | .129 |

| Table 113. Isochronous Receive Context Command Pointer Register Description  | .130 |

| Table 114. Isochronous Receive Context Match Register                        |      |

| Table 115. Isochronous Receive Context Match Register Description            | .132 |

| Table 116. FW323 Vendor Specific Registers Description                       |      |

| Table 117. Isochronous DMA Control Registers Description                     |      |

| Table 118. Asynchronous DMA Control Registers Description                    |      |

| Table 119. Link Registers Description                                        |      |

| Table 120. ROM Format Description                                            |      |

| Table 121. Absolute Maximum Ratings                                          |      |

| Table 122. Analog Characteristics                                            |      |

| Table 123. Driver Characteristics                                            |      |

| Table 124. Device Characteristics                                            |      |

| Table 125. Switching Characteristics                                         |      |

| Table 126. Clock Characteristics                                             |      |

| Table 127. ac Characteristics of Serial EEPROM Interface Signals             | .141 |

| Table 128. PHY Core Register Map for the Cable Environment                   |      |

| Table 129. PHY Core Register Fields for Cable Environment                    |      |

| Table 130. PHY Core Register Page 0: Port Status Page                        |      |

| Table 131. PHY Core Register Port Status Page Fields                         | .148 |

| Table 132. PHY Core Register Page 1: Vendor Identification Page              |      |

| Table 133. PHY Core Register Vendor Identification Page Fields               | .149 |

## FW323 Functional Overview

- PCI:

- Revision 2.2 compliant

- 33 MHz/32-bit operation

- Programmable burst size for PCI data transfer

- Supports PCI Bus Power Management Interface Specification v.1.1

- Supports clockrun protocol per PCI Mobile Design Guide

- Global byte swap function

## **Other Features**

- I<sup>2</sup>C serial ROM interface

- CMOS process

- 3.3 V operation, 5 V tolerant inputs

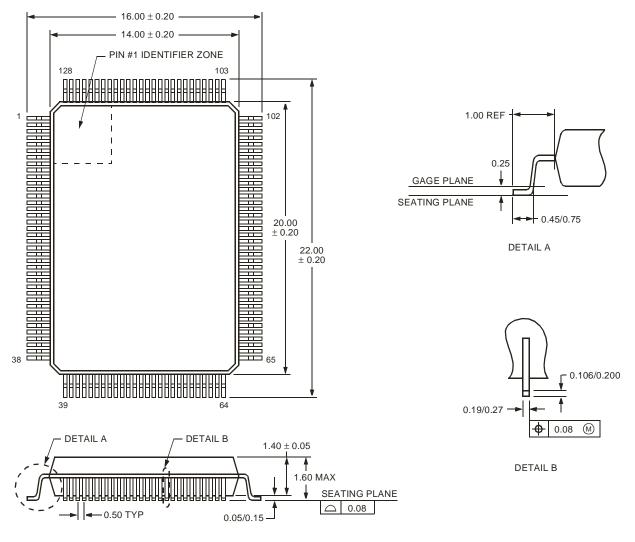

- 128-pin TQFP package

The FW323 is the Agere Systems Inc. implementation of a high-performance, PCI bus-based open host controller for implementation of *IEEE* 1394a-2000 compliant systems and devices. Link-layer functions are handled by the FW323, utilizing the on-chip 1394a-2000 compliant link core and physical layer core. A high-performance and cost-effective solution for connecting and servicing multiple *IEEE* 1394 (both 1394-1995 and 1394a-2000) peripheral devices can be realized.

5-6250 (F).e

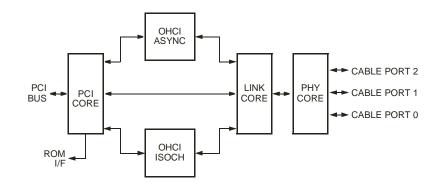

#### Figure 1. FW323 Functional Block Diagram

#### FW323 Functional Description

The FW323 is comprised of five major functional sections (see Figure 1): PCI core, isochronous data transfer, asynchronous data transfer, link core, and PHY core. The following is a general description of each of the five major sections.

## **PCI** Core

The PCI core serves as the interface to the PCI bus. It contains the state machines that allow the FW323 to respond properly when it is the target of the transaction. During 1394 packet transmission or reception, the PCI core arbitrates for the PCI bus and enables the FW323

Agere Systems Inc.

to become the bus master for reading the different buffer descriptors and management of the actual data transfers to/from host system memory.

The PCI core also supports the *PCI Bus Power Management Interface Specification* v.1.1. Included in this support is a standard power management register interface accessible through the PCI configuration space. Through this register interface, software is able to transition the FW323 into four distinct power consumption states (D0, D1, D2, and D3). This permits software to selectively increase/decrease the power consumption of the FW323 for reasons such as periods of system inactivity or power conservation. In addition, the FW323 also includes support for hardware wake-up mechanisms through power management events

(PMEs). When the FW323 is in a low-power state, PMEs provide a hardware mechanism for requesting a software wake-up. Together, the power management register interface and PME support within the FW323 combine to form an efficient means for implementing power management.

## Isochronous Data Transfer

The isochronous data transfer logic handles the transfer of isochronous data between the link core and the PCI interface module. It consists of the isochronous register module, the isochronous transmit DMA module, the isochronous receive DMA module, the isochronous transmit FIFO, and the isochronous receive FIFO.

#### **Isochronous Register**

The isochronous register module operates on PCI slave accesses to OHCI registers within the isochronous block. The module also maintains the status of interrupts generated within the isochronous block and sends the isochronous interrupt status to the OHCI interrupt handler block.

#### Isochronous Transmit DMA (ITDMA)

The isochronous transmit DMA module moves data from host memory to the link core, which will then send the data to the 1394 bus. It consists of isochronous contexts, each of which is independently controlled by software, and can send data on a 1394 isochronous channel.

During each 1394 isochronous cycle, the ITDMA module will service each of the contexts and attempt to process one 1394 packet for each context. If a context is active, ITDMA will request access to the PCI bus. When granted PCI access, a descriptor block is fetched from host memory. This data is decoded by ITDMA to determine how much data is required and where in host memory the data resides. ITDMA initiates another PCI access to fetch this data, which is placed into the transmit FIFO for processing by the link core. If the context is not active, it is skipped by ITDMA for the current cycle.

After processing each context, ITDMA writes a cycle marker word in the transmit FIFO to indicate to the link core that there is no more data for this isochronous cycle. As a summary, the major steps for the FW323 ITDMA to transmit a packet are the following:

- 1. Fetch a descriptor block from host memory.

- 2. Fetch data specified by the descriptor block from host memory and place it into the isochronous transmit FIFO.

- 3. Data in FIFO is read by the link and sent to the PHY core device interface.

#### Isochronous Receive DMA (IRDMA)

The isochronous receive DMA module moves data from the receive FIFO to host memory. It consists of isochronous contexts, each of which is independently controlled by software. Normally, each context can process data on a single 1394 isochronous channel. However, software can select one context to receive data on multiple channels.

When IRDMA detects that the link core has placed data into the receive FIFO, it immediately reads out the first word in the FIFO, which makes up the header of the isochronous packet. IRDMA extracts the channel number for the packet and packet filtering controls from the header. This information is compared with the control registers for each context to determine if any context is to process this packet.

If a match is found, IRDMA will request access to the PCI bus. When granted PCI access, a descriptor block is fetched from host memory. The descriptor provides information about the host memory block allocated for the incoming packet. IRDMA then reads the packet from the receive FIFO and writes the data to host memory via the PCI bus.

If no match is found, IRDMA will read the remainder of the packet from the receive FIFO, but not process the data in any way.

## Asynchronous Data Transfer

The ASYNC block is functionally partitioned into two independent logic blocks for transmitting and receiving 1394 packets. The ASYNC\_TX unit is responsible for packet transmission while the ASYNC\_RX unit processes received data.

## **Asynchronous Register**

The asynchronous register module operates on PCI slave accesses to OHCI registers within the asynchronous block. The module also maintains the status of interrupts generated within the asynchronous block and sends the asynchronous interrupt status to the OHCI interrupt handler block.

#### Asynchronous Transmit (ASYNC\_TX)

The ASYNC\_TX block of the FW323 manages the asynchronous transmission of either request or response packets. The mechanism for asynchronous transmission of requests and responses are similar. The only difference is the system memory location of the buffer descriptor list when processing the two contexts. Therefore, the discussion below, which is for asynchronous transmit requests, parallels that of the asynchronous transmit response. The FW323 asynchronous transmission of packets involves the following steps:

- 1. Fetch complete buffer descriptor block from host memory.

- 2. Get data from system memory and store into async FIFO.

- 3. Request transfer of data from FIFO to link device.

- 4. Handle retries, if any.

- 5. Handle errors in steps 1 to 4.

- 6. End the transfer if there are no errors.

#### Asynchronous Receive (ASYNC\_RX)

The ASYNC\_RX block of the FW323 manages the processing of received packets. Data packets are parsed and stored in a dedicated asynchronous receive FIFO. Command descriptors are read through the PCI interface to determine the disposition of the data arriving through the 1394 link.

The header of the received packet is processed to determine, among other things, the following:

- 1. The type of packet received.

- 2. The source and destinations.

- 3. The data and size, if any.

- 4. The operation required, if any. For example, compare and swap operation.

The ASYNC block also handles DMA transfers of self-ID packets during the 1394 bus initialization phase and block transactions associated with physical request.

## Serial EEPROM Interface

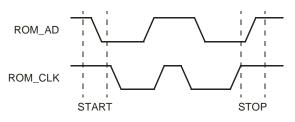

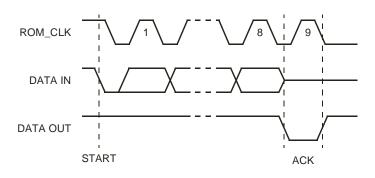

The FW323 features an I<sup>2</sup>C compliant serial ROM interface that allows for the connection of an external serial EEPROM. The interface provides a mechanism to store configuable data such as the global unique identification (GUID) within an external EEPROM. The interface consists of the ROM\_AD and ROM\_CLK pins.

ROM\_CLK is an output clock provided by the FW323 to the external EEPROM. ROM\_AD is bidirectional and is used for serial data/control transfer between the FW323 and the external EEPROM. The FW323 uses this interface to read the contents of the serial EEPROM during initial power-up or when a hardware reset occurs. The FW323 also makes the serial ROM interface visible to software through the OHCI defined GUID ROM register. When the FW323 is operational, the GUID ROM register allows software to initiate reads to the external EEPROM.

#### Link Core

It is the responsibility of the link to ascertain if a received packet is to be forwarded to the OHCI for processing. If so, the packet is directed to a proper inbound FIFO for either the isochronous block or the asynchronous block to process. The link is also responsible for CRC generation on outgoing packets and CRC checking on receiving packets.

To become aware of data to be sent outbound on 1394 bus, the link must monitor the OHCI FIFOs looking for packets in need of transmission. Based on data received from the OHCI block, the link will form packet headers for the 1394 bus. The link will alert the PHY core as to the availability of the outbound data. It is the link's function to generate CRC for the outbound data. The link also provides PHY core register access for the OHCI.

## **PHY Core**

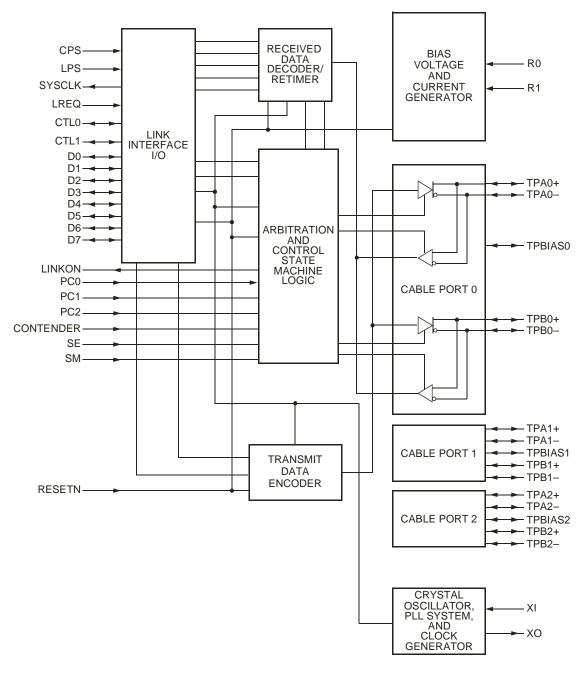

The PHY core provides the analog physical layer functions needed to implement a three-port node in a cable-based *IEEE* 1394-1995 and *IEEE* 1394a-2000 network.

Each cable port incorporates two differential line transceivers. The transceivers include circuitry to monitor the line conditions as needed for determining connection status, for initialization and arbitration, and for packet reception and transmission. The PHY core interfaces with the link core.

The PHY core requires either an external 24.576 MHz crystal or crystal oscillator. The internal oscillator drives an internal phase-locked loop (PLL), which generates the required 400 MHz reference signal. The 400 MHz reference signal is internally divided to provide the 49.152 MHz, 98.304 MHz, and 196.608 MHz clock signals that control transmission of the outbound clock signal is also supplied to the associated LLC for synchronization of the two chips and is used for resynchronization of the received data.

The PHY/link interface is a direct connection and does not provide isolation.

Data bits to be transmitted through the cable ports are received from the LLC on two, four, or eight data lines (D[0:7]), and are latched internally in the PHY in synchronization with the 49.152 MHz system clock. These bits are combined serially, encoded, and transmitted at 98.304 Mbits/s, 196.608 Mbits/s, or 393.216 Mbits/s as the outbound data-strobe information stream. During transmission, the encoded data information is transmitted differentially on the TPA and TPB cable pair(s).

During packet reception, the TPA and TPB transmitters of the receiving cable port are disabled, and the receivers for that port are enabled. The encoded data information is received on the TPA and TPB cable pair. The received data-strobe information is decoded to recover the receive clock signal and the serial data bits. The serial data bits are split into two, four, or eight parallel streams, resynchronized to the local system clock, and sent to the associated LLC. The received data is also transmitted (repeated) out of the other active (connected) cable ports.

Both the TPA and TPB cable interfaces incorporate differential comparators to monitor the line states during initialization and arbitration. The outputs of these comparators are used by the internal logic to determine the arbitration status. The TPA channel monitors the incoming cable common-mode voltage. The value of this common-mode voltage is used during arbitration to set the speed of the next packet transmission. In addition, the TPB channel monitors the incoming cable common-mode voltage for the presence of the remotely supplied twisted-pair bias voltage. This monitor is called bias-detect.

The TPBIAS circuit monitors the value of incoming TPA pair common-mode voltage when local TPBIAS is inactive. Because this circuit has an internal current source and the connected node has a current sink, the monitored value indicates the cable connection status. The monitor is called connect-detect.

Both the TPB bias-detect monitor and TPBIAS connect-detect monitor are used in suspend/resume signaling and cable connection detection.

The PHY core provides a 1.86 V nominal bias voltage for driver load termination. This bias voltage, when seen through a cable by a remote receiver, indicates the presence of an active connection. The value of this bias voltage has been chosen to allow interoperability between transceiver chips operating from 5 V or 3 V nominal supplies. This bias voltage source should be stabilized by using an external filter capacitor of approximately 0.33  $\mu$ F.

The port transmitter circuitry and the receiver circuitry are disabled when the port is disabled, suspended, or disconnected.

The line drivers in the PHY core operate in a highimpedance current mode and are designed to work with external 112  $\Omega$  line-termination resistor networks. One network is provided at each end of each twisted pair cable. Each network is composed of a pair of series-connected 56  $\Omega$  resistors. The midpoint of the pair of resistors that is directly connected to the twisted pair A (TPA) signals is connected to the TPBIAS voltage signal. The midpoint of the pair of resistors that is directly connected to the twisted-pair B (TPB) signals is coupled to ground through a parallel RC network with recommended resistor and capacitor values of 5 k $\Omega$  and 220 pF, respectively. The value of the external resistors are specified to meet the draft standard specifications when connected in parallel with the internal receiver circuits.

The driver output current, along with other internal operating currents, is set by an external resistor. This resistor is connected between the R0 and R1 signals and has a value of  $2.49 \text{ k}\Omega \pm 1\%$ .

Four signals are used as inputs to set four configuration status bits in the self-identification (self-ID) packet. These signals are hardwired high or low as a function of the equipment design. PC[0:2] are the three signals that indicate either the need for power from the cable or the ability to supply power to the cable. The fourth signal (CONTENDER), as an input, indicates whether a node is a contender for bus manager. When the CONTENDER signal is asserted, it means the node is a contender for bus manager. When the signal is not asserted, it means that the node is not a contender. The contender bit corresponds to bit 20 in the self-ID packet, PC0 corresponds to bit 21, PC1 corresponds to bit 22, and PC2 corresponds to bit 23 (see Table 4-29 of the IEEE 1394-1995 standard for additional details).

When the power supply of the PHY core is removed while the twisted-pair cables are connected, the PHY core transmitter and receiver circuitry has been designed to present a high impedance to the cable in order to not load the TPBIAS signal voltage on the other end of the cable.

For reliable operation, the TPB± signals must be terminated using the normal termination network,

regardless of whether a cable is connected to port or not connected to a port. For those applications, when FW323 is used with one or more of the ports not brought out to a connector, those unused ports may be left unconnected without normal termination. When a port does not have a cable connected, internal connect-detect circuitry will keep the port in a disconnected state.

**Note:** All gap counts on all nodes of a 1394 bus must be identical. This may be accomplished by using PHY core configuration packets (see Section 4.3.4.3 of *IEEE* 1394-1995 standard) or by using two bus resets, which resets the gap counts to the maximum level (3Fh). The internal link power status (LPS) signal works with the internal LinkOn signal to manage the LLC power usage of the node. The LPS signal indicates that the LLC of the node is powered up or down. If LPS is inactive for more than 1.2  $\mu$ s and less than 25  $\mu$ s, the internal PHY/link interface is reset.

If LPS is inactive for greater than 25 µs, the PHY will disable the internal PHY/link interface to save power. The FW323 continues its repeater function. If the PHY then receives a link-on packet, the internal LinkOn signal is activated to output a 6.114 MHz signal, which can be used by the LLC to power itself up. Once the LLC is powered up, the internal LPS signal communicates this to the PHY and the internal PHY/link interface is enabled. Internal LinkOn signal is turned off when LCtrl bit is set.

Three of the signals are used to set up various test conditions used in manufacturing. These signals (SE, SM, and PTEST) should be connected to VSS for normal operation.

5-5459.i(F) R.01

Figure 2. The PHY Core Block Diagram

## **Pin Information**

Note: Active-low signals within this document are indicated by an N following the symbol names.

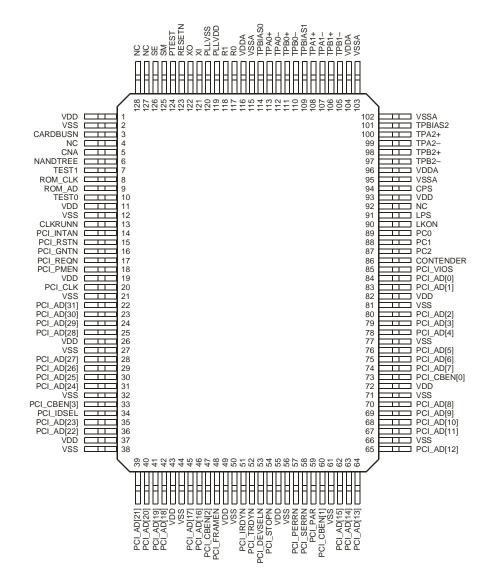

Figure 3. Pin Assignments for the FW323

5-7838 (F)a

#### Table 1. Pin Descriptions

| Pin | Symbol*        | Туре | Description                                                                                                                                                                                                                                |

|-----|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VDD            | —    | Power.                                                                                                                                                                                                                                     |

| 2   | VSS            |      | Ground.                                                                                                                                                                                                                                    |

| 3   | CARDBUSN       | I    | <b>CardBusN (Active-Low).</b> Selects mode of operation for PCI output buffers. Tie low for cardbus operation, high for PCI operation. An internal pull-up is provided to force buffers to PCI mode, if no connection is made to this pin. |

| 4   | NC             |      | No Connect.                                                                                                                                                                                                                                |

| 5   | CNA            | 0    | <b>Cable Not Active.</b> CNA output is provided for use in legacy power management systems.                                                                                                                                                |

| 6   | NANDTREE       | 0    | Nand Tree Test Output. When the chip is placed into<br>the NAND tree test mode, the pin is the output of the<br>NAND tree logic. This pin is not used during functional<br>operation.                                                      |

| 7   | TEST1          | I    | Test. Used for device testing. Tie to VSS.                                                                                                                                                                                                 |

| 8   | ROM_CLK        | I/O  | ROM Clock.                                                                                                                                                                                                                                 |

| 9   | ROM_AD         | I/O  | ROM Address/Data.                                                                                                                                                                                                                          |

| 10  | TEST0          | I    | Test. Used for device testing. Tie to VSS.                                                                                                                                                                                                 |

| 11  | VDD            |      | Power.                                                                                                                                                                                                                                     |

| 12  | VSS            |      | Ground.                                                                                                                                                                                                                                    |

| 13  | CLKRUNN        | I/O  | CLKRUNN (Active-Low). Optional signal for PCI<br>mobile environment. If not used, CLKRUNN pin needs<br>to be pulled down to VSS for correct operation.                                                                                     |

| 14  | PCI_INTAN      | 0    | PCI Interrupt (Active-Low).                                                                                                                                                                                                                |

| 15  | PCI_RSTN       | I    | PCI Reset (Active-Low).                                                                                                                                                                                                                    |

| 16  | PCI_GNTN       | I    | PCI Grant Signal (Active-Low).                                                                                                                                                                                                             |

| 17  | PCI_REQN       | 0    | PCI Request Signal (Active-Low).                                                                                                                                                                                                           |

| 18  | PCI_PMEN       | 0    | PCI Power Management Event (Active-Low).                                                                                                                                                                                                   |

| 19  | VDD            |      | Power.                                                                                                                                                                                                                                     |

| 20  | PCI_CLK        | I    | PCI Clock Input. 33 MHz.                                                                                                                                                                                                                   |

| 21  | VSS            |      | Ground.                                                                                                                                                                                                                                    |

| 22  | PCI_AD[31]     | I/O  | PCI Address/Data Bit.                                                                                                                                                                                                                      |

| 23  | PCI_AD[30]     | I/O  | PCI Address/Data Bit.                                                                                                                                                                                                                      |

| 24  | PCI_AD[29]     | I/O  | PCI Address/Data Bit.                                                                                                                                                                                                                      |

| 25  | PCI_AD[28]     | I/O  | PCI Address/Data Bit.                                                                                                                                                                                                                      |

| 26  | VDD            |      | Power.                                                                                                                                                                                                                                     |

| 27  | VSS            | —    | Ground.                                                                                                                                                                                                                                    |

| 28  | PCI_AD[27]     | I/O  | PCI Address/Data Bit.                                                                                                                                                                                                                      |

| 29  | PCI_AD[26]     | I/O  | PCI Address/Data Bit.                                                                                                                                                                                                                      |

| 30  | PCI_AD[25]     | I/O  | PCI Address/Data Bit.                                                                                                                                                                                                                      |

| 31  | PCI_AD[24]     | I/O  | PCI Address/Data Bit.                                                                                                                                                                                                                      |

| 32  | VSS            | —    | Ground.                                                                                                                                                                                                                                    |

| 33  | PCI_CBEN[3]    | I/O  | PCI Command/Byte Enable (Active-Low).                                                                                                                                                                                                      |

| 34  | PCI_IDSEL      | I    | PCI ID Select.                                                                                                                                                                                                                             |

| 35  | <br>PCI_AD[23] | I/O  | PCI Address/Data Bit.                                                                                                                                                                                                                      |

#### Table 1. Pin Descriptions (continued)

| Pin | Symbol*     | Туре | Description                                  |

|-----|-------------|------|----------------------------------------------|

| 36  | PCI_AD[22]  | I/O  | PCI Address/Data Bit.                        |

| 37  | Vdd         |      | Power.                                       |

| 38  | Vss         | —    | Ground.                                      |

| 39  | PCI_AD[21]  | I/O  | PCI Address/Data Bit.                        |

| 40  | PCI_AD[20]  | I/O  | PCI Address/Data Bit.                        |

| 41  | PCI_AD[19]  | I/O  | PCI Address/Data Bit.                        |

| 42  | PCI_AD[18]  | I/O  | PCI Address/Data Bit.                        |

| 43  | Vdd         | —    | Power.                                       |

| 44  | Vss         | —    | Ground.                                      |

| 45  | PCI_AD[17]  | I/O  | PCI Address/Data Bit.                        |

| 46  | PCI_AD[16]  | I/O  | PCI Address/Data Bit.                        |

| 47  | PCI_CBEN[2] | I/O  | PCI Command/Byte Enable Signal (Active-Low). |

| 48  | PCI_FRAMEN  | I/O  | PCI Frame Signal (Active-Low).               |

| 49  | Vdd         | —    | Power.                                       |

| 50  | Vss         | —    | Ground.                                      |

| 51  | PCI_IRDYN   | I/O  | PCI Initiator Ready Signal (Active-Low).     |

| 52  | PCI_TRDYN   | I/O  | PCI Target Ready Signal (Active-Low).        |

| 53  | PCI_DEVSELN | I/O  | PCI Device Select Signal (Active-Low).       |

| 54  | PCI_STOPN   | I/O  | PCI Stop Signal (Active-Low).                |

| 55  | Vdd         | —    | Power.                                       |

| 56  | Vss         | —    | Ground.                                      |

| 57  | PCI_PERRN   | I/O  | PCI Parity Error Signal (Active-Low).        |

| 58  | PCI_SERRN   | I/O  | PCI System Error Signal (Active-Low).        |

| 59  | PCI_PAR     | I/O  | PCI Parity Signal.                           |

| 60  | PCI_CBEN[1] | I/O  | PCI Command/Byte Enable Signal (Active-Low). |

| 61  | Vss         | —    | Ground.                                      |

| 62  | PCI_AD[15]  | I/O  | PCI Address/Data Bit.                        |

| 63  | PCI_AD[14]  | I/O  | PCI Address/Data Bit.                        |

| 64  | PCI_AD[13]  | I/O  | PCI Address/Data Bit.                        |

| 65  | PCI_AD[12]  | I/O  | PCI Address/Data Bit.                        |

| 66  | Vss         |      | Ground.                                      |

| 67  | PCI_AD[11]  | I/O  | PCI Address/Data Bit.                        |

| 68  | PCI_AD[10]  | I/O  | PCI Address/Data Bit.                        |

| 69  | PCI_AD[9]   | I/O  | PCI Address/Data Bit.                        |

| 70  | PCI_AD[8]   | I/O  | PCI Address/Data Bit.                        |

| 71  | Vss         | —    | Ground.                                      |

| 72  | Vdd         |      | Power.                                       |

| 73  | PCI_CBEN[0] | I/O  | PCI Command/Byte Enable Signal (Active-Low). |

| 74  | PCI_AD[7]   | I/O  | PCI Address/Data Bit.                        |

| 75  | PCI_AD[6]   | I/O  | PCI Address/Data Bit.                        |

| 76  | PCI_AD[5]   | I/O  | PCI Address/Data Bit.                        |

| 77  | Vss         | —    | Ground.                                      |

| 78  | PCI_AD[4]   | I/O  | PCI Address/Data Bit.                        |

#### Table 1. Pin Descriptions (continued)

| Pin | Symbol*   | Туре       | Description                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|-----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 79  | PCI_AD[3] | I/O        | PCI Address/Data Bit.                                                                                                                                                                                                                                                                                                                                                                                       |

| 80  | PCI_AD[2] | I/O        | PCI Address/Data Bit.                                                                                                                                                                                                                                                                                                                                                                                       |

| 81  | Vss       | —          | Ground.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 82  | Vdd       | —          | Power.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 83  | PCI_AD[1] | I/O        | PCI Address/Data Bit.                                                                                                                                                                                                                                                                                                                                                                                       |

| 84  | PCI_AD[0] | I/O        | PCI Address/Data Bit.                                                                                                                                                                                                                                                                                                                                                                                       |

| 85  | PCI_VIOS  | —          | PCI Signaling Indicator. (5 V or 3.3 V.)                                                                                                                                                                                                                                                                                                                                                                    |

| 86  | CONTENDER | I          | <b>Contender.</b> On hardware reset, this input sets the default value of the CONTENDER bit indicated during self-ID. This bit can be programmed by tying the signal to VDD (high) or to ground (low).                                                                                                                                                                                                      |

| 87  | PC2       |            | Power-Class Indicators. On hardware reset, these                                                                                                                                                                                                                                                                                                                                                            |

| 88  | PC1       |            | inputs set the default value of the power class indicated                                                                                                                                                                                                                                                                                                                                                   |

| 89  | PC0       |            | during self-ID. These bits can be programmed by tying the signals to VDD (high) or to ground (low).                                                                                                                                                                                                                                                                                                         |

| 90  | LKON      | 0          | <b>Link On.</b> Signal from the internal PHY core to the internal link core. This signal is provided as an output for use in legacy power management systems.                                                                                                                                                                                                                                               |

| 91  | LPS       | 0          | <b>Link Power Status.</b> Signal from the internal link core to the internal PHY core. LPS is provided as an output for use in legacy power management systems.                                                                                                                                                                                                                                             |

| 92  | NC        | —          | No Connect.                                                                                                                                                                                                                                                                                                                                                                                                 |

| 93  | Vdd       | —          | Power.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 94  | CPS       | Ι          | <b>Cable Power Status.</b> CPS is normally connected to the cable power through a 400 k $\Omega$ resistor. This circuit drives an internal comparator that detects the presence of cable power. This information is maintained in one internal register and is available to the LLC by way of a register read (see <i>IEEE</i> 1394a-2000, <i>Standard for a High Performance Serial Bus</i> (Supplement)). |

| 95  | VSSA      | _          | <b>Analog Circuit Ground.</b> All VSSA signals should be tied together to a low-impedance ground plane.                                                                                                                                                                                                                                                                                                     |

| 96  | Vdda      | _          | <b>Analog Circuit Power.</b> VDDA supplies power to the analog portion of the device.                                                                                                                                                                                                                                                                                                                       |

| 97  | TPB2-     | Analog I/O | <b>Port 2, Port Cable Pair B.</b> TPB2± is the port B connection to the twisted-pair cable. Board traces from each                                                                                                                                                                                                                                                                                          |

| 98  | TPB2+     |            | pair of positive and negative differential signal pins<br>should be kept matched and as short as possible to the<br>external load resistors and to the cable connector.                                                                                                                                                                                                                                     |

| 99  | TPA2-     | Analog I/O | <b>Port 2, Port Cable Pair A.</b> TPA2± is the port A connection to the twisted-pair cable. Board traces from each                                                                                                                                                                                                                                                                                          |

| 100 | TPA2+     |            | pair of positive and negative differential signal pins<br>should be kept matched and as short as possible to the<br>external load resistors and to the cable connector.                                                                                                                                                                                                                                     |

## Table 1. Pin Descriptions (continued)

| Pin | Symbol* | Туре       | Description                                                                                                                                                                                                                         |

|-----|---------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 101 | TPBIAS2 | Analog I/O | <b>Port 2, Twisted-Pair Bias.</b> TPBIAS2 provides the 1.86 V nominal bias voltage needed for proper operation of the twisted-pair cable drivers and receivers and for sending a valid cable connection signal to the remote nodes. |

| 102 | VSSA    |            | <b>Analog Circuit Ground.</b> All VSSA signals should be tied together to a low-impedance ground plane.                                                                                                                             |

| 103 | VSSA    | —          | <b>Analog Circuit Ground.</b> All VSSA signals should be tied together to a low-impedance ground plane.                                                                                                                             |

| 104 | Vdda    | —          | <b>Analog Circuit Ground.</b> VDDA supplies power to the analog portion of the device.                                                                                                                                              |

| 105 | TPB1–   | Analog I/O | <b>Port 1, Port Cable Pair B.</b> TPB1± is the port B connection to the twisted-pair cable. Board traces from each                                                                                                                  |

| 106 | TPB1+   |            | pair of positive and negative differential signal pins<br>should be kept matched and as short as possible to the<br>external load resistors and to the cable connector.                                                             |

| 107 | TPA1–   | Analog I/O | <b>Port 1, Port Cable Pair A.</b> TPA1± is the port A connection to the twisted-pair cable. Board traces from each                                                                                                                  |

| 108 | TPA1+   |            | pair of positive and negative differential signal pins<br>should be kept matched and as short as possible to the<br>external load resistors and to the cable connector.                                                             |

| 109 | TPBIAS1 | Analog I/O | <b>Port 1, Twisted-Pair Bias.</b> TPBIAS1 provides the 1.86 V nominal bias voltage needed for proper operation of the twisted-pair cable drivers and receivers and for sending a valid cable connection signal to the remote nodes. |

| 110 | TPB0–   | Analog I/O | <b>Port 0, Port Cable Pair B.</b> TPB0± is the port B connection to the twisted-pair cable. Board traces from each                                                                                                                  |

| 111 | TPB0+   |            | pair of positive and negative differential signal pins<br>should be kept matched and as short as possible to the<br>external load resistors and to the cable connector.                                                             |

| 112 | TPA0-   | Analog I/O | <b>Port 0, Port Cable Pair A.</b> TPA0± is the port A connection to the twisted-pair cable. Board traces from each                                                                                                                  |

| 113 | TPA0+   |            | pair of positive and negative differential signal pins<br>should be kept matched and as short as possible to the<br>external load resistors and to the cable connector.                                                             |

| 114 | TPBIAS0 | Analog I/O | <b>Port 0, Twisted-Pair Bias.</b> TPBIAS0 provides the 1.86 V nominal bias voltage needed for proper operation of the twisted-pair cable drivers and receivers and for sending a valid cable connection signal to the remote nodes. |

| 115 | VSSA    | _          | <b>Analog Circuit Ground.</b> All VSSA signals should be tied together to a low-impedance ground plane.                                                                                                                             |

| 116 | Vdda    | —          | Analog Circuit Power. VDDA supplies power to the analog portion of the device.                                                                                                                                                      |

#### Table 1. Pin Descriptions (continued)

| Pin           | Symbol*  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 117       118 | R0<br>R1 |      | <b>Current Setting Resistor.</b> An internal reference voltage is applied to a resistor connected between R0 and R1 to set the operating current and the cable driver output current. A low temperature-coefficient resistor (TCR) with a value of 2.49 k $\Omega \pm 1\%$ should be used to meet the <i>IEEE</i> 1394-1995 standard requirements for output voltage limits.                                                       |

| 119           | PLLVdd   | -    | <b>Power for PLL Circuit.</b> PLLVDD supplies power to the PLL circuitry portion of the device.                                                                                                                                                                                                                                                                                                                                    |

| 120           | PLLVss   | —    | <b>Ground for PLL Circuit.</b> PLLVss is tied to a low-<br>impedance ground plane.                                                                                                                                                                                                                                                                                                                                                 |

| 121           | XI<br>XO | _    | <b>Crystal Oscillator.</b> XI and XO connect to a 24.576 MHz parallel resonant fundamental mode crystal. Although when a 24.576 MHz clock source is used, it can be connected to XI with XO left unconnected. The optimum values for the external shunt                                                                                                                                                                            |

| 122           |          |      | capacitors are dependent on the specifications of the<br>crystal used. The suggested values of 12 pF are appro-<br>priate for crystal with 7 pF specified loads. For more<br>details, see the Crystal Selection Considerations<br>section.                                                                                                                                                                                         |

| 123           | RESETN   |      | <b>Reset (Active-Low).</b> When RESETN is asserted low (active), a bus reset condition is set on the active cable ports and the internal PHY core logic is reset to the reset start state. An internal pull-up resistor, which is connected to VDD, is provided, so only an external delay capacitor and resistor are required. This input is a standard logic buffer and can also be driven by an open-drain logic output buffer. |

| 124           | PTEST    |      | Test. Used for device testing. Tie to Vss.                                                                                                                                                                                                                                                                                                                                                                                         |

| 125           | SM       | I    | <b>Test Mode Control.</b> SM is used during the manufac-<br>turing test and should be tied to Vss.                                                                                                                                                                                                                                                                                                                                 |

| 126           | SE       | I    | <b>Test Mode Control.</b> SE is used during the manufac-<br>turing test and should be tied to VSS.                                                                                                                                                                                                                                                                                                                                 |

| 127           | NC       | —    | No Connect.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 128           | NC       |      | No Connect.                                                                                                                                                                                                                                                                                                                                                                                                                        |

\* Active-low signals within this document are indicated by an N following the symbol names.

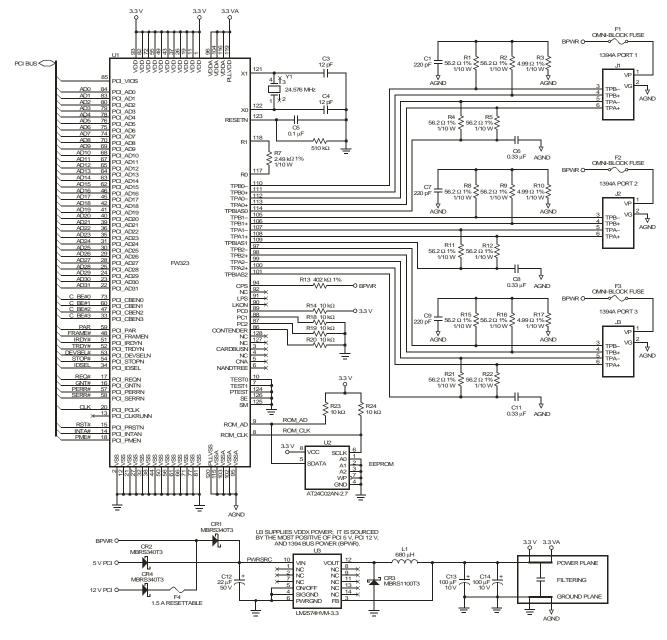

# **Application Schematic**

The application schematic presents a complete three-port, 400 Mbits/s *IEEE* 1394a-2000 design, featuring the Agere FW323 PCI bus-based host OHCI controller and 400 Mbits/s PHY core. The FW323 device needs only a power source (U3), connection to PCI interface, 1394a-2000 terminators and connectors, crystal, and serial EEPROM. No external PHY is required because the FW323 contains both host controller and PHY core functions. This design is a secondary (Class 4) power provider to the 1394 bus, and will participate in the required 1394a-2000 bus activities, even when power on the PCI bus is not energized.

## Application Schematic (continued)

5-8886(f) R.05fm

Figure 4. Application Schematic for the FW323

## **Internal Registers**

This section describes the internal registers in FW323, including both PCI configuration registers and OHCI registers. All registers are detailed in the same format; a brief description for each register, followed by the register offset and a bit table describing the reset state for each register.

A bit description table indicates bit-field names, a detailed field description, and field access tags.

Table 2 describes the field access tags.

#### Table 2. Bit-Field Access Tag Description

| Access Tag | Name   | Description                                                       |  |  |

|------------|--------|-------------------------------------------------------------------|--|--|

| R          | Read   | eld may be read by software.                                      |  |  |

| W          | Write  | Field may be written by software to any value.                    |  |  |

| S          | Set    | ield may be set by a write of 1. Writes of 0 have no effect.      |  |  |

| С          | Clear  | Field may be cleared by a write of 1. Writes of 0 have no effect. |  |  |

| U          | Update | Field may be autonomously updated by the FW323.                   |  |  |

#### **PCI Configuration Registers**

Table 3 illustrates the PCI configuration header that includes both the predefined portion of the configuration space and the user definable registers.

#### Table 3. PCI Configuration Register Map

| Register Name                    |                                                               |                | Offset               |        |

|----------------------------------|---------------------------------------------------------------|----------------|----------------------|--------|

| Devi                             | Device ID Vendor ID                                           |                | 00h                  |        |

| Sta                              | itus                                                          | Com            | mand                 | 04h    |

|                                  | Class Code                                                    | l              | Revision ID          | 08h    |

| BIST                             | Header Type                                                   | Latency Timer  | Cache Line Size      | 0Ch    |

|                                  | OHCI Register                                                 | s Base Address |                      | 10h    |

|                                  | Res                                                           | erved          |                      | 14h    |

|                                  | Res                                                           | erved          |                      | 18h    |

|                                  | Res                                                           | erved          |                      | 1Ch    |

|                                  | 20h                                                           |                |                      |        |