**TOSHIBA** TA8552AFN

TOSHIBA BIPOLAR LINEAR INTEGRATED CIRCUIT SILICON MONOLITHIC

# **TA8552AFN**

#### PLL DATA SYNCHRONIZER FOR DAT STREAMER

The TA8552AFN is PLL DATA SYNCHRONIZER for Digital Audio Tape (DAT) strteamer, Digital Data Storage (DDS).

#### **FEATURES**

- The TA8552AFN incorporates edge detector, data synchronizer, and latch for data separator. Also the TA8552AFN is available to correspond to x1, x2 and x3 of data transfer rates by adjusting external devices.

- The data synchronizer is available to correspond to ±7% variation of data transfer rate.

- By employing full differential signal processing in PLL loop, the TA8552AFN eliminates the influence of external

- Fast & stable locking is realized by switching between the frequency detective mode and the phase detective mode.

- Operating power supply voltage range: 4.5V to 5.5V

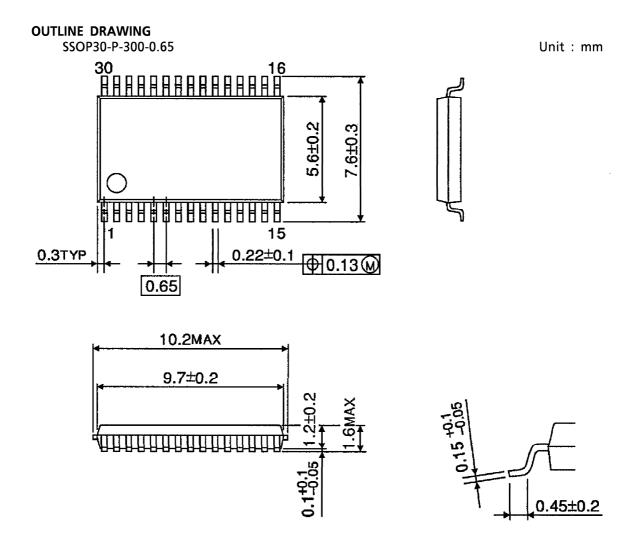

- Small package; SSOP30-P-300-0.65

Handle with care to prevent devices from deterioration by static electricity.

Weight: 0.17g (Typ.)

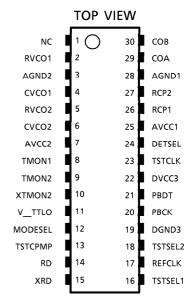

#### PIN CONNECTOION

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

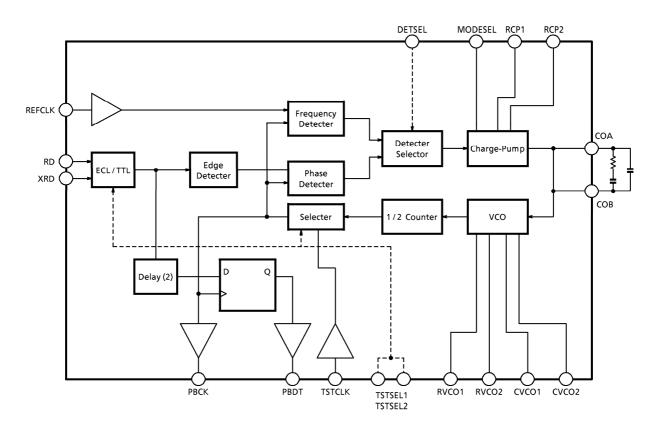

#### **BLOCK DIAGRAM**

## **PIN FUNCTION**

| PIN No. | PIN NAME                                                      | FUNCTION                                                                                                                                      |                     |  |  |

|---------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--|--|

| 1       | NC                                                            | NC terminal. (open at normal use)                                                                                                             | _                   |  |  |

| 2       | RVCO1                                                         | VCO adjusting terminal. Connect an external resistor (R <sub>VCO1</sub> ) between V <sub>CC</sub> .                                           | _                   |  |  |

| 3       | AGND2                                                         | Analog ground for VCO.                                                                                                                        | _                   |  |  |

| 4       | CVCO1                                                         | VCO adjusting terminal. Connect a capacitor (C <sub>VCO</sub> ) between this pin and pin6.                                                    | _                   |  |  |

| 5       | RVCO2                                                         | VCO adjusting terminal. Connect an external resistor (R <sub>VCO2</sub> ) between V <sub>CC</sub> .                                           | _                   |  |  |

| 6       | CVCO2                                                         | VCO adjusting terminal. Connect a capacitor (C <sub>VCO</sub> ) between this pin and pin4.                                                    | _                   |  |  |

| 7       | AVCC2                                                         | analog power supply voltage for VCO.                                                                                                          | _                   |  |  |

| 8       | TMON1                                                         | NC terminal (Open at normal use)                                                                                                              | _                   |  |  |

| 9       | TMON2                                                         | NC terminal (Open at normal use)                                                                                                              | _                   |  |  |

| 10      | XTMON2                                                        | NC terminal (Open at normal use)                                                                                                              | _                   |  |  |

| 11      | V_TTLO                                                        | Input terminal for TTL Voh (high voltage level of pin20, and pin21 output) limitting.                                                         | _                   |  |  |

| 12      | MODESEL                                                       | Input terminal for switching the Normal mode and the Serching mode. (H : Normal mode, L ; Serching mode)                                      |                     |  |  |

| 13      | TSTCPMP                                                       | NC terminal. (Open at normal use.)                                                                                                            | _                   |  |  |

| 14      | RD                                                            | Input terminal of Data (Normal phase)                                                                                                         | ECL-in or<br>TTL-in |  |  |

| 15      | XRD                                                           | Input terminal of Data (Reverse phase).  (This terminal is active when TSTSEL1 = L and TSTSEL2 = H.  Otherelse, short with V <sub>CC</sub> .) | (ECL-in)            |  |  |

| 16      | TSTSEL1                                                       | Input terminal for Test Mode selecting. (Refer the chapter of "Test Mode")                                                                    | _                   |  |  |

| 17      | REFCLK                                                        | Reference clock input of frequency synchronizer.                                                                                              | TTL-in              |  |  |

| 18      | TSTSEL2                                                       | Input terminal for Test Mode selecting. (Refer the chapter of "Test Mode")                                                                    | _                   |  |  |

| 19      | DGND3                                                         | Digital ground for TTL output.                                                                                                                | _                   |  |  |

| 20      | PBCK                                                          | Output terminal of Data Latch Clock.                                                                                                          | TTL-out             |  |  |

| 21      | PBDT                                                          | Output terminal of Data Latch.                                                                                                                | TTL-out             |  |  |

| 22      | DVCC3                                                         | Digital power supply voltage for TTL output.                                                                                                  | _                   |  |  |

| 23      | TSTCLK                                                        | Input terminal of $x1/2$ vco test clock. (Short with $V_{CC}$ at mormal use.)                                                                 | _                   |  |  |

| 24      | Input terminal for switching the frequency detective mode and |                                                                                                                                               | TTL-in              |  |  |

| 25      | AVCC1                                                         | Analog power supply voltage.                                                                                                                  | _                   |  |  |

| PIN No.     | PIN NAME | FUNCTION                                                                                                         | IN/OUT |

|-------------|----------|------------------------------------------------------------------------------------------------------------------|--------|

| 26          | RCP1     | Adjusting terminal of Charge pump at normal mode.  Connect an external resistor (R <sub>cp1</sub> ) between GND. | -      |

| 27          | RCP2     | Adjusting terminal of Charge pump at normal mode.  Connect an external resistor (R <sub>cp2</sub> ) between GND. | _      |

| 28          | AGND1    | Analog ground                                                                                                    | _      |

| 29          | СОА      | Connecting terminal of loop filter. Connect an external loop filter between this pin and 30pin.                  | _      |

| 1 30 1(OR 1 |          | Connecting terminal of loop filter. Connect an external loop filter between this pin and 29pin.                  | -      |

## **ABSOLUTE MAXIMUM RATING** ( $Ta = 27^{\circ}C$ )

| PARAMETER           | SYMBOL           | RATING                    | UNIT |

|---------------------|------------------|---------------------------|------|

| Supply Voltage      | AVCC             | 7                         | V    |

| Input Voltage       | V <sub>IN</sub>  | -0.3~V <sub>CC</sub> +0.3 | V    |

| Output Voltage      | Vout             | -0.3~V <sub>CC</sub> +0.3 | V    |

| Storage Temperature | T <sub>stg</sub> | <b>- 55∼150</b>           | °C   |

## **RECOMMENDED OPERATING CONDITION**

| PARAMETER             | SYMBOL           | CONDITION | MIN.       | TYP. | MAX. | UNIT |

|-----------------------|------------------|-----------|------------|------|------|------|

| Supply Voltage        | AVCC             | _         | 4.5        | 5    | 5.5  | V    |

| Operation Temperature | T <sub>opr</sub> | _         | <b>–</b> 5 | _    | 75   | °C   |

## **POWER** SUPPLY (Unless otherwise specified, $Ta = 27^{\circ}C$ , $V_{CC} = 5.0V$ )

| PARAMETER      | SYMBOL | CONDITION                                          | MIN. | TYP. | MAX. | UNIT |

|----------------|--------|----------------------------------------------------|------|------|------|------|

| Supply Current | IPLCC  | TSTSEL1 = H, TSTSEL2 = L<br>DETSEL = L, MODSEL = H |      |      | 65   | mA   |

## **ELECTRICAL CHARACTERISTIC** (Unless otherwise specified, $Ta = 27^{\circ}C$ , $V_{CC} = 5.0V$ )

| PARAMETER                             | SYMBOL          | TEST<br>CIR-<br>CUIT | TEST CONDITION                                 | MIN.                     | TYP. | MAX.                     | UNIT |

|---------------------------------------|-----------------|----------------------|------------------------------------------------|--------------------------|------|--------------------------|------|

| High Level<br>Input Voltage (1)       | V <sub>IH</sub> | _                    | TTL input pins                                 | 2.0                      | _    | _                        | V    |

| Low Level<br>Input Voltage (1)        | V <sub>IL</sub> | _                    | TTL input pins                                 | _                        | _    | 0.4                      | ٧    |

| High Level<br>Input Current (1)       | lіН             | _                    | TTL input pins                                 | _                        | _    | 20                       | μΑ   |

| Low Level<br>Input Current (1)        | I <sub>IL</sub> | _                    | TTL input pins                                 | _                        | _    | - 360                    | μΑ   |

| High Level<br>Input Voltage (2)       | VIHE            | _                    | ECL input pins                                 | V <sub>CC</sub><br>– 1.0 | _    | _                        | V    |

| Low Level<br>Input Voltage (2)        | VILE            | _                    | ECL input pins                                 | _                        | _    | V <sub>CC</sub><br>– 1.5 | ٧    |

| High Level<br>Input Current (2)       | IIHE            | _                    | ECL input pins                                 | _                        | _    | 2.0                      | mA   |

| Low Level<br>Input Current (2)        | IILE            | _                    | ECL input pins                                 | _                        | _    | 1.6                      | mA   |

| High Level<br>output Voltage (1)      | VOH             | _                    | TTL output pins $I_{OH} = 400 \mu A$           | VTTLO<br>-0.2            |      | VTTLO<br>+ 0.2           | V    |

| Low Level<br>Output Voltage (1)       | V <sub>OL</sub> | _                    | TTL output pins IOL = 4mA                      | _                        | _    | 1.0                      | V    |

| Output Rise Time (1)                  | TOR             | _                    | TTL output pins 1.5V to 3.5V $C_L \le 30pF$ *1 | _                        | _    | 5                        | ns   |

| Output Fall Time (1)                  | TOF             | _                    | TTL output pins 3.5V to 1.5V $C_L \le 30pF$ *1 | _                        | _    | 5                        | ns   |

| Input Voltage Range to VTTLO terminal | VTTLO           | _                    |                                                | 2.7                      |      | 3.3                      | V    |

<sup>\*1 ;</sup> Design guaranteed value.

## CHARGE PUMP (Unless otherwise specified, $Ta = 27^{\circ}C$ , $V_{CC} = 5.0V$ )

| PARAMETER          | SYMBOL            | TEST<br>CIR-<br>CUIT | CONDITION               | MIN.  | TYP. | MAX.  | UNIT    |

|--------------------|-------------------|----------------------|-------------------------|-------|------|-------|---------|

| Range of Output    | les               |                      | At normal mode *1       | 30    |      | _     |         |

| current setting    | ICP               | _                    | At serching mode *2     | _     | _    | 800   | $\mu$ A |

| Accuracy of Output |                   | _                    | At normal mode          | - 6   | _    | + 6   | %       |

| Current Setting    | tting lacu        |                      | At serching mode        | -8    | _    | +8    | 70      |

| Leak Current       | 1 .               |                      | Between COA pin and COB | - 3.5 |      | + 3.5 | μΑ      |

| Leak Cullett       | <sup>I</sup> reak |                      | pin, at high impedance  | - 3.3 |      | + 3.5 | $\mu$ A |

<sup>\*1 ;</sup> Output current is set by an external resistor ( $R_{cp1}$ ), as following ;  $2 \times 1.3 / R_{cp1} =$  (Output current at normal mode).

<sup>\*2 ;</sup> Output current is set by external resisters ( $R_{cp1}$ ,  $R_{cp2}$ ), as following ;  $2 \times 1.3 / R_{cp1} + 8 \times 1.3 / R_{cp2} =$  (Output current at search mode). (Note) The above values are all at open loop.

VCO (Unless otherwise specified,  $Ta = 27^{\circ}C$ ,  $V_{CC} = 5.0V$ )

| PARAMETER                            | SYMBOL           | TEST<br>CIR-<br>CUIT | CONDITION                                                                                                           |    | MIN. | TYP. | MAX. | UNIT    |

|--------------------------------------|------------------|----------------------|---------------------------------------------------------------------------------------------------------------------|----|------|------|------|---------|

| Input Voltage of VCO<br>(V(COB–COA)) | Vvco             | _                    | $R_{VCO1} = 3.75 k\Omega$<br>$R_{VCO2} = 1.21 k\Omega$<br>$C_{VCO} = 39 pF$<br>$f_{VCO} = 28.224 MHz$               | *1 | 0.25 |      | 0.45 | \<br>\  |

| Upper Limitation of VCO Frequency    | f <sub>max</sub> | _                    | $R_{VCO1} = 3.75 k\Omega$ $R_{VCO2} = 1.21 k\Omega$ $C_{VCO} = 39 pF$ $V (COB-COA) = 0.6 V$                         | *1 | 29.5 |      |      | MHz     |

| Lower Limitation of<br>VCO Frequency | f <sub>min</sub> | _                    | $R_{VCO1} = 3.75 k\Omega$<br>$R_{VCO2} = 1.21 k\Omega$<br>$C_{VCO} = 39 pF$<br>V (COB-COA) = -0.6V                  | *1 |      |      | 23.5 | MHz     |

| Control Gain (F/V)                   | G <sub>VCO</sub> | _                    | $R_{VCO1} = 3.75 k\Omega$ $R_{VCO2} = 1.21 k\Omega$ $C_{VCO} = 39 pF$ $Voltage (COB-COA)$ $Excursion 0.3V to -0.3V$ | *1 | 6    |      | 7.7  | MHz / V |

| VCO Jitter                           | <sup>t</sup> jit | _                    | PBCK pin<br>at ×3 transfer rate                                                                                     | *2 |      | 300  |      | ps      |

$<sup>^{*}</sup>$ 1; CVCO inclides the package capacitance.

(Note) The above values are all at open loop, measured at the PBCK pin

CLOSED LOOP (Unless otherwise specified, Ta = 27°C, V<sub>CC</sub> = 5.0V)

| PARAMETER                    | SYMBOL             | TEST<br>CIR-<br>CUIT | CONDITION                     | MIN. | TYP. | MAX. | UNIT |

|------------------------------|--------------------|----------------------|-------------------------------|------|------|------|------|

| VCO Jitter in Closed<br>Loop | <sup>t</sup> jit2N | _                    | In search mode lock to REFCLK |      |      | 0.5  | ns   |

| VCO Jitter in Closed<br>Loop | <sup>t</sup> jit2S | _                    | In normal mode lock to RD     |      |      | 0.4  | ns   |

Values of external parts are  $(R_{VCO1}=3.75k\Omega,\ R_{VCO2}=1.21k\Omega,\ C_{VCO}=39pF$  (Including storage capacitor),  $R_{CP1}=8.25k,\ R_{CP2}=30.1k$ ).

<sup>\*2;</sup> Design guaranteed value.

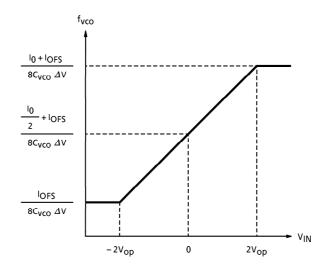

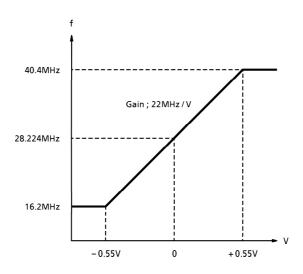

#### **CHARACTER OF VCO**

The connection of input voltage and output frequency of VCO (measured at PBCK after the 1/2 frequency counter) is written as following;

$$f_{\text{VCO}} = \begin{cases} \frac{1}{8 \cdot C_{\text{VCO}} \cdot \Delta V} \cdot (I_{\text{O}} + I_{\text{Ofs}}) & (V_{\text{in}} > 2V_{\text{op}}) \\ \frac{1}{8 \cdot C_{\text{VCO}} \cdot \Delta V} \cdot (\frac{I_{\text{O}}}{4V_{\text{op}}} \cdot V_{\text{in}} + \frac{I_{\text{O}}}{2} + I_{\text{Ofs}}) & (2V_{\text{op}} > V_{\text{in}} > -2V_{\text{op}}) \\ \frac{1}{8 \cdot C_{\text{VCO}} \cdot \Delta V} \cdot I_{\text{Ofs}} & (V_{\text{in}} < -2V_{\text{op}}) \end{cases}$$

Where ;  $C_{VCO}$  is an external capacitor between 4pin and 6pin,  $\Delta V = 0.35V$ ,  $V_{Op} = 0.275V$ ,  $V_{in}$  is the input voltage of VCO (differential),  $I_{O} = 3 \times 1.3 / R_{VCO} = 1.3 / R$

So, the gain of VCO is defined as following (at PBCK);

$$\frac{1}{8 \cdot \mathsf{C}_{\mathsf{VCO}} \cdot \Delta \mathsf{V}} \cdot \frac{\mathsf{I}_{\mathsf{O}}}{4 \mathsf{V}_{\mathsf{O}\mathsf{D}}}$$

And, Upper limitation f upper, and Lower limitation of VCO frequency f lower is defined as follows;

$$f_{upper} = (I_O + I_{ofs}) / 8C_{vco} \Delta V$$

$$f_{lower} = I_{ofs} / 8C_{vco} \Delta V$$

I 0 can be determined by selecting  $R_{VCO\,1}$ , and I ofs can by  $R_{VCO\,2}$ . So, you can independently determine the gain of VCO, upper limitation and lower limitation of VCO frequency by selecting  $C_{VCO}$ ,  $R_{VCO\,1}$ , and  $R_{VCO\,2}$ .

[ Example ] When,  $C_{vco} = 22.1 pF$ ,  $R_{vco1} = 2.6 k\Omega$ ,  $R_{vco2} = 2.6 k\Omega$ ,

Gain of VCO ;

$$\frac{1.3/(2.6 \times 10^3) \times 3}{8 \times 22.1 \times 10^{-12} \times 0.35 \times 4 \times 0.275} = 22MHz/V$$

Upper limitation of VCO frequency;

$$\frac{1.3/(2.6 \times 10^3) \times 3 + 1.3/(2.6 \times 10^3) \times 2}{8 \times 22.1 \times 10^{-12} \times 0.35} = 40.4 \text{MHz}$$

Lower limitation of VCO frequency;

$$\frac{1.3/(2.6 \times 10^3) \times 2}{8 \times 22.1 \times 10^{-12} \times 0.35} = 16.2 \text{MHz}$$

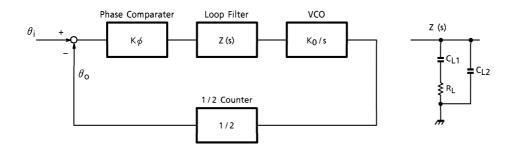

#### **FUNCTION DESCRIPTION:**

The angular frequency ( $\omega_n$ ) and dumping factor ( $\zeta$ ) are adjusted by external devices. The setting procedure is shown as following.

The setting conditions to lock PLL inside a constant time;

• Data transfer rate : 28.224Mbps (f<sub>M</sub> = 28.224MHz)

• The capturing signal of PLL : The rectangle wave of 14.112MHz (Data pattern is 101010...),

The term of this data is continuous 180 bits.

• The capturing time of PLL :  $1/(14.114 \times 10^6) \times 180 = 12.75 \times 10^{-6}$ s

$12.75 \times 10^{-6} \times 0.9 = 11.5 \mu s$  (This 0.9 is a factor of margin.)

[ The transfer function of PLL ]

The transfer function (F (S)), the angular frequency ( $\omega_n$ ), and the dumping factor ( $\zeta$ ) of the above composition are defined as following (However  $C_{L2}$  is ignored as  $C_{L2} \ll C_{L1}$ ):

$$\omega_{\rm n} = (\frac{\rm K}{\rm C_{\rm L1}}) 1/2$$

$$\zeta = \frac{R_L C_{L1} \omega_n}{2}$$

[ Calculation of  $\zeta$  ]

The dumping factor ( $\zeta$ ) is set to 0.7 as the most stable response characteristic. Besides  $\omega_n$  t is assumed to set as 6.

[ Calculation of  $\omega_n$  ]

The capturing time of PLL is expected as above 11.5 $\mu$ s. Therefore ( $\omega_n$ ) is determinated as the following :

$$\omega_n = 6 / (11.5 \times 10^{-6}) = 552 \text{krad/s}$$

[ Calculation of K<sub>0</sub> (VCO control gain)]

$K_0$  is determined as the following;

$$K_0 = 40MHz / V = 251.3Mrad / V$$

[ Calculation of  $K\phi$  (phase detector gain) ]

$K\phi$  is estimated as the following (The current of charge pump is set as  $\pm 50\mu A$ .)

$$K\phi = \frac{1}{2} \cdot \frac{1}{2\pi} \times 50 \times 10^{-6} = 3.98 \times 10^{-6}$$

(A / rad)

The current of charge pump (lchp) is set by an external resister ( $R_{cp1}$ ), connected with  $R_{cp1}$  (26pin). When "H" level voltage inputs to MODESEL (12pin), lchp is set as the following :

$$I_{chp} = 2 \times 1.3 / R_{CP1} \rightarrow R_{CP1} = 2 \times 1.3 / I_{chp} = 2 \times 1.3 / 50 \times 10^{-6} = 52 \times 10^{3} \Omega$$

Therefore, when  $R_{CP1}$  is  $52k\Omega$ ,  $I_{chp}$  is set as  $\pm 50 \mu A$

[ Calculation of external devices of loop-filter ]

$$C_{L1} = \frac{K\phi \times K_0}{2\omega_n} = \frac{3.98 \times 10^{-6} \times 251.3 \times 10^6}{2 \times (522 \times 10^3)^2} = 1800 \times 10^{-6} F$$

$$R_{L} = \frac{2\zeta}{C_{L1} \omega_{n}} = \frac{2 \times 0.7}{1800 \times 10^{-12} \times 522 \times 10^{3}} = 1.5 \times 10^{3} \Omega$$

$$C_{L2} = C_{L1} / 10 = 180 pF$$

#### **MODESEL SWITCHING FUNCTION**

The TA8552AFN has a function to correspond with the high-speed serching mode of DAT streamer. In the searching mode, the data transfer rate will shift with small percentage error. The TA8552AFN is available to solve this problem by extending the lock-in-range ( $\Delta\omega_L$ ). In the serching mode the current of charge pump will be increased to raise the phase detecter gain, then the lock-in-range ( $\Delta\omega_L$ ) will extend.

This function is selected by MODESEL (12pin).

(H: normal mode/L: searching mode)

[ Calculation of the charge pump's current in the searching mode ]

The charge pump's current in the searching mode is estimated as the following (The shift rateX of data, transfer is assumed as X = 7% in this example);

$$I_{chp} = \frac{f_{M} \times X \times 2\pi}{R \times K_{0}} \times 8\pi = \frac{28.224 \times 10^{6} \times 0.07 \times 2 \times 3.14}{1.5 \times 10^{3} \times 251.3 \times 10^{6}} \times 8 \times 3.14 = 830 \times 10^{-6} \text{ (A)}$$

When "L" level voltage inputs to MODESEL (12pin), the charge pump's current (Ichp) increases. In the normal mode, the charge pump's current ( $I_{cp1}$ ) is set by an external resister ( $R_{cp1}$ ). And in the searching mode, another current ( $I_{cp2}$ ), is set by an external resister ( $R_{cp2}$ ), adds to Icp1. This ( $R_{cp2}$ ) is the resister to be connected with RCP2 (27pin).

The additional current (I<sub>CD2</sub>) is determined by the following :

$$I_{cp2} = 8 \times 1.3 / R_{cp2}$$

Therefore, R<sub>cp2</sub> is estimated as the following :

$$R_{cp2} = \frac{8 \times 1.3}{830 \times 10^{-6} - 50 \times 10^{-6}} = 13.3 \times 10^{3} \Omega$$

MODESEL FUNCTION is summarized by the followings

| MODE                        | NORMAL<br>MODE           | HIGH-SPEED SEARCHING<br>MODE                      |

|-----------------------------|--------------------------|---------------------------------------------------|

| MODESEL (12pin)             | Н                        | L                                                 |

| Charge pump current<br>Ichp | I <sub>cp1</sub>         | l <sub>cp1</sub> + l <sub>cp2</sub>               |

| Setting definition          | $2 \times 1.3 / R_{cp1}$ | $2 \times 1.3 / R_{cp1} + 8 \times 1.3 / R_{cp2}$ |

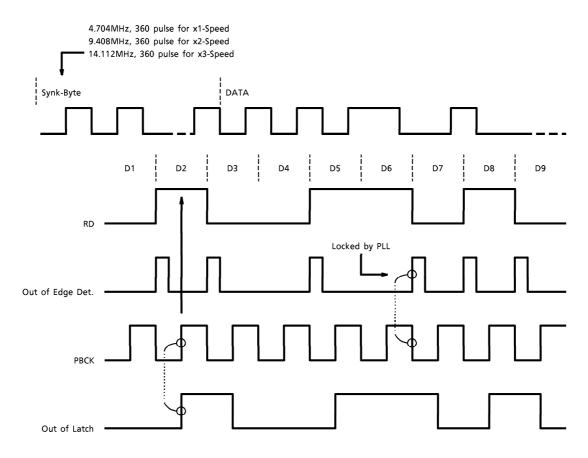

## TIMING CHART OF LATCH

## (Note) TEST MONITOR OUTPUT TERMINAL

| TST | SEL | DATAINPUT                                 | FUNCTION                                                                                                          |

|-----|-----|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 1   | 2   | DATAINPUT                                 | FUNCTION                                                                                                          |

| L   | L   | TTL input from 14pin (RD)                 | _                                                                                                                 |

| Н   | L   | TTL input from 14pin (RD)                 | PBCK (20pin) & PBDT (21pin) becomes disable                                                                       |

| L   | Н   | ECL input from 14pin (RD) and 15pin (XRD) | _                                                                                                                 |

| Н   | Н   | TTL input from 14pin (RD)                 | The internal PLL becomes disable, and the external clock from TSTCLK (23pin) becomes enable as input data signal. |

- (Note) We commend the use of this IC under the comdition of ECL input from 14pin (RD) and 15pin (XRD) when (TSTSEL1, TSTSEL2) = (L, H)

- It is possible of the use of TTL input from 14pin (RD) when (TSTSEL1, TSTSEL2) = (L, L)

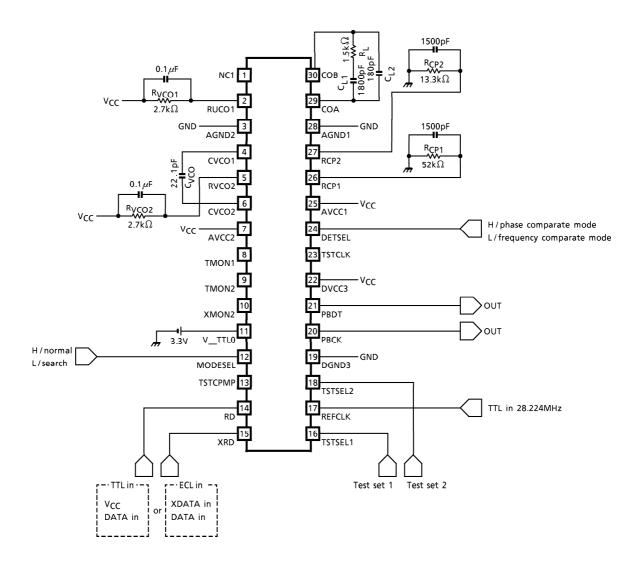

#### **APPLICATION DIAGRAM**

When the data transfer rate is 28.224Mbps, the application diagram is shown below.

Weight: 0.17g (Typ.)