# MOS INTEGRATED CIRCUIT $\mu PD4990A$

# SERIAL I/O CALENDAR & CLOCK CMOS LSI

The  $\mu$ PD4990A is a CMOS LSI developed to input/output calendar & clock data serially to/from the micro computer. The crystal frequency is 32.768 kHz and the data items included are time, minute, second, year, month, day, and week.

#### **FEATURES**

- Built-in counters for time (hour, minute, and second) and date (year, month, day, and week)

- · Leap years are adjusted automatically.

- Data is represented in BCD notation (except months in hexadecimal notation) and input/output serially.

- · Commands can be set by inputting serial data.

- Selective timing pulses (TPs) are 64 Hz, 256 Hz, 2 048 Hz, and 4 096 Hz and selective output intervals are 1, 10, 30, and 60 seconds.

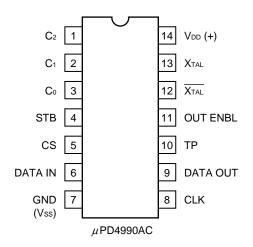

#### ORDERING INFORMATION

| PART No.  | PACKAGE                      |

|-----------|------------------------------|

| μPD4990AC | 14-pin plastic DIP (300 mil) |

| μPD4990AG | 16-pin plastic SOP (300 mil) |

#### **CONNECTION DIAGRAM (Top View)**

NC: NO CONNECTION

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage              | $V_{DD}-V_{SS}$ | −0.5 to 7.0              | V  |

|-----------------------------|-----------------|--------------------------|----|

| Input Voltage               | Vin             | Vss $-0.3$ to Vpp $+0.3$ | V  |

| Operating Temperature Range | Topt            | -40 to +85               | °C |

| Storage Temperature Range   | Tstg            | -65 to +125              | °C |

| Output Terminal Voltage     | Vouт            | -0.5 to 7.0              | V  |

# ELECTRICAL CHARACTERISTICS (f = 32.768 kHz, Cg = CD = 20 pF, Cl = 20 k $\Omega$ , Ta = 25 °C)

| CHARACTERISTIC           | SYMBOL                            | MIN.                | TYP. | MAX.                | UNIT | TEST CONDITIONS                                      |

|--------------------------|-----------------------------------|---------------------|------|---------------------|------|------------------------------------------------------|

| Operating Voltage        | V <sub>DD</sub> - V <sub>SS</sub> | 2.00                |      | 5.50                | V    |                                                      |

| Current Consumption      | 1                                 |                     | 8    | 20                  | μΑ   | V <sub>DD</sub> - V <sub>SS</sub> = 3.60 V           |

| Current Consumption      | IDD                               |                     |      | 100                 | μΑ   | V <sub>DD</sub> - V <sub>SS</sub> = 5.50 V           |

| Low Level Output Voltage | Vol                               |                     |      | 0.4*                | V    | V <sub>DD</sub> – V <sub>SS</sub> = 2.0 to 5.5 V     |

| Low Level Output Voltage |                                   |                     |      |                     |      | IoL = 500 μA                                         |

| CLK Input Frequency      | fclk                              | DC                  |      | 500                 | kHz  | V <sub>DD</sub> - V <sub>SS</sub> = 2.0 V, Duty 50 % |

| Input Leakage Current    | lin                               |                     |      | ±1                  | μΑ   | V <sub>DD</sub> - V <sub>SS</sub> = 5.50 V           |

| High Level Input Voltage | Vıн                               | 0.7 V <sub>DD</sub> |      | V <sub>DD</sub>     | V    |                                                      |

| Low Level Input Voltage  | VIL                               | Vss                 |      | 0.3 V <sub>DD</sub> | V    |                                                      |

<sup>\*</sup> TP and DATA OUT are N-channel open drain output.

# A.C. ELECTRICAL CHARACTERISTICS (f = 32.768 kHz, VDD - Vss = 2.0 V, Ta = 25 °C)

| CHARACTERISTIC                             | SYMBOL              | MIN. | TYP. | MAX. | UNIT | TEST CONDITIONS              |

|--------------------------------------------|---------------------|------|------|------|------|------------------------------|

| C <sub>0 to 2</sub> , CS – STB Set-up Time | <b>t</b> su         | 1    |      |      | μs   |                              |

| STB Pulse Width                            | tsтв                | 1    |      |      | μs   |                              |

| C <sub>0 to 2</sub> , CS – STB Hold Time   | <b>t</b> HLD        | 1    |      |      | μs   |                              |

| STB LATCH Delay Time                       | t <sub>d1</sub>     |      |      | 1**  | μs   | except Time Read mode        |

| CLK-DATA OUT Delay time                    | t <sub>d(c-o)</sub> |      |      | 1    | μs   | $R_L$ = 33 kΩ, $C_L$ = 15 pF |

| DATA IN Set-up Time                        | <b>t</b> osu        | 1    |      |      | μs   |                              |

| DATA IN Hold Time                          | <b>t</b> DHLD       | 1    |      |      | μs   |                              |

<sup>\*\*</sup> **Note:** When a function mode is Time Read mode (other than Test mode), STB LATCH delay time is 20  $\mu$ s MAX. (t<sub>d2</sub>).

#### **FUNCTION SPECIFICATIONS**

- Crystal frequency (X tal osc.).

- o 32.768 kHz

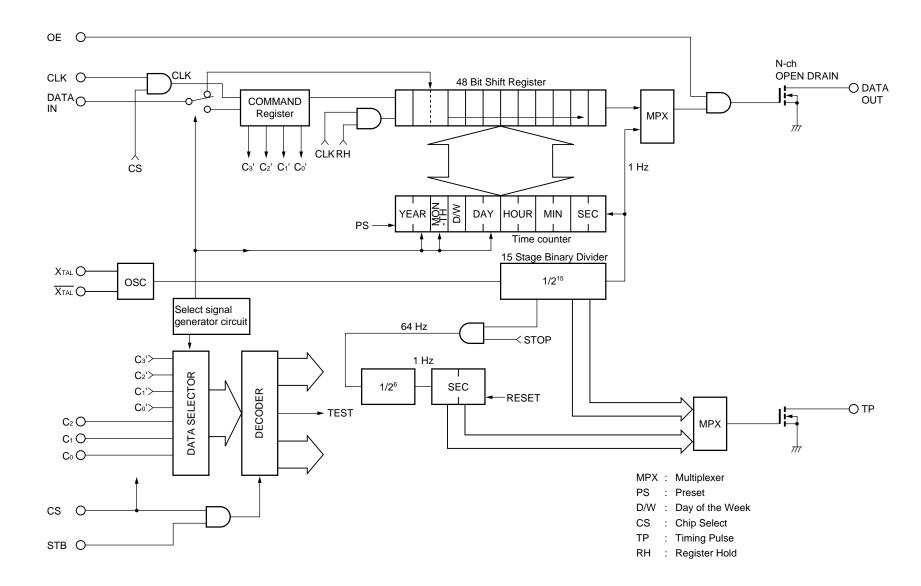

#### Data

Data types are: second, minute, day, week, month, and year.

Leap years, 31-day months, and months with 30 or less days are adjusted automatically.

A 24-hour system is used and last two digits of Gregorian year are indicated.

It is assumed that leap years are expressed by multiples of 4.

#### Data format

Data is represented in BCD notation. Only months are represented in hexadecimal notation.

#### Data input-output and Clock

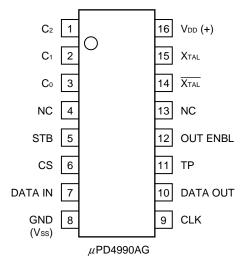

Data is input/output synchronously with reference to the external clocks input from the CLK pin using the serial input/output system. (See Fig. 1.)

#### • Timing pulse output

Three frequencies, 64 Hz, 256 Hz, and 2 048 Hz, can be set with C<sub>0</sub>, C<sub>1</sub> and C<sub>2</sub> pins.

Using serial data input command, selective timing pulses (TPs) are 64 Hz, 256 Hz, 2 048 Hz, and 4 096 Hz and selective output intervals are 1, 10, 30, and 60 seconds.

#### Function mode selection

A function mode can be selected by the inputs from  $C_0$ ,  $C_1$ , and  $C_2$ . Also a function mode can be selected through serial data input. ( $C_0 = C_1 = C_2 = V_{DD}$ )

Each command is latched with STB (strobe).

#### Chip select

Connecting the CS pin to the ground level inhibits CLK and STB inputs.

#### • Data output inhibition

Connecting the OUT ENBL pin to the ground level sets the DATA OUT pin at high impedance.

Figure 1.

52 Bit Shift Register

<sup>\*</sup> DATA of 52 Bit Shift Register appears on DATA OUT terminal from LSB of second.

#### **TERMINALS**

• Input terminals

DATA IN Data input of 40-/52-bit shift register

CLK Shift clock input of 40-/52-bit shift register

o Co, C1, C2 Command input (3 bit)

• STB Strobe input

• CS Chip select input (Prohibits CLK & STB)

o OUT ENBL Output control input (Makes the DATA OUT high impedance by inputting low level).

• Output terminals (N-channel Open Drain)

o DATA OUT Data output of 40-/52-bit shift register

• TP Timing pulse output

• Oscillation terminals

XTAL Oscillation inverter input (OSC IN)

XTAL Oscillation inverter output (OSC OUT)

Power supply terminals

VDD Plus power supplyGND (Vss) Common line

#### **COMMAND SPECIFICATIONS**

Commands input from C<sub>0</sub>, C<sub>1</sub>, and C<sub>2</sub> pins (1 ...H, 0 ...L)

Shift register 40 bit (The year function is ineffective.)

(Operates as the existing μPD1990AC in other than test mode)

| C <sub>2</sub> | C <sub>1</sub> | Co |                            | FUNCTION                  |

|----------------|----------------|----|----------------------------|---------------------------|

| 0              | 0              | 0  | Register Hold              | DATA OUT = 1 Hz           |

| 0              | 0              | 1  | Register Shift             | DATA OUT = [LSB] = 0 or 1 |

| 0              | 1              | 0  | Time Set & Counter Hold    | DATA OUT = [LSB] = 0 or 1 |

| 0              | 1              | 1  | Time Read                  | DATA OUT = 1 Hz           |

| 1              | 0              | 0  | TP = 64 Hz                 |                           |

| 1              | 0              | 1  | TP = 256 Hz                |                           |

| 1              | 1              | 0  | TP = 2 048 Hz              |                           |

| 1              | 1              | 1  | Serial command transfer mo | de                        |

<sup>\*</sup> The test mode is cancelled by [C2, C1, C0] = [0, 0, 0] to [1, 1, 0].

o Serial data commands

Set  $[C_2, C_1, C_0] = [1, 1, 1]$  at all time.

Shift register 52 bit (The year function is effective.)

| Сз' | C <sub>2</sub> ' | C <sub>1</sub> ' | Co' | FU                                             | INCTION                   |  |  |  |

|-----|------------------|------------------|-----|------------------------------------------------|---------------------------|--|--|--|

| 0   | 0                | 0                | 0   | Register Hold                                  | DATA OUT = 1 Hz           |  |  |  |

| 0   | 0                | 0                | 1   | Register Shift                                 | DATA OUT = [LSB] = 0 or 1 |  |  |  |

| 0   | 0                | 1                | 0   | Time Set & Counter Hold                        | DATA OUT = [LSB] = 0 or 1 |  |  |  |

| 0   | 0                | 1                | 1   | Time Read                                      | DATA OUT = 1 Hz           |  |  |  |

| 0   | 1                | 0                | 0   | TP = 64 Hz                                     |                           |  |  |  |

| 0   | 1                | 0                | 1   | TP = 256 Hz                                    |                           |  |  |  |

| 0   | 1                | 1                | 0   | TP = 2 048 Hz                                  | TP = 2 048 Hz             |  |  |  |

| 0   | 1                | 1                | 1   | TP = 4 096 Hz                                  |                           |  |  |  |

| 1   | 0                | 0                | 0   | TP = 1 s interval set (counter reset & start)  |                           |  |  |  |

| 1   | 0                | 0                | 1   | TP = 10 s interval set (counter reset & start) |                           |  |  |  |

| 1   | 0                | 1                | 0   | TP = 30 s interval set (counter reset & start) |                           |  |  |  |

| 1   | 0                | 1                | 1   | TP = 60 s interval set (counter reset & start) |                           |  |  |  |

| 1   | 1                | 0                | 0   | Interval Output Flag Reset                     |                           |  |  |  |

| 1   | 1                | 0                | 1   | Interval Timer Clock Run                       |                           |  |  |  |

| 1   | 1                | 1                | 0   | Interval Timer Clock Stop                      |                           |  |  |  |

| 1   | 1                | 1                | 1   | TEST MODE SET                                  |                           |  |  |  |

When serial data commands are used,  $C_0$ ,  $C_1$ , and  $C_2$  pins should be connected  $V_{DD}$  pin.

- Command input

- (1) 3-bit binary code input: C2, C1, C0

- (2) 4-bit serial transfer command input: C3', C2', C1', C0'

- Number of commands

|                  | C <sub>2</sub> , C <sub>1</sub> , C <sub>0</sub> | C'3, C'2, C'1, C'0 |

|------------------|--------------------------------------------------|--------------------|

| Register control | 4                                                | 4                  |

| TP select        | 3                                                | 8                  |

| TP control       | 0                                                | 3                  |

| Test mode set    | 1                                                | 1                  |

- Commands (C<sub>3</sub>', C<sub>2</sub>', C<sub>1</sub>', C<sub>0</sub>' commands are made effective only when [C<sub>2</sub>, C<sub>1</sub>, C<sub>0</sub>] = [1, 1, 1].)

- (1) Register control

• Register Hold Mode

[0, 0, 0] / [0, 0, 0, 0]

[C<sub>2</sub>, C<sub>1</sub>, C<sub>0</sub>]

The 40-bit shift register is held. The year function is ineffective.

The 48-bit shift register is held.

The command register is not held.

- \* The DATA OUT output frequency is 1 Hz.

- o Register Shift Mode

[C<sub>2</sub>, C<sub>1</sub>, C<sub>0</sub>]

The 40-bit shift register data can be shifted. The year function is ineffective.

Data in 52-bit shift registers (including command registers) can be shifted. For command register, data can be always shifted using the serial command transfer mode.

- \* The DATA OUT output is LSB data from the shift register.

- o Time Set and Counter Hold Mode

[C<sub>2</sub>, C<sub>1</sub>, C<sub>0</sub>]

Data is transferred from the 40-bit shift register to the time counter. The year function is ineffective.

[C<sub>3</sub>', C<sub>2</sub>', C<sub>1</sub>', C<sub>0</sub>']

Data is transferred from the 48-bit shift register to the time counter.

- \* This command is used to reset the last 10-15 of 15 Stage Binary Divider and holds the time counter.

- 15 Stage Binary Divider resetting and time counter release are executed by the following:

$$[C2, C1, C0] = [0, 0, 0] [0, 0, 1] [0, 1, 1] [C3', C2', C1', C0'] = [0, 0, 0, 0] [0, 0, 0, 1] [0, 0, 1, 1]$$

The time setting accuracy is  $\pm 15.625$  ms.

The DATA OUT pin outputs LSB data (0 or 1) from the shift register.

After this command is executed, the 40-/48-bit shift register is held and data cannot be shifted.

• Time Read Mode [0, 1,

[C<sub>2</sub>, C<sub>1</sub>, C<sub>0</sub>]

Data is transferred from the time-counter to the 40-bit shift register. The year function is ineffective.

Data is transferred from the time counter to the 48-bit shift register.

\* The DATA OUT pin output is a 1 Hz frequency.

After this command is executed, the 40-/48-bit shift register is held and data cannot be shifted.

- (2) TP selection and control [C<sub>2</sub>, C<sub>1</sub>, C<sub>0</sub>] / [C<sub>3</sub>', C<sub>2</sub>', C<sub>1</sub>', C<sub>0</sub>']

- **TP = 64 Hz** Set Mode [1, 0, 0] / [0, 1, 0, 0]

64 Hz (50 % duty) is output to the TP pin.

[C2, C1, C0]: The year function is ineffective and the interval timer stops.

• <u>TP = 256 Hz</u> Set Mode [1, 0, 1] / [0, 1, 0, 1]

256 Hz (50 % duty) is output to the TP pin.

[C2, C1, C0]: The year function is ineffective and the interval timer stops.

• <u>TP = 2 048 Hz</u> Set Mode [1, 1, 0] / [0, 1, 1, 0]

2 048 Hz (50 % duty) is output to the TP pin.

[C<sub>2</sub>, C<sub>1</sub>, C<sub>0</sub>]: The year function is ineffective and the interval timer stops.

Modes permitted only for serial commands [C<sub>3</sub>', C<sub>2</sub>', C<sub>1</sub>', C<sub>0</sub>']

• TP = 4 098 Hz Set Mode [0, 1, 1, 1]

4 098 Hz (50 % duty) is output to the TP pin. The interval timer stops.

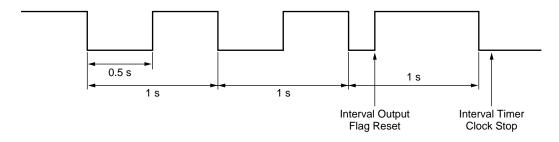

• <u>TP = 1-second</u> Interval Set Mode (counter reset & start) [1, 0, 0, 0]

A 1-second interval signal is output to the TP pin.

• <u>TP = 10-second</u> Interval Set Mode (counter reset & start) [1, 0, 0, 1]

A 10-second interval signal is output to the TP pin.

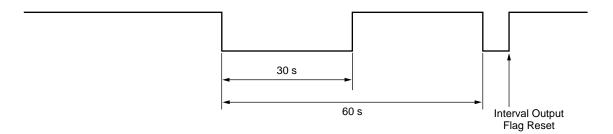

• TP = 30-second Interval Set Mode (counter reset & start) [1, 0, 1, 0]

A 30-second interval signal is output to the TP pin.

• TP = 60-second Interval Set Mode (counter reset & start) [1, 0, 1, 1]

A 60-second interval signal is output to the TP pin.

• Interval Output Flag Reset [1, 1, 0, 0]

The interval signal output to the TP pin is reset.

The interval timer counter continue the operation.

• Interval Timer Clock Run [1, 1, 0, 1]

The timer for outputting interval signals is reset then started.

• Interval Timer Clock Stop [1, 1, 1, 0]

The timer for outputting interval signals stops.

The output status does not change.

(3) Serial command transfer mode setting

Set

$$[C_2, C_1, C_0] = [1, 1, 1]$$

(4) Test mode setting

$$Set \; [C_2,\; C_1,\; C_0] = [1,\; 1,\; 1] \; [C_3',\; C_2',\; C_1',\; C_0'] = [1,\; 1,\; 1,\; 1]$$

o 3-bit parallel command setting mode [C2, C1, C0]

The year function is ineffective when commands are input through C2, C1, and C0 pins.

Generally, February involves 28 days. The 29th day can be set optionally. The next day of the February 29th can be set the March 1st automatically. The interval timer is in the halt state.

- \* The test mode is cancelled by  $[C_2, C_1, C_0] = [0, 0, 0]$  to [1, 1, 0].

- Serial command transfer mode [C<sub>3</sub>', C<sub>2</sub>', C<sub>1</sub>', C<sub>0</sub>']

If a strobe signal is input with  $C_2$ ,  $C_1$ , and  $C_0$  pins set at the  $V_{DD}$  level ([1, 1, 1]), the contents of the serial command register ([ $C_3$ ',  $C_2$ ',  $C_1$ ',  $C_0$ ']) are received as a command; the year function is effective.

\* The test mode is cancelled by [C<sub>3</sub>', C<sub>2</sub>', C<sub>1</sub>', C<sub>0</sub>']

$$= [0, 0, 0]$$

$$= [0, 1, 0, 0]$$

to  $[1, 1, 1, 0]$

In this mode, the serial command register is not held with the Register Hold command. Accordingly, the serial command can be executed irrespective of the mode if the CS pin is active.

The year function is effective in the serial command transfer mode.

#### Interval output function

An interrupt signal can be output by selecting an output from TP.

Interrupt signals are output repeatedly at specified intervals until their output is suppressed by a command. Only output flags can be reset to operate the timer continuously.

Interval of 1 second

The interval signal waveform is rectangular (50 % duty) if not reset.

The interval timer is independent of the Timer Counter, so it is not affected by the resetting of the current time timer.

The interval timer accuracy is  $\pm 15.625$  ms.

\* The interval timer counter is reset by [1, 0, 0, 0] through [1, 0, 1, 1].

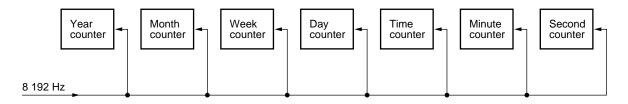

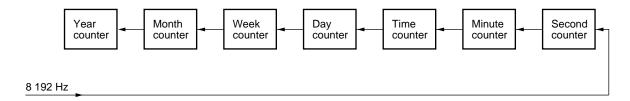

#### o Test mode

In the test mode, data is output to the DATA OUT pin regardless of whether data has been input to OUT ENBL.

There are two different test modes depending on the OUT ENBL data.

(1) Test mode 1 (OUT ENBL = 0)

8 192 Hz signals are set parallel in the counters for year, month, week, day, time, minute, and second. There is no carry from these counters.

#### (2) Test mode 2 (OUT ENBL = 1)

A 8 192 Hz signal is input to the second counter instead of the 1 Hz signal. There is carry from counters.

Outputs from DATA OUT and TP OUT pins in different function modes are listed below.

| MODE           | DATA OUT              | TP      |                | Others                         |

|----------------|-----------------------|---------|----------------|--------------------------------|

| REGISTER HOLD  | 1 Hz                  | 64 Hz   | By this comman | d, TEST MODE is released.      |

| REGISTER SHIFT | LSB of shift register | 32 Hz   |                | 8 192 Hz input to time counter |

| TIME SET       | LSB of shift register | L Level | Test mode      |                                |

| TIME READ      | 1 Hz                  | 32 Hz   |                | 8 192 Hz input to time counter |

When the REGISTER HOLD command cancels the test mode, 64 Hz is output to the TP pin.

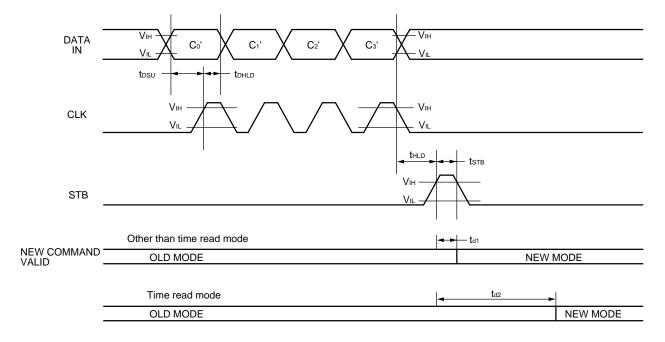

# TIMING DIAGRAM FOR SETTING COMMANDS (Co', C1', C2', C3')

Figure 2.

$$V_{DD}-V_{SS}=2.0~V~t_{DSU}=1~\mu s~MIN.$$

$$t_{DHLD}=1~\mu s~MIN.$$

$$t_{HLD}=1~\mu s~MIN.$$

$$t_{STB}=1~\mu s~MIN.$$

$$t_{d1}=1~\mu s~MAX.~(Other~than~time~read~mode)$$

$$t_{d2}=20~\mu s~MAX.~(Time~read~mode)$$

Note: Command (C2, C1, C0) is set to (1, 1, 1)

CS = "H"

A mode is latched by STB and held until another mode in the same group is set.

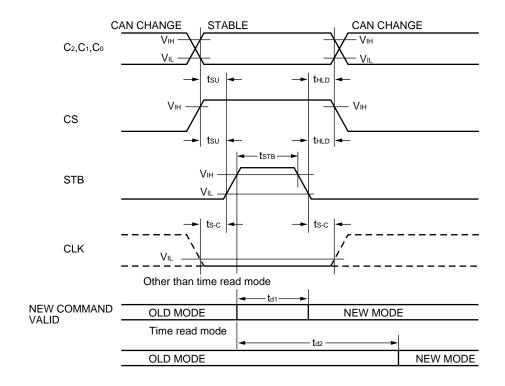

# TIMING DIAGRAM FOR SETTING COMMANDS (Co, C1, C2)

Figure 3.

Note: A mode is latched by STB and held until another mode in the same group is set.

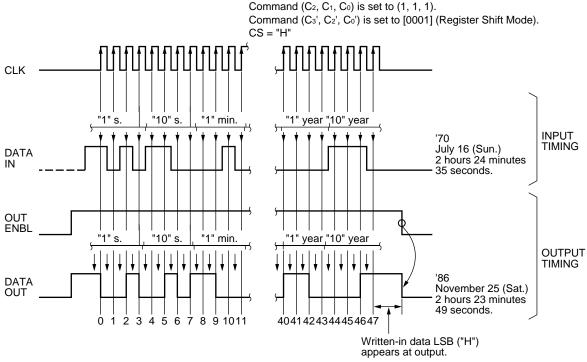

### DATA INPUT/OUTPUT TIMING DIAGRAM

Figure 4.

Note: Reading-in timing of CPU (Trailing edge of CLK).

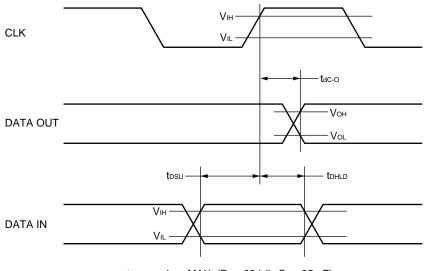

#### TIMING DIAGRAM OF DATA INPUT AND OUTPUT

Figure 5.

t<sub>dC-O</sub> :  $1 \mu$ s MAX. (R<sub>L</sub> = 33 k $\Omega$ , C<sub>L</sub> = 25 pF)

tdsu :  $1 \mu s$  MIN. tdhld :  $1 \mu s$  MIN.

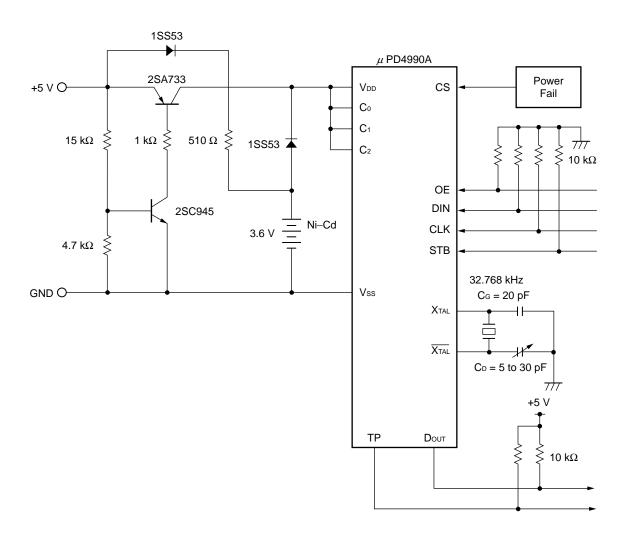

#### **POWER SUPPLY CIRCUIT**

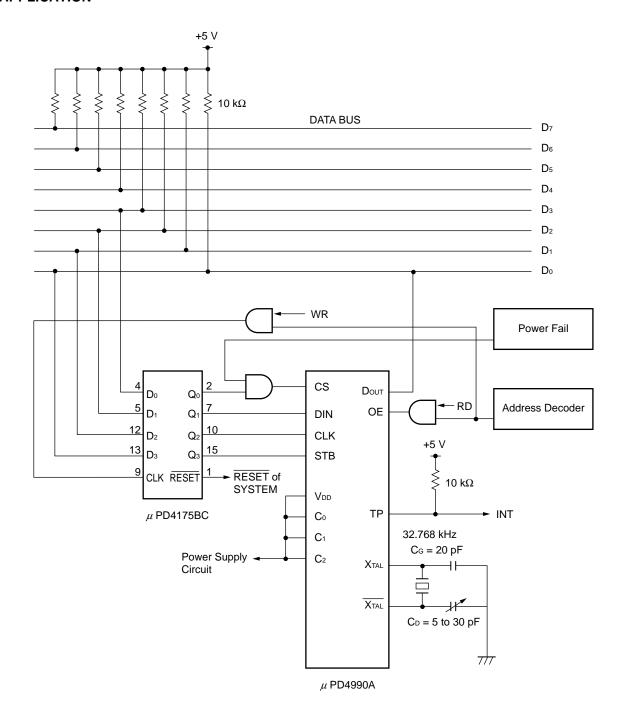

#### **APPLICATION**

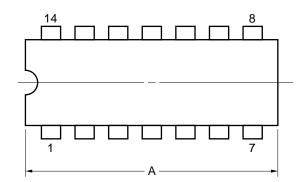

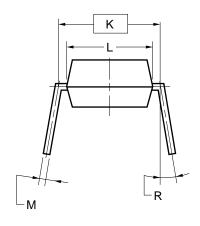

# 14PIN PLASTIC DIP (300 mil)

#### NOTES

- 1) Each lead centerline is located within 0.25 mm (0.01 inch) of its true position (T.P.) at maximum material condition.

- 2) Item "K" to center of leads when formed parallel.

| ITEM | MILLIMETERS                    | INCHES                    |

|------|--------------------------------|---------------------------|

| Α    | 20.32 MAX.                     | 0.800 MAX.                |

| В    | 2.54 MAX.                      | 0.100 MAX.                |

| С    | 2.54 (T.P.)                    | 0.100 (T.P.)              |

| D    | 0.50±0.10                      | $0.020^{+0.004}_{-0.005}$ |

| F    | 1.2 MIN.                       | 0.047 MIN.                |

| G    | 3.5±0.3                        | 0.138±0.012               |

| Н    | 0.51 MIN.                      | 0.020 MIN.                |

| 1    | 4.31 MAX.                      | 0.170 MAX.                |

| J    | 5.08 MAX.                      | 0.200 MAX.                |

| K    | 7.62 (T.P.)                    | 0.300 (T.P.)              |

| L    | 6.4                            | 0.252                     |

| М    | 0.25 <sup>+0.10</sup><br>-0.05 | 0.010+0.004               |

| N    | 0.25                           | 0.01                      |

| R    | 0~15°                          | 0~15°                     |

|      |                                |                           |

P14C-100-300A,C-1

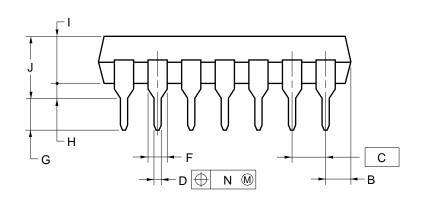

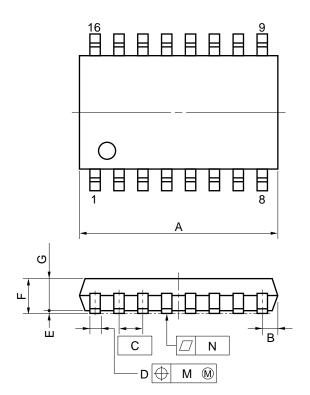

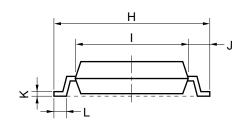

# 16 PIN PLASTIC SOP (300 mil)

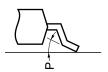

detail of lead end

#### NOTE

Each lead centerline is located within 0.12 mm (0.005 inch) of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS            | INCHES                    |

|------|------------------------|---------------------------|

| IIEW |                        |                           |

| A    | 10.46 MAX.             | 0.412 MAX.                |

| В    | 0.78 MAX.              | 0.031 MAX.                |

| С    | 1.27 (T.P.)            | 0.050 (T.P.)              |

| D    | $0.40^{+0.10}_{-0.05}$ | $0.016^{+0.004}_{-0.003}$ |

| E    | 0.1±0.1                | 0.004±0.004               |

| F    | 1.8 MAX.               | 0.071 MAX.                |

| G    | 1.55                   | 0.061                     |

| Н    | 7.7±0.3                | 0.303±0.012               |

| - 1  | 5.6                    | 0.220                     |

| J    | 1.1                    | 0.043                     |

| K    | $0.20^{+0.10}_{-0.05}$ | $0.008^{+0.004}_{-0.002}$ |

| L    | 0.6±0.2                | $0.024^{+0.008}_{-0.009}$ |

| М    | 0.12                   | 0.005                     |

| N    | 0.10                   | 0.004                     |

| Р    | 3°+7°                  | 3°+7°                     |

P16GM-50-300B-4

[MEMO]

NEC  $\mu$ PD4990A

[MEMO]

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

M4 96.5