## **Product Description**

Stanford Microdevices' SPA-1318 is a high efficiency GaAs Heterojunction Bipolar Transistor (HBT) amplifier housed in a low-cost surface-mountable plastic package. These HBT amplifiers are fabricated using molecular beam epitaxial growth technology which produces reliable and consistent performance from wafer to wafer and lot to lot.

This product is specifically designed for use as a driver amplifier for infrastructure equipment in the 2150 MHz PCS band. Its high linearity makes it an ideal choice for multi-carrier and digital applications.

# **SPA-1318**

# 2150 MHz 1 Watt Power Amplifier with Active Bias

## **Product Features**

- On-chip Active Bias Control

- Power Control Allows Power Consumption Reduction

- Patented High Reliability GaAsHBT Technology

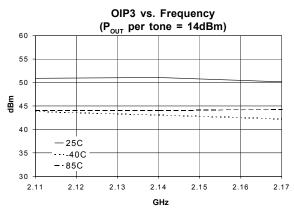

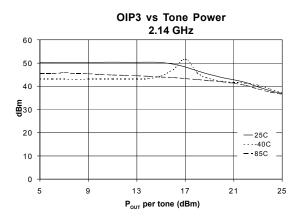

- High Linearity Performance: +48dBm OIP3 Typ.

- Surface-Mountable Plastic Package

# **Applications**

- W-CDMA Systems

- Multi-Carrier Applications

| Symbol                | Parameters: Test Conditions:<br>Z₀ = 50 Ohms Temp = 25°C, Vcc = 5.0V | Units | Min. | Тур.  | Max. |

|-----------------------|----------------------------------------------------------------------|-------|------|-------|------|

| f <sub>o</sub>        | Frequency of Operation                                               | MHz   | 2110 |       | 2170 |

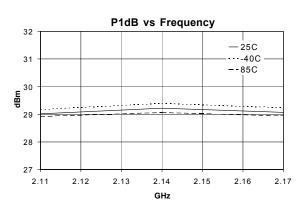

| P <sub>1dB</sub>      | Output Power at 1dB Compression                                      | dBm   |      | 29.5  |      |

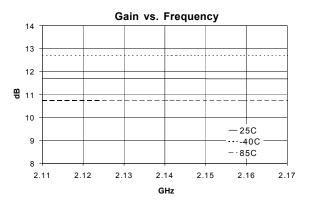

| S <sub>21</sub>       | Small Signal Gain                                                    | dB    |      | 11.5  |      |

| VSWR                  | Input VSWR                                                           | -     |      | 1.4:1 |      |

| OIP <sub>3</sub>      | Output Third Order Intercept Point<br>Power out per tone = +14dBm    | dBm   |      | 48.0  |      |

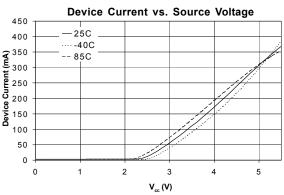

| lcc                   | Device Current                                                       | mA    |      | 320   |      |

| R <sub>th</sub> , j-I | Thermal Resistance (junction - lead)                                 | °C/W  |      | 40    |      |

The information provided herein is believed to be reliable at press time. Stanford Microdevices assumes no responsibility for inaccuracies or omissions. Stanford Microdevices assumes no responsibility for the use of this information, and all such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. Stanford Microdevices does not authorize or warrant any Stanford Microdevices product for use in life-support devices and/or systems. Copyright 2001 Stanford Microdevices, Inc. All worldwider rights reserved.

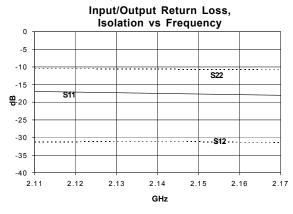

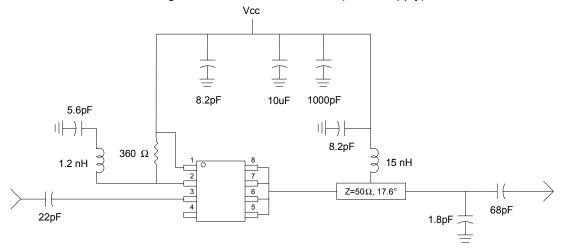

# 2150 MHz Application Circuit Data, Icc=320mA, T=+25C, Vcc=5V

Note: Tuned for Output IP3

850-950 MHz Application Circuit Data (Optimized for IP3), Icc=400mA, T=+25C, Vcc=5V, The W-CDMA setup is PCCPCH+PSCH+SSCH+CPICH+PICH+64 DPCH

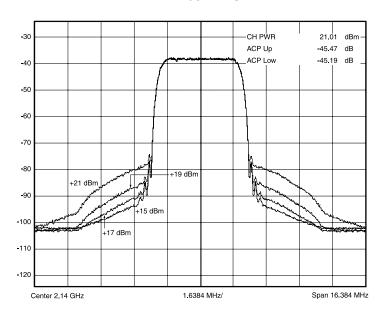

W-CDMA at 2.14 GHz **Adjacent Channel Power** vs. Channel Output Power -30 -35 Adjacent Channel Power (dBc) -40 -45 -50 -55 -60 -65 16 19 25 Channel Output Power (dBm)

#### W-CDMA at 2.14 GHz

## Voltage Feed Resistor Bias Circuit (for 5V supply)

2110 -2170 MHz Schematic

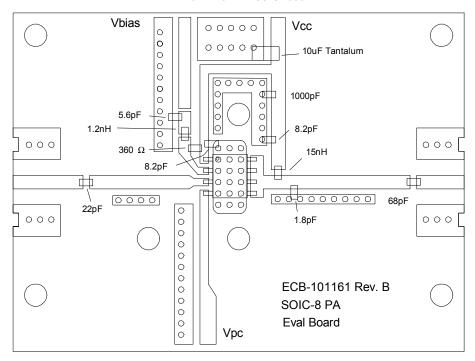

2110 -2170 MHz Evaluation Board Layout

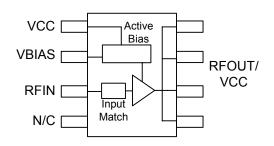

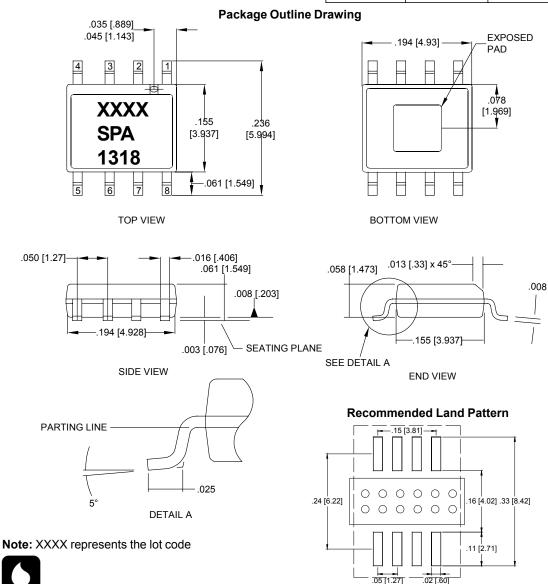

| Pin #      | Function   | Description                                                                                                                                                                                                                                                                                                                                                 | Device Schematic      |  |

|------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|

| 1          | Vcc        | VCC is the supply voltage for the active bias network. Bypassing in the appropriate location as shown on application schematic is required for optimum RF performance.                                                                                                                                                                                      | 1                     |  |

| 2          | Vbias      | Vbias is the bias control pin for the active bias network. Device current is set by the current into this pin. Recommended configuration shown in the Application Schematic is required for optimum RF performance.                                                                                                                                         | 2 ACTIVE BIAS NETWORK |  |

| 3          | RF In      | RF input pin. This pin requires the use of an external DC blocking capacitor.                                                                                                                                                                                                                                                                               |                       |  |

| 4          | N/C        | No connection                                                                                                                                                                                                                                                                                                                                               | 3                     |  |

| 5, 6, 7, 8 | RF Out/Vcc | RF output and bias pin. Bias should be supplied to this pin through an external RF choke. Because DC biasing is present on this pin, a DC blocking capacitor should be used in most applications (see application schematic). The supply side of the bias network should be well bypassed. An output matching network is necessary for optimum performance. |                       |  |

| EPAD       | Gnd        | Exposed area on the bottom side of the package needs to be soldered to the ground plane of the board for optimum thermal and RF performance. Several vias should be located under the EPAD as shown in the recommended land pattern (page 6).                                                                                                               | V                     |  |

## **Absolute Maximum Ratings**

Operation of this device above any one of these parameters may cause permanent damage.

Bias Conditions should also satisfy the following expression:  $I_DV_D$  (max) <  $(T_J - T_{OP})/R_{th}$ , j-l

Caution: ESD sensitive

Appropriate precautions in handling, packaging and testing devices must be observed.

| Parameter                                        | Value       | Unit |

|--------------------------------------------------|-------------|------|

| Supply Current (I <sub>D</sub> )                 | 750         | mA   |

| Device Voltage (V <sub>D</sub> )                 | 6.0         | V    |

| Power Dissipation                                | 4.0         | W    |

| Operating Lead Temperature (T <sub>L</sub> )     | -40 to +85  | ℃    |

| RF Input Power                                   | 800         | mW   |

| Storage Temperature Range                        | -40 to +150 | ℃    |

| Operating Junction Temperature (T <sub>J</sub> ) | +150        | ℃    |

#### Part Number Ordering Information

| Part Number | Devices Per Reel | Reel Size |

|-------------|------------------|-----------|

| SPA-1318    | 500              | 7"        |

Note: Parts need to be baked prior to use as discussed in application note AN-029 (Special handling information for Exposed Pad ™ SOIC-8 products) to ensure no moisture is trapped in the encapsulated package. In production, this baking procedure is not necessary if parts are used within 48 hours of opening the sealed shipping materials.