# **MAS9078**

## **AM Receiver IC**

- High Sensitivity

- Very Low Power Consumption

- Wide Supply Voltage Range

- Power Down Control

- Control for AGC On

- High Selectivity by Crystal Filter

- Fast Startup Feature

APPLICATIONS

## DESCRIPTION

The MAS9078 AM-Receiver chip is a highly sensitive, simple to use AM receiver specially intended to receive time signals in the frequency range from 40 kHz to 100 kHz. Only a few external components are required for time signal receiver. The circuit has preamplifier, wide range automatic gain control, demodulator and output comparator

built in. The output signal can be processed directly by an additional digital circuitry to extract the data from the received signal. The control for AGC (automatic gain control) can be used to switch AGC on or off if necessary. Unlike MAS1016A and MAS1016B, MAS9078 does not require AGC control procedure in WWVB and JJY systems.

Time Signal Receiver WWVB (USA), JJY (Japan),

DCF77 (Germany) and MSF (UK)

Receiver for ASK Modulated Data Signals

## FEATURES

- Highly Sensitive AM Receiver, 0.4  $\mu V_{\text{RMS}}$  typ.

- Wide Supply Voltage Range from 1.1 V to 3.6 V

- Very Low Power Consumption

- Power Down Control

- Fast Startup

- Only a Few External Components Necessary

- Control for AGC On

- Wide Frequency Range from 40 kHz to 100 kHz

- High Selectivity by Quartz Crystal Filter

- Die and TSSOP-16 Package

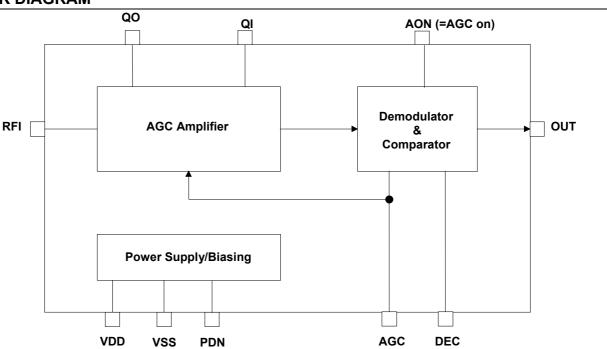

## **BLOCK DIAGRAM**

1702 µm

| VSS RFI PDN AON DEC |         |

|---------------------|---------|

| 9078Bx              | 1778 µm |

| VDD QO QI AGC OUT   |         |

DIE size =  $1.70 \times 1.78 \text{ mm}$ ; PAD size =  $100 \times 100 \mu \text{m}$

**Note:** Because the substrate of the die is internally connected to VDD, the die has to be connected to VDD or left floating. Please make sure that VDD is the first pad to be bonded. Pick-and-place and all component assembly are recommended to be performed in ESD protected area.

Note: Coordinates are pad center points where origin has been located in the center of VDD pad

**Note:** The on-chip product code 9078Bx identifies internal compensation capacitance option. x has values 1, 2, 3, 4 or 5 refering to capacitance option described in the Table 2 on page 4.

| Pin Description       | Name | X-coordinate | Y-coordinate | Note |

|-----------------------|------|--------------|--------------|------|

| Power Supply Voltage  | VDD  | 0 µm         | 0 µm         |      |

| Quarz Filter Output   | QO   | 306 µm       | 19 μm        |      |

| Quarz Filter Input    | QI   | 586 μm       | 19 µm        |      |

| AGC Capacitor         | AGC  | 866 µm       | 19 µm        |      |

| Receiver Output       | OUT  | 1109 μm      | 19 µm        | 1    |

| Demodulator Capacitor | DEC  | 1109 μm      | 1428 μm      |      |

| AGC On Control        | AON  | 866 µm       | 1428 μm      | 2    |

| Power Down Input      | PDN  | 549 μm       | 1428 μm      | 3    |

| Receiver Input        | RFI  | 306 µm       | 1428 μm      |      |

| Power Supply Ground   | VSS  | 16 µm        | 1407 μm      |      |

Notes:

- 1) OUT = VSS when carrier amplitude at maximum; OUT = VDD when carrier amplitude is reduced (modulated)

- the output is a current source/sink with  $|I_{OUT}| > 5 \mu A$

- at power down the output is pulled to VSS (pull down switch)

- AON = VSS means AGC off (hold current gain level); AON = VDD means AGC on (working)

Internal pull-up with current < 1 μA which is switched off at power down</li>

- 3) PDN = VSS means receiver on; PDN = VDD means receiver off

- Fast start-up is triggered when the receiver is after power down (PDN=VDD) controlled to power up (PDN=VSS) i.e. at the falling edge of PDN signal.

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter             | Symbol              | Conditions | Min                  | Max                  | Unit |

|-----------------------|---------------------|------------|----------------------|----------------------|------|

| Supply Voltage        | $V_{DD}$ - $V_{SS}$ |            | -0.3                 | 5.0                  | V    |

| Input Voltage         | V <sub>IN</sub>     |            | V <sub>SS</sub> -0.3 | V <sub>DD</sub> +0.3 | V    |

| Power Dissipation     | P <sub>MAX</sub>    |            |                      | 100                  | mW   |

| Operating Temperature | T <sub>OP</sub>     |            | -20                  | 70                   | °C   |

| Storage Temperature   | T <sub>ST</sub>     |            | -40                  | 120                  | °C   |

## **ELECTRICAL CHARACTERISTICS**

| Parameter                                                                                    | Symbol                             | Conditions                                                                                                                         | Min                 | Тур      | Max                 | Unit     |

|----------------------------------------------------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------|---------------------|----------|

| Operating Voltage                                                                            | V <sub>DD</sub>                    |                                                                                                                                    | 1.10                |          | 3.60                | V        |

| Current Consumption                                                                          | I <sub>DD</sub>                    | VDD=3.6 V, Vin=0 μV<br>VDD=1.4 V, Vin=0 μV                                                                                         | 56                  | 76<br>66 | 95                  | μA       |

| Stand-By Current                                                                             | I <sub>DDoff</sub>                 |                                                                                                                                    |                     |          | 0.1                 | μA       |

| Input Frequency Range                                                                        | f <sub>IN</sub>                    |                                                                                                                                    | 40                  |          | 100                 | kHz      |

| Minimum Input Voltage                                                                        | V <sub>IN min</sub>                |                                                                                                                                    |                     | 0.4      | 1                   | μVrms    |

| Maximum Input Voltage                                                                        | V <sub>IN max</sub>                |                                                                                                                                    | 20                  |          |                     | mVrms    |

| Input Levels $ I_{IN} $ <0.5 $\mu$ A                                                         | V <sub>IL</sub><br>V <sub>IH</sub> |                                                                                                                                    | 0.8 V <sub>DD</sub> |          | 0.2 V <sub>DD</sub> | V        |

| Output Current<br>V <sub>OL</sub> <0.2 V <sub>DD</sub> ;V <sub>OH</sub> >0.8 V <sub>DD</sub> | Ι <sub>ουτ</sub>                   |                                                                                                                                    | 5                   |          |                     | μA       |

| Output Pulse                                                                                 | T <sub>100ms</sub>                 | $\begin{array}{l} 1 \hspace{0.1cm} \mu Vrms \hspace{0.1cm} \leq \hspace{0.1cm} V_{IN} \leq \\ 20 \hspace{0.1cm} mVrms \end{array}$ | 50                  |          | 140                 | ms       |

|                                                                                              | T <sub>200ms</sub>                 | $\begin{array}{l} 1 \ \mu Vrms \ \leq V_{\text{IN}} \leq \\ 20 \ mVrms \end{array}$                                                | 150                 |          | 230                 | ms       |

|                                                                                              | T <sub>500ms</sub>                 | $\begin{array}{l} 1 \ \mu Vrms \ \leq V_{\text{IN}} \leq \\ 20 \ mVrms \end{array}$                                                | 400                 | 500      | 600                 | ms       |

|                                                                                              | T <sub>800ms</sub>                 | $\begin{array}{l} 1 \ \mu Vrms \ \leq V_{\text{IN}} \leq \\ 20 \ mVrms \end{array}$                                                | 700                 | 800      | 900                 | ms       |

| Startup Time                                                                                 | T <sub>Start</sub>                 | Fast Start-up<br>Without Fast Start-up                                                                                             |                     | 12<br>3  |                     | s<br>min |

| Output Delay Time                                                                            | T <sub>Delay</sub>                 |                                                                                                                                    |                     | 50       | 100                 | ms       |

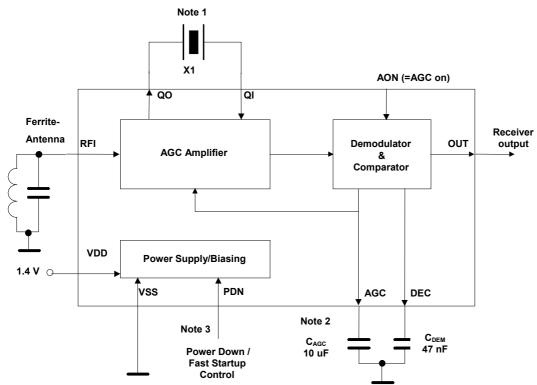

#### TYPICAL APPLICATION

#### Note 1: Crystal

The crystal as well as ferrite antenna frequencies are chosen according to the time-signal system (Table 1). The crystal shunt capacitance C<sub>0</sub> should be matched as well as possible with the internal shunt capacitance compensation capacitance C<sub>c</sub>. MAS9078 has five compensation capacitance options. Capacitance values and suitable crystals are described in Table 2. See also Ordering Information (p.10).

| Time-Signal System | Location       | Antenna Frequency | Recommended Crystal Frequency |

|--------------------|----------------|-------------------|-------------------------------|

| DCF77              | Germany        | 77.5 kHz          | 77.503 kHz                    |

| MSF                | United Kingdom | 60 kHz            | 60.003 kHz                    |

| WWVB               | USA            | 60 kHz            | 60.003 kHz                    |

| JJY                | Japan          | 40 kHz and 60 kHz | 40.003 kHz and 60.003 kHz     |

Table 1 **Time-Signal System Frequencies**

| Device    | Cc                | Crystal Description                                                |

|-----------|-------------------|--------------------------------------------------------------------|

| MAS9078B1 | 0.75 pF           | For single low C₀ crystal (Nominal value)                          |

| MAS9078B2 | 1.25 pF           | For single high C <sub>0</sub> crystal                             |

| MAS9078B3 | 1.625 pF          | For two parallel low C <sub>0</sub> crystals (dual band receiver)  |

| MAS9078B4 | 2.5 pF            | For two parallel high C <sub>0</sub> crystals (dual band receiver) |

| MAS9078B5 | 3.875 pF          | Any crystal with parallel external compensation capacitor          |

| Table 2   | Compensation Capa | acitance Options                                                   |

l able 2 Compensation Capacitance Options

#### Note 2: AGC Capacitor

The AGC and DEC capacitors must have low leakage currents due to very small 40 nA signal currents through the capacitors. The insulation resistance of these capacitors should be higher than 70 M $\Omega$ . Also probes with at least 100 M $\Omega$  impedance should be used for voltage probing of AGC and DEC pins.

#### Note 3: Power Down / Fast Startup Control

Both power down and fast startup are controlled using the PDN pin. The device is in power down (turned off) if PDN = VDD and in power up (turned on) if PDN = VSS. Fast startup is triggered by the falling edge of PDN signal, i.e., controlling device from power down to power up. The startup time without using the fast startup control can be several minutes but with fast startup it is shortened typically to 12 s.

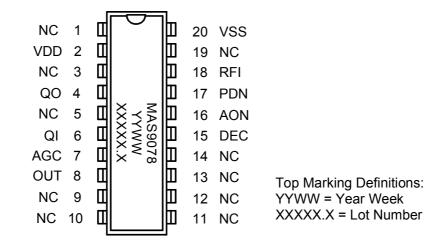

SAMPLES IN SBDIL 20 PACKAGE

#### **PIN DESCRIPTION**

| Pin Name | Pin | Туре | Function              | Note |

|----------|-----|------|-----------------------|------|

| NC       | 1   |      |                       |      |

| VDD      | 2   | Р    | Positive Power Supply |      |

| NC       | 3   |      |                       |      |

| QO       | 4   | AO   | Quartz Filter Output  |      |

| NC       | 5   |      |                       | 1    |

| QI       | 6   | AI   | Quartz Filter Input   |      |

| AGC      | 7   | AO   | AGC Capacitor         |      |

| OUT      | 8   | DO   | Receiver Output       | 2    |

| NC       | 9   |      |                       |      |

| NC       | 10  |      |                       |      |

| NC       | 11  |      |                       |      |

| NC       | 12  |      |                       |      |

| NC       | 13  |      |                       |      |

| NC       | 14  |      |                       |      |

| DEC      | 15  | AO   | Demodulator Capacitor |      |

| AON      | 16  | DI   | AGC On Control        | 3    |

| PDN      | 17  | AI   | Power Down Input      | 4    |

| RFI      | 18  | AI   | Receiver Input        |      |

| NC       | 19  |      |                       |      |

| VSS      | 20  | G    | Power Supply Ground   |      |

Notes:

Pin 5 between quartz crystal filter pins must be connected to VSS to eliminate DIL package leadframe parasitic capacitances disturbing the crystal filter performance. All other NC (Not Connected) pins are also recommended to be connected to VSS to minimize noise coupling.

OUT = VSS when carrier amplitude at maximum; OUT = VDD when carrier amplitude is reduced (modulated)

- the output is a current source/sink with  $|I_{OUT}| > 5 \mu A$

at power down the output is pulled to VSS (pull down switch)

- 3) AON = VSS means AGC off (hold current gain level); AON = VDD means AGC on (working)

- Internal pull-up with current < 1 μA which is switched off at power down

- 4) PDN = VSS means receiver on; PDN = VDD means receiver off

- Fast start-up is triggered when the receiver is after power down (PDN=VDD) controlled to power up (PDN=VSS) i.e. at the falling edge of PDN signal.

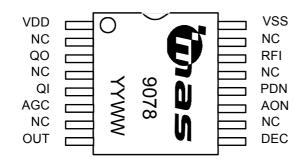

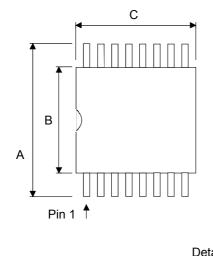

#### **PIN CONFIGURATION & TOP MARKING FOR PLASTIC TSSOP-16 PACKAGE**

Top Marking Definitions: YYWW = Year Week

#### **PIN DESCRIPTION**

| Pin Name | Pin | Туре | Function              | Note |

|----------|-----|------|-----------------------|------|

| VDD      | 1   | Р    | Positive Power Supply |      |

| NC       | 2   |      |                       |      |

| QO       | 3   | AO   | Quartz Filter Output  |      |

| NC       | 4   |      |                       | 1    |

| QI       | 5   | AI   | Quartz Filter Input   |      |

| AGC      | 6   | AO   | AGC Capacitor         |      |

| NC       | 7   |      |                       |      |

| OUT      | 8   | DO   | Receiver Output       | 2    |

| DEC      | 9   | AO   | Demodulator Capacitor |      |

| NC       | 10  |      |                       |      |

| AON      | 11  | DI   | AGC On Control        | 3    |

| PDN      | 12  | AI   | Power Down Input      | 4    |

| NC       | 13  |      |                       |      |

| RFI      | 14  | AI   | Receiver Input        |      |

| NC       | 15  |      |                       |      |

| VSS      | 16  | G    | Power Supply Ground   |      |

Notes:

- Pin 4 between quartz crystal filter pins must be connected to VSS to eliminate package leadframe parasitic capacitances disturbing the crystal filter performance. All other NC (Not Connected) pins are also recommended to be connected to VSS to minimize noise coupling.

- 2) OUT = VSS when carrier amplitude at maximum; OUT = VDD when carrier amplitude is reduced (modulated)

- the output is a current source/sink with  $|I_{OUT}| > 5 \mu A$

- at power down the output is pulled to VSS (pull down switch)

- AON = VSS means AGC off (hold current gain level); AON = VDD means AGC on (working)

Internal pull-up (to AGC on) with current < 1 μA which is switched off at power down</li>

- 4) PDN = VSS means receiver on; PDN = VDD means receiver off

- Fast start-up is triggered when the receiver is after power down (PDN=VDD) controlled to power up (PDN=VSS) i.e. at the falling edge of PDN signal.

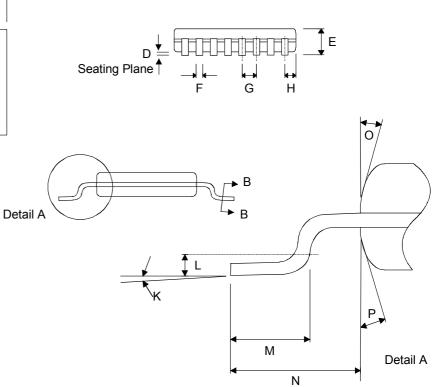

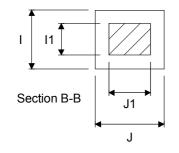

## PACKAGE (TSSOP16) OUTLINES

| Dimension                     | Min  | Мах    | Unit |

|-------------------------------|------|--------|------|

| A                             | 6.4  | IO BSC | mm   |

| В                             | 4.30 | 4.50   | mm   |

| С                             | 5.0  | 00 BSC | mm   |

| D                             | 0.05 | 0.15   | mm   |

| E                             |      | 1.10   | mm   |

| F                             | 0.19 | 0.30   | mm   |

| G                             | 0.6  | 65 BSC | mm   |

| Н                             | 0.18 | 0.28   | mm   |

|                               | 0.09 | 0.20   | mm   |

| I1                            | 0.09 | 0.16   | mm   |

| J                             | 0.19 | 0.30   | mm   |

| J1                            | 0.19 | 0.25   | mm   |

| K                             | 0°   | 8°     |      |

| L                             | 0.24 | 0.26   | mm   |

| М                             | 0.50 | 0.75   | mm   |

| (The length of a terminal for |      |        |      |

| soldering to a substrate)     |      |        |      |

| Ν                             | 1.(  | mm     |      |

| 0                             |      |        |      |

| Р                             |      |        |      |

Dimensions do not include mold flash, protrusions, or gate burrs. All dimensions are in accordance with JEDEC standard MO-153.

## SOLDERING INFORMATION

| Resistance to Soldering Heat    | According to RSH test IEC 68-2-58/20 2*220°C                |

|---------------------------------|-------------------------------------------------------------|

| Maximum Temperature             | 240°C                                                       |

| Maximum Number of Reflow Cycles | 2                                                           |

| Reflow profile                  | Thermal profile parameters stated in JESD22-A113 should not |

|                                 | be exceeded. http://www.jedec.org                           |

| Seating Plane Co-planarity      | max 0.08 mm                                                 |

| Lead Finish                     | Solder plate 7.62 - 25.4 µm, material Sn 85% Pb 15%         |

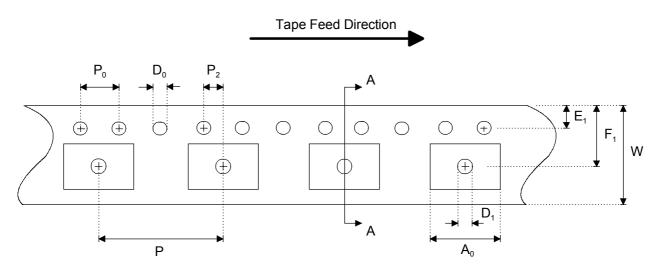

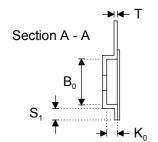

## EMBOSSED TAPE SPECIFICATIONS

Tape Feed Direction

Pin 1 Designator

| Dimension      | Min       | Мах        | Unit |

|----------------|-----------|------------|------|

| A <sub>0</sub> | 6.50      | 6.70       | mm   |

| B <sub>0</sub> | 5.20      | 5.40       | mm   |

| D <sub>0</sub> | 1.50 +0.1 | 10 / -0.00 | mm   |

| D <sub>1</sub> | 1.50      |            | mm   |

| E <sub>1</sub> | 1.65      | 1.85       | mm   |

| F <sub>1</sub> | 7.20      | 7.30       | mm   |

| K <sub>0</sub> | 1.20      | 1.40       | mm   |

| Р              | 11.90     | 12.10      | mm   |

| P <sub>0</sub> | 4         | .0         | mm   |

| P <sub>2</sub> | 1.95      | 2.05       | mm   |

| S <sub>1</sub> | 0.6       |            | mm   |

| Т              | 0.25      | 0.35       | mm   |

| W              | 11.70     | 12.30      | mm   |

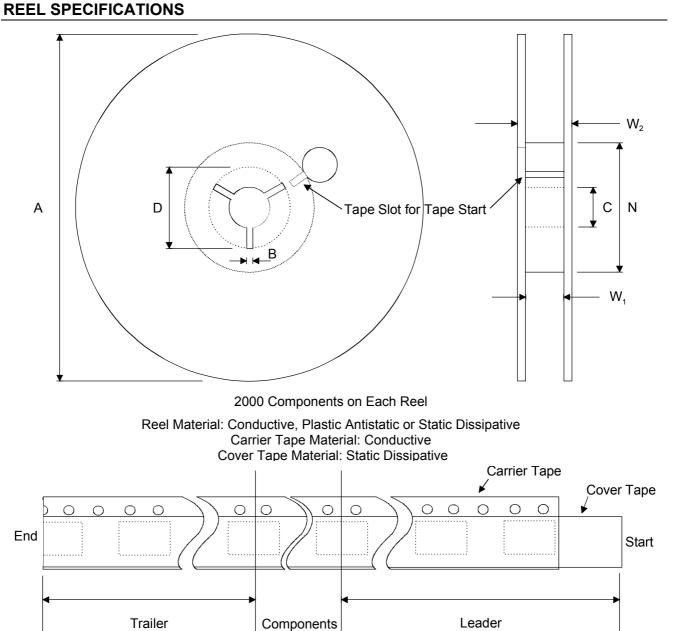

| Dimension         | Min                      | Max   | Unit |

|-------------------|--------------------------|-------|------|

| А                 |                          | 330   | mm   |

| В                 | 1.5                      |       | mm   |

| С                 | 12.80                    | 13.50 | mm   |

| D                 | 20.2                     |       | mm   |

| Ν                 | 50                       |       | mm   |

| W <sub>1</sub>    | 12.4                     | 14.4  | mm   |

| (measured at hub) |                          |       |      |

| W <sub>2</sub>    |                          | 18.4  | mm   |

| (measured at hub) |                          |       |      |

| Trailer           | 160                      |       | mm   |

| Leader            | 390,                     |       | mm   |

|                   | of which minimum 160     |       |      |

|                   | mm of empty carrier tape |       |      |

|                   | sealed with cover tape   |       |      |

| Weight            |                          | 1500  | g    |

### **ORDERING INFORMATION**

| Product Code  | Product        | Package                            | Capacitance Option              |

|---------------|----------------|------------------------------------|---------------------------------|

| MAS9078BTB1   | AM-Receiver IC | EWS-tested wafer, Thickness 480 µm | $C_{\rm C}$ = 0.75 pF (Nominal) |

| MAS9078BTB2   | AM-Receiver IC | EWS-tested wafer, Thickness 480 µm | C <sub>c</sub> = 1.25 pF        |

| MAS9078BTB3   | AM-Receiver IC | EWS-tested wafer, Thickness 480 µm | C <sub>C</sub> = 1.625 pF       |

| MAS9078BTB4   | AM-Receiver IC | EWS-tested wafer, Thickness 480 µm | C <sub>c</sub> = 2.5 pF         |

| MAS9078BTB5   | AM-Receiver IC | EWS-tested wafer, Thickness 480 µm | C <sub>C</sub> = 3.875 pF       |

| MAS9078BTC1   | AM-Receiver IC | EWS-tested wafer, Thickness 400 µm | C <sub>C</sub> = 0.75 pF        |

| MAS9078BTC2   | AM-Receiver IC | EWS-tested wafer, Thickness 400 µm | C <sub>c</sub> = 1.25 pF        |

| MAS9078BTC3   | AM-Receiver IC | EWS-tested wafer, Thickness 400 µm | C <sub>C</sub> = 1.625 pF       |

| MAS9078BTC4   | AM-Receiver IC | EWS-tested wafer, Thickness 400 µm | C <sub>c</sub> = 2.5 pF         |

| MAS9078BTC5   | AM-Receiver IC | EWS-tested wafer, Thickness 400 µm | C <sub>C</sub> = 3.875 pF       |

| MAS9078BUA1-T | AM-Receiver IC | TSSOP-16, Tape & Reel              | $C_{C}$ = 0.75 pF (Nominal)     |

Contact Micro Analog Systems Oy for other wafer thickness options.

## LOCAL DISTRIBUTOR

## MICRO ANALOG SYSTEMS OY CONTACTS

| Micro Analog Systems Oy  | Tel. +358 9 80 521    |

|--------------------------|-----------------------|

|                          | Fax +358 9 805 3213   |

| FIN-02771 Espoo, FINLAND | http://www.mas-oy.com |

#### NOTICE

Micro Analog Systems Oy reserves the right to make changes to the products contained in this data sheet in order to improve the design or performance and to supply the best possible products. Micro Analog Systems Oy assumes no responsibility for the use of any circuits shown in this data sheet, conveys no license under any patent or other rights unless otherwise specified in this data sheet, and makes no claim that the circuits are free from patent infringement. Applications for any devices shown in this data sheet are for illustration only and Micro Analog Systems Oy makes no claim or warranty that such applications will be suitable for the use specified without further testing or modification.