www.DataSheetAU.com

TVPO 2066

TV Controller

with On-Screen Display

for TV Receivers

# **TVPO 2066**

### Contents

| Page | Section | Title                                              |

|------|---------|----------------------------------------------------|

| 3    | 1.      | Introduction                                       |

| 3    | 2.      | The Functional Blocks of the TVPO 2066             |

| 3    | 2.1.    | The 8049 Microcomputer                             |

| 4    | 2.2.    | The Remote–Control Decoder                         |

| 4    | 2.3.    | The Mains Flip–Flop and Reset Circuit              |

| 4    | 2.4.    | The IM Bus and Non–Volatile Memory                 |

| 5    | 2.5.    | The Clock Generator and the Sequence Control       |

| 5    | 2.6.    | The D/A Converters for the Analog Outputs          |

| 5    | 2.7.    | The Tuning Voltage Generator                       |

| 5    | 2.8.    | The Ports                                          |

| 5    | 2.9.    | The On–Screen Display                              |

| 5    | 2.9.1.  | Outputs and Inputs for the OSD                     |

| 5    | 2.9.2.  | Display Format                                     |

| 6    | 2.9.3.  | Display Control                                    |

| 7    | 3.      | <b>Description of Hardware Component Registers</b> |

| 8    | 3.1.    | Registers for Infrared Control                     |

| 8    | 3.2.    | Register for Port 3                                |

| 8    | 3.3.    | Registers for IM–Bus Control                       |

| 8    | 3.4.    | Registers for Analog Outputs & MAINS–Control       |

| 8    | 3.5.    | Registers for On–Screen Display                    |

| 9    | 4.      | Specifications                                     |

| 9    | 4.1.    | Outline Dimensions                                 |

| 9    | 4.2.    | Pin Connections                                    |

| 9    | 4.2.1.  | 40–Pin DIL Package                                 |

| 10   | 4.2.2.  | 44–Pin PLCC Package                                |

| 11   | 4.3.    | Pin Descriptions                                   |

| 12   | 4.4.    | Pin Circuits                                       |

| 14   | 4.5.    | Electrical Characteristics                         |

| 14   | 4.5.1.  | Absolute Maximum Ratings                           |

| 15   | 4.5.2.  | Recommended Operating Conditions                   |

| 16   | 4.5.3.  | Characteristics                                    |

| 17   | 5.      | Appendix                                           |

| 17   | 5.1.    | DAC Poly–Counter Code                              |

| 18   | 5.2.    | On–Screen Display Format                           |

| 19   | 5.3.    | Character Set                                      |

| 20   | 5.4.    | Programmed Versions of TVPO 2066                   |

| 20   | 5.5.    | User Options                                       |

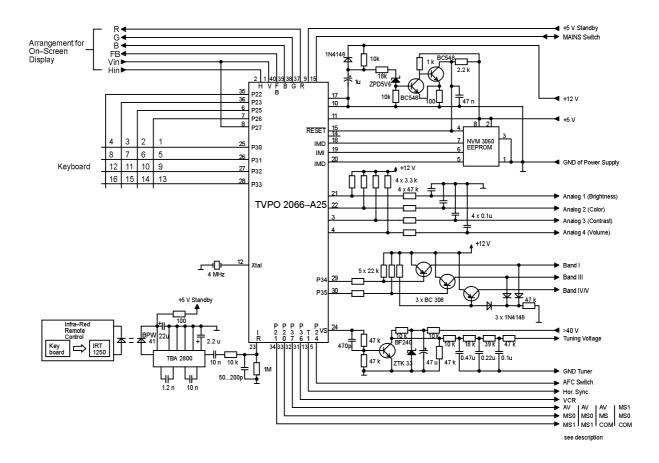

| 21   | 5.6.    | Application Circuit                                |

# TV-Controller with Integrated On-Screen Display Ability

#### 1. Introduction

In comparison to the older TVPO 2065 hardware, the port 3 of the TVPO 2066 consists of 6 x 12 V/2 mA opendrain outputs instead of 5 V/25 mA open—drain outputs.

"TVPO 2066" is the name of the unprogrammed hardware. The programmed versions will be called:

- TVPO 2066-Axx for analog TV-sets

- TVPO 2066-Dxx for digital TV-sets

with the version–no. xx. Application diagrams and descriptions of different software versions are available in additional data sheets.

The TVPO 2066 is an intelligent microcomputer in N-channel MOS technology. On one silicon chip, it contains all operating and tuning functions of a modern TV receiver. Thus, along with the non-volatile memory (MDA 2062, NVM 3060), the SAA 1250, IRT 1250 or IRT 1260 remote-control transmitter and the TBA 2800 preamplifier this offers a very economic solution for TV receivers with on-screen display and voltage synthesizer.

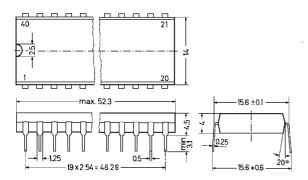

The device is available in 44-pin PLCC package and 40-pin DIL package. The PLCC version has 4 pins more for digital combined inputs/outputs.

#### 2. The Functional Blocks of the TVPO 2066

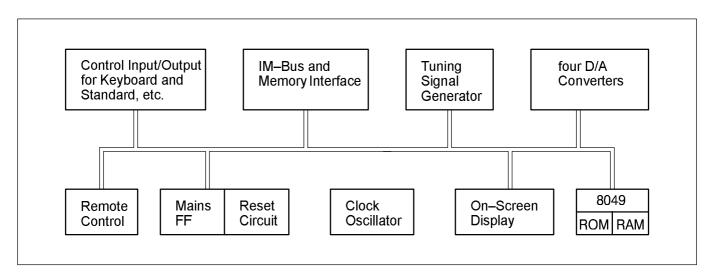

The hardware components of the TVPO 2066 are:

- 8048-core, fully compatible to 8048 instruction set

- 10K ROM, 256 byte RAM

- four 64 steps analog output to control vol., color etc.

- single 4032 steps analog output for controlling of a VS-tuner

- IR decoder for ITT-IR (remote control with IRT 1250/60)

- mains flip-flop for standby mode

- IM-bus interface for non-volatile memory and devices of DIGIT 2000 system for digital video-processing.

- fast counter input (T1) for automatic search (for analog TV–sets)

- 12 digital combined inputs/outputs (8 or 10 for DIL– package)

- 8 digital outputs

- integrated 12-digit on-screen display

#### 2.1. The 8049 Microcomputer

For the description of the commands and characteristics of the 8049, please refer to the CCU 2030, CCU 2050, CCU 2070 data sheet.

The 8049 provides separate address space for program, data, in/out, and external data. The ROM is organized in banks of 2 K Bytes. Bank 0 occupies the addresses 0 to 2047. The other banks (10, 11, 12, 13) share the addresses 2048 to 4095. The different banks are selected through the bank select register 15 as described for the CCU 2070 in the CCU 2030, 2050, 2070 data sheet. Banks 14 through 17 of the CCU 2070 are not available in the TVPO.

The data and control registers of the TVPO's peripheral units are located in the address space of external data.

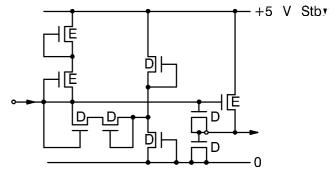

Fig. 1-1: Functional block diagram of the TVPO 2066

They are accessed by the "Move External" instruction (MOVX). Electrically, the connection is provided by the lines  $DB_0$  to  $DB_{7}$ ,  $\overline{RD}$ ,  $\overline{WR}$ , and ALE. These connections of the 8049 microcomputer are not available during normal operation. In "Test Mode" (EA = 5 V or EA = 12 V), some pins are switched so that the TVPO's peripherals can be accessed from the outside via  $DB_0$  to  $DB_7$ .

In normal operation, only P2 of the 8049's original ports remains unchanged. During test operation,  $\overline{RD}$ ,  $\overline{WR}$ , ALE and  $\overline{PSEN}$  are connected to P2<sub>4</sub> to P2<sub>7</sub> (compare CCU 2030, CCU 2050, CCU 2070 data sheet).

#### 2.2. The Remote-Control Decoder

In the already mentioned standby mode, and also during normal operation, the remote–control decoder expects infrared–transmitted signals that were transmitted by the SAA 1250, IRT 1250 or IRT 1260 remote–control transmitter IC, received by an infrared photo diode, and amplified by the TBA 2800 infrared preamplifier IC. The decoder frees the remote–control signal from interference and decodes each command word that is recognized as correct. A valid command word is made available to the microcomputer by way of two registers. No interrupt is initiated. Rather, it is the task of the program to continuously check the infrared registers.

A command word transmitted via infrared consists of 10 bits – four address bits and six data bits. These two parts of the command word are provided in two different registers. Bit 7 in the address register is low when a valid command word is detected. When the data word is read, both infrared registers are cleared.

It is possible to mask–program which infrared commands also carry the power–on information and switch the TVPO from standby to full operation. For this purpose, up to five groups of commands within a binary decoder matrix are programmable for one infrared address (compare CCU 2030, CCU 2050, CCU 2070 data sheet).

#### 2.3. The Mains Flip-Flop and Reset Circuit

Mains flip—flop and reset circuit operate from the standby supply. After switching on the standby supply it takes 100 ms at most until the TVPO is in full standby operation. The Mains output is controlled by the mains flip flop. In the

"Mains off" position the output is high.

The mains flip–flop is set by means of the infrared "Mains on" commands or by an active low level applied to the  $\overline{\text{Mains}}$  output for at least 20  $\mu s$ . A reset for the mains flip–flop is generated whenever:

The standby supply voltage is less than approx. 3.5 V (e.g. during power–on) 2. The microcomputer executes a "Mains off" command.

The microcomputer clears the mains flip—flop by writing a 1 into bit 3 of the external register 13. In order to properly charge the stray capacitances at the Mains output, the mains flip—flop remains blocked in the "Mains off" position for 16 ms after any reset. After this time has elapsed, the TV set may be turned on again.

With no Reset option set (compare CCU 2030, CCU 2050, CCU 2070 data sheet), the mains flip–flop is also reset by any Reset signal going low. The TVPO–internal Reset', which is different from the externally–applied Reset is high only when both Mains is in the low state and Reset is at high level. Two options are mask–programmable in this respect:

Reset 1: The Reset signal, going low, does not reset the mains flip–flop. If the customer does not specify, this option will be set as default.

Reset 2: The TVPO-internal Reset' is identical to the Reset signal and independent of the state of the mains flip-flop.

Resetting the mains flip–flop clears the remote–control decoder. The other parts of the TVPO are cleared by the TVPO–internal Reset' signal via the Reset input. Delaying the Reset signal with respect to the V<sub>DD</sub> supply voltage is done by an external RC network at the Reset input.

The input voltage of the regulator for the 5 V  $V_{DD}$  supply voltage should be monitored to prevent the system's circuits from resetting improperly and the NVM 3060 EE-PROM from programming false data.

With no Reset option set, any spike or excessive noise present on the Reset line may cause the mains flip–flop to be reset. In such cases, a ceramic filter capacitor should be provided near the Reset pin.

#### 2.4. The IM-Bus and Non-Volatile-Memory

It is by means of this part of the circuit that the TVPO 2066 communicates with the non-volatile memory (MDA 2062 or NVM 3060) which stores the tuning and analog data, acquired during the Memo procedure and the options. The IM-Bus consists of three lines Clock, Ident and Data. Clock and Ident are unidirectional signals from the TVPO 2066 to the memory (and to the VSP-processor in case of a digital TV set), and Data is bidirectional for transferring the data in both directions. In addition, the MDA 2062 (not the NVM 3060) requires a memory clock signal which is issued from the TVPO 2066 (approx. 1 kHz). All these signals on the IM-Bus have TTL level. In the nonoperative state all three bus lines are high. The start of a telegram is initiated when Ident and Data are low. Data takeover occurs at the positive edge of Clock. For a detailed description of the IM-Bus protocol please refer to the data sheet of the MDA 2062 or NVM 3060.

#### 2.5. The Clock Generator and the Sequence Control

For the purpose of generating the clock signals required to operate the TVPO 2066 the chip contains an oscillator which is designed for crystals in the frequency range from 3.5 to 4.5 MHz. For the exact requirement of "off-timer" and "sleep-timer" functions, a 4 MHz crystal is needed. The crystal is connected to the 'Xtal' input. All timing specification in this data sheet relate to a crystal frequency of 4 MHz. With other crystal frequencies, there will be corresponding variations.

#### 2.6. The D/A Converters for the Analog Outputs

The TVPO 2066 provides four analog outputs for adjustment of the TV's basic settings (e.g. volume and for analog TV sets additional brightness, contrast and color saturation). These control voltages are made available as pulse/pause modulated signals, where the ratio can be varied in 64 steps. The needed DC level signal is obtained by means of a simple RC lowpass filter.

#### 2.7. The Tuning Voltage Generator

The tuning voltage for the capacitance diodes of the TV tuner is generated as a pulse/interval modulated signal by a modified rate multiplier. The range of variation of the pulse/interval ratio extends from 0 (no pulses) to infinity (continuous signal) with a resolution of 4032 steps. At a clock frequency of 4 MHz the basic period of the rate multiplier is 0.5 ms which results in tolerable filter expenditure.

#### 2.8. The Ports

The TVPO 2066 has two ports (Port 2 and Port 3) which are used by the software versions as control outputs/inputs for a keyboard, band selection, multi–standard indicators, multi–video indicators and AFC switch.

The PLCC version of the TVPO 2066 has in addition four pins of Port 1 (P14...P17). The DIL version of the TVPO 2066 is also available in other pinnings: the D/A converter DA3 and DA4 can be exchanged to port input/outputs. DA3 to Port 1, Bit 5 (P15) and DA4 to Port 1, Bit 6 (P16). This possibility is very useful in digital TV sets, because in this case only one D/A converter is needed for volume control.

#### 2.9. The On-Screen Display

#### 2.9.1. Outputs and Inputs for the OSD

The OSD is an additional hardware module on the TVPO 2066 chip, which allows the display of 12 different characters such as the program number and analog val-

ues (volume, brightness etc.) on a TV screen. The TVPO 2066 software controls the OSD through a set of 16 external write registers.

The TVPO 2066 delivers four additional output signals:

| <ul><li>R_out</li></ul>    | character signal red   | (1 Vpp)     |

|----------------------------|------------------------|-------------|

| – G_out                    | character signal green | (1 Vpp)     |

| - B_out                    | character signal blue  | (1 Vpp)     |

| <ul><li>– FB_out</li></ul> | fast blanking          | (TTL level) |

Fast blanking is used for switching between video and OSD signals and shows the validity of the R, G, B outputs.

For synchronization and to place the display, the TVPO 2066 needs two additional input signals:

| – H_in | horizontal synchronization | (TTL level) |

|--------|----------------------------|-------------|

| – V_in | vertical synchronization   | (TTL level) |

#### 2.9.2. Display Format

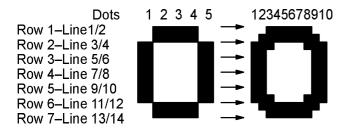

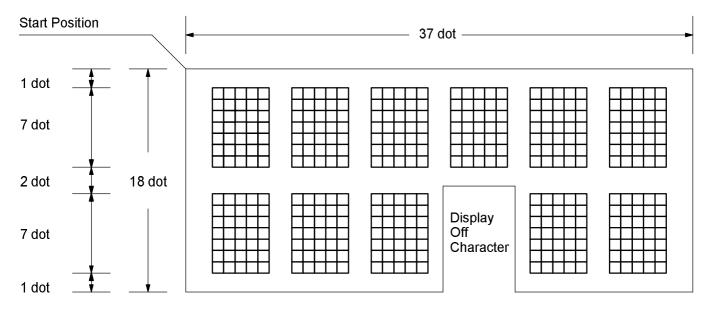

The OSD generates a rectangular display block, which contains 2 rows of 6 characters each (see Fig. 2–1). The characters are addressed depending on their position within this display block. Each address is attached to one TVPO 2066 register. The content of each register describes the character type and its color.

| 0000 | 1<br>0001 | 2<br>0010 | 3<br>0011 | 4<br>0100 | 5<br>0101 | (Hex)<br>(Bin) |

|------|-----------|-----------|-----------|-----------|-----------|----------------|

| 8    | 9         | A         | B         | C         | D         | (Hex)          |

| 1000 | 1001      | 1010      | 1011      | 1100      | 1101      | (Bin)          |

Fig. 2-1: On-Screen Display Block

A character is displayed in  $5 \times 7$  dot matrix format, which is stored in the character ROM. The size of one dot can be programmed to 4 different values (size = 1, 2, 3, 4).

- character format

- dot format vertical

- dot format horizontal

= 2 x 7 dot

= 2 lines x size

- dot format horizontal

T0 is the duration of one clock period of the system clock (CLK = 4 MHz  $\rightarrow$  T0 = 0.25 ns).

To make the characters easier to see without increasing the storage requirement, a smoothing algorithm is implemented. The space between two diagonal dots is filled with one pixel. Thus the character appears in a  $10 \times 14$  matrix format.

Fig. 2-2: Character smoothing

– pixel format vertical = 1 line x size

– pixel format horizontal = T0 x size

The horizontal space between two characters is 1 dot, the vertical space is 2 dots. A fringe of 1 dot lies around the 12 characters. The overall size of the display block is:

– block format vertical = 18 dot

– block format horizontal = 37 dot

The start position of the display's left, upper corner on the TV screen is specified by two registers and can be programmed in steps of 18 video lines, respectively 12 clock periods.

- start position vertical = 18 lines x Vpos

- start position horizontal =  $12 \times T0 \times Hpos$

#### 2.9.3. Display Control

The interface between TVPO 2066 and OSD consists of 16 external write registers in which the TVPO 2066 software can store the structure, size and position of the display (see also Table 3–1).

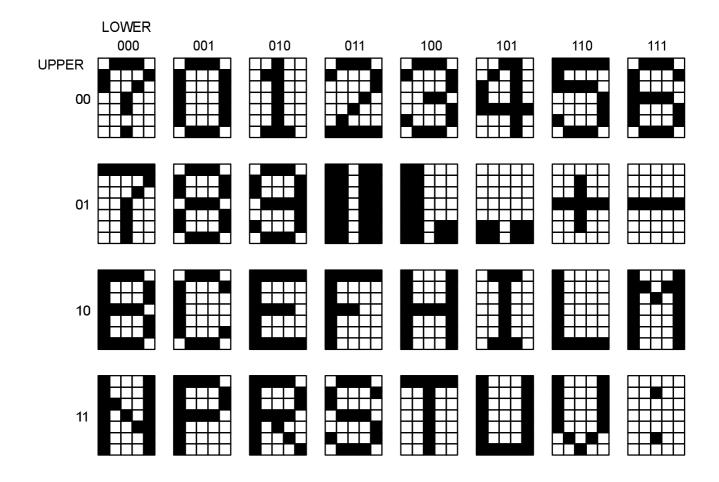

There are 32 different character types (C4...C0) in 8 colors (R, G, B) available. One special character is the 'display off code'. In this case the display is switched off for one character. The remaining 31 codes are used as address for the character ROM which stores 31 characters represented in a  $5 \times 7$  matrix format.

It is possible to use 3 kinds of background modes.

#### 1. No Background

Only the character itself is laid over the TV picture on those points where the character matrix are set. A blank character for instance is not visible.

#### 2. Square Background

The whole display block is visible in the desired background color. The characters differ from the background by use of another color. Only the 'display off code' switches off the background at the concerning character position.

#### 3. Fringe Background

This function creates a fringe of one pixel around and inside of each character. The color of the fringe is programmable. Only this fringe and the character itself is laid over the TV picture.

The display control bits are explained in the next chapter.

## 3. Description of Hardware Component Registers

**Table 3–1:** Registers of hardware components (x='0' or '1')

| Register                                                             | Register                                                                            |                                    |                                    |                                   | Fo                                    | rmat                                   |                                                                |                                              |                                         |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------|------------------------------------|-----------------------------------|---------------------------------------|----------------------------------------|----------------------------------------------------------------|----------------------------------------------|-----------------------------------------|

| Address                                                              | Contents                                                                            | 7                                  | 6                                  | 5                                 | 4                                     | 3                                      | 2                                                              | 1                                            | 0                                       |

| 1<br>2<br>3                                                          | IR-ADDR.<br>IR-COMM.<br>PORT3                                                       | CR<br>0<br>B7                      | 0<br>0<br>B6                       | 0<br>C5<br>B5                     | 0<br>C4<br>B4                         | A3<br>C3<br>B3                         | A2<br>C2<br>B2                                                 | A1<br>C1<br>B1                               | A0<br>C0<br>B0                          |

| 7<br>8<br>9<br>10                                                    | IMB-ADDR.<br>IMB-DATH<br>IMB-DATL<br>IMB-CTRL.                                      | A7<br>B15<br>B7<br>BB              | A6<br>B14<br>B6<br>x               | A5<br>B13<br>B5<br>x              | A4<br>B12<br>B4<br>x                  | A3<br>B11<br>B3<br>C3                  | A2<br>B10<br>B2<br>C2                                          | A1<br>B9<br>B1<br>C1                         | A0<br>B8<br>B0<br>C0                    |

| 11<br>12<br>13<br>16<br>17<br>18<br>19                               | TUNE-VL<br>TUNE-VH<br>MAINS-FF.<br>DAC 1<br>DAC 2<br>DAC 3<br>DAC 4                 | T3<br>T11<br>x<br>x<br>x<br>x<br>x | T2<br>T10<br>x<br>x<br>x<br>x<br>x | T1<br>T9<br>x<br>x<br>x<br>x<br>x | T0<br>T8<br>x<br>B4<br>B4<br>B4<br>B4 | x<br>T7<br>MOF<br>B3<br>B3<br>B3<br>B3 | x<br>T6<br>x<br>B2<br>B2<br>B2<br>B2                           | x<br>T5<br>x<br>B1<br>B1<br>B1               | x<br>T4<br>x<br>B0<br>B0<br>B0<br>B0    |

| 32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41<br>42<br>43 | CHAR 0 CHAR 1 CHAR 2 CHAR 3 CHAR 4 CHAR 5 CHAR 8 CHAR 9 CHAR A CHAR B CHAR C CHAR D | ~~~~~~~~~~~                        | 0000000000000                      | 888888888888                      | 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 | 88888888888888                         | C2<br>C2<br>C2<br>C2<br>C2<br>C2<br>C2<br>C2<br>C2<br>C2<br>C2 | C1<br>C1<br>C1<br>C1<br>C1<br>C1<br>C1<br>C1 | 888888888888888888888888888888888888888 |

| 44<br>45<br>46<br>47                                                 | SIZE/Vpos<br>Hpos<br>Mode<br>Test                                                   | S1<br>x<br>BGR<br>RO               | S0<br>x<br>BGG<br>GO               | x<br>x<br>BGB<br>BO               | X<br>H4<br>CRF<br>FBO                 | V3<br>H3<br>CR0<br>SM                  | V2<br>H2<br>SQ<br>T0                                           | V1<br>H1<br>FR<br>TM                         | V0<br>H0<br>DI<br>x                     |

#### 3.1. Registers for Infrared Control

Register 1: Infrared Address (READ only)

A0 ...A3: Address

CR : 0 = valid command received

1 = no command received

Register 2: Infrared Command (READ only)

C0...C5: Command

#### 3.2. Register for Port 3

Register 3: Port 3 (WRITE only)

B0...B7: Set status of port 3, Bit 0...7

#### 3.3. Registers for IM-Bus Control

Register 7: IM-Bus address (WRITE only)

A0...A7: IM-Bus address 0...255

Register 8: IM-Bus data high (READ/WRITE)

B8...B15: IM-Bus data, bit 8...15

Register 9: IM-Bus data low (READ/WRITE)

B0...B7: IM-Bus data, bit 0...7

Register 10: IM-Bus control (READ/WRITE)

C0...C3: IM-Bus control (READ/WRITE)

| C3               | C2               | C1          | C0               |                                |                                    |

|------------------|------------------|-------------|------------------|--------------------------------|------------------------------------|

| 1<br>1<br>1<br>0 | 1<br>1<br>0<br>1 | 0<br>1<br>1 | 1<br>0<br>1<br>1 | Read<br>Read<br>Write<br>Write | 8 bit<br>16 bit<br>8 bit<br>16 bit |

#### 3.4. Registers for Analog Outputs & MAINS-Control

Register 11: Tuning Voltage (WRITE only)

T0...T3: LSB's of DAC-Input

Register 12: Tuning Voltage (WRITE only)

T4...T11: MSB's of DAC-Input DAC worked with binary (dual) code Range is 0...4031 dec. = 0...FBF hex.

Register 13: Mains Flipflop (WRITE only)

MOF: Mains off

Register 16: Digital/Analog converter Output 1 (WRITE

B0...B5: Input of DAC1

Register 17: Digital/Analog converter Output 2 (WRITE

B0...B5: Input of DAC2

Register 18: Digital/Analog converter Output 3 (WRITE only)

B0...B5: Input of DAC3

Register 19: Digital/Analog converter Output 4 (WRITE

only)

B0...B5: Input DAC4

The DAC's of reg. 16...19 with a polynomial

code shown in Table 5-1.

#### 3.5. Registers for On-Screen Display

Register 32...43:C0...C4: Character to be displayed

R, G, B: RGB-color of character to be

displayed

Register 32: Character 0 of OSD (WRITE only)

Register 33: Character 1 of OSD (WRITE only)

Register 34: Character 2 of OSD (WRITE only)

Register 35: Character 3 of OSD (WRITE only)

Register 36: Character 4 of OSD (WRITE only)

Register 37: Character 5 of OSD (WRITE only)

Register 38: Character 8 of OSD (WRITE only)

Register 39: Character 9 of OSD (WRITE only)

Register 40: Character A of OSD (WRITE only)

Register 41:

Character B of OSD (WRITE only) Register 42: Character C of OSD (WRITE only)

Register 43: Character D of OSD (WRITE only)

OSD size and vertical position (WRITE only)

Register 44:

V0...V3: vertical position

S0...S1: size 1...4

Register 45: OSD horizontal position (WRITE only)

H0...H4: horizontal position

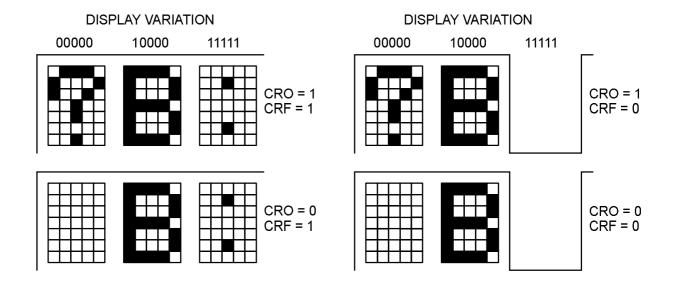

Register 46: OSD Mode (WRITE only)

CR0

: 0 = OSD off, 1 = OSD on

(set 0 by power–on reset)

SQ, FR: 00 = no background

01 = fringe background

1x = square background

: 1 = char. code 0 is 1st char.

0 = char. code 0 is blank

: 1 = char. code 1F is 32<sup>nd</sup> char CRF

0 = char. code 1F is display

: x = RGB, 1 of 8 background BGx

colors

Register 47: OSD Test (WRITE only)

: 1 = test mode on TM

(set 0 by power-on reset)

T0 : 0 = RGB-outp.sync

TVPO clock

1 = RGB-outp. sync to hor.

blanking

SM : 1 = Smoothing off

FB0 : 1 = Fast-Blank. output

disabled

: x = RGB 1 = RGB output x0

disabled

(all bits are set 0, if TM is set 0)

#### 4. Specifications

#### 4.1. Outline Dimensions

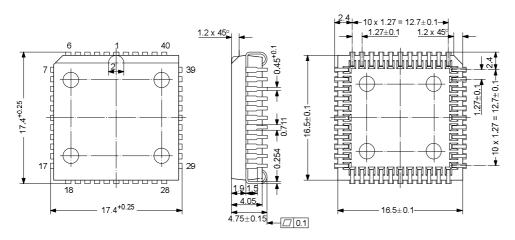

**Fig. 4–1:** TVPO 2066 in 40–pin DIL Package 20 B 40 according to DIN 41866

Weight approx. 6 g Dimensions in mm

**Fig. 4–2:** TVPO 2066 in 44–pin PLCC Package Weight approx. 2.2 g Dimensions in mm

#### 4.2. Pin Connections

#### 4.2.1. 40-Pin DIL Package

- 1 Vin: Vertical Blanking Pulse Input

- 2 Hin: Undel. Horizontal Blanking Pulse Input

- 3 DA3: Analog 3 Output (P15: Port P1, Bit 5)

- 4 DA4: Analog 4 Output (P16: Port P1, Bit 6)

- 5 P24: Port P2, Bit 4

- 6 P25: Port P2, Bit 5

- 7 P26: Port P2, Bit 6

- 8 P27: Port P2, Bit 7

- 9 Vstb: Standby Supply Voltage

- 10 GND: Ground, 0

- 11 Vsup: Supply Voltage

- 12 Xtal: Oscillator Input

- 13 T1: T1 Input

- 14 Clck: Memory Clock Output

- 15 Reset: Reset Input

- 16 Mains: Mains Switch Input/Output

- 17 EA (normally at GND)

# **TVPO 2066**

| 18    | IMD: IM Bus Data Input/Output      | 7  | P24: Port P2, Bit 4                         |

|-------|------------------------------------|----|---------------------------------------------|

| 19    | IMI: IM Bus Ident Output           | 8  | P17: Port P1, Bit 7                         |

| 20    | IMC: IM Bus Clock Output           | 9  | P16: Port P1, Bit 6                         |

| 21    | DA1: Analog 1 Output               | 10 | P15: Port P1, Bit 5                         |

| 22    | DA2: Analog 2 Output               | 11 | P14: Port P1, Bit 4                         |

| 23    | IR: Infrared Remote Control Input  | 12 | Hin: Undel. Horizontal Blanking Pulse Input |

| 24    | VS: Tuning Voltage Output          | 13 | Vin: Vertical Blanking Pulse Input          |

| 25    | P30: Port P3, Bit 0                | 14 | FB_out: Fast Blanking Pulse Output          |

| 26    | P31: Port P3, Bit 1                | 15 | B_out: BLUE Output                          |

| 27    | P32: Port P3, Bit 2                | 16 | G_out: GREEN Output                         |

| 28    | P33: Port P3, Bit 3                | 17 | R_out: RED Output                           |

| 29    | P34: Port P3, Bit 4                | 18 | P23: Port P2, Bit 3                         |

| 30    | P35: Port P3, Bit 5                | 19 | P22: Port P2, Bit 2                         |

| 31    | P36: Port P3, Bit 6                | 20 | P21: Port P2, Bit 1                         |

| 32    | P37: Port P3, Bit 7                | 21 | P20: Port P2, Bit 0                         |

| 33    | P20: Port P2, Bit 0                | 22 | P37: Port P3, Bit 7                         |

| 34    | P21: Port P2, Bit 1                | 23 | P36: Port P3, Bit 6                         |

| 35    | P22: Port P2, Bit 2                | 24 | P35: Port P3, Bit 5                         |

| 36    | P23: Port P2, Bit 3                | 25 | P34: Port P3, Bit 4                         |

| 37    | R_out: RED Output                  | 26 | P33: Port P3, Bit 3                         |

| 38    | G_out: GREEN Output                | 27 | P32: Port P3, Bit 2                         |

| 39    | B_out: BLUE Output                 | 28 | P31: Port P3, Bit 1                         |

| 40    | FB_out: Fast Blanking Pulse Output | 29 | P30: Port P3, Bit 0                         |

|       |                                    | 30 | VS: Tuning Voltage Output                   |

| 4.2.2 | 2. 44–Pin PLCC Package             | 31 | IR: Infrared Remote Control Input           |

| 1     | Vsup: Supply Voltage               | 32 | DA2: Analog 2 Output                        |

| 2     | GND: Ground, 0                     | 33 | DA1: Analog 1 Output                        |

| 3     | Vstb: Standby Supply Voltage       | 34 | DA4: Analog 4 Output                        |

| 4     | P27: Port P2, Bit 7                | 35 | DA3: Analog 3 Output                        |

| 5     | P26: Port P2, Bit 6                | 36 | IMC: IM Bus Clock Output                    |

| 6     | P25: Port P2, Bit 5                | 37 | IMI: IM Bus Ident Output                    |

|       |                                    |    |                                             |

38 IMD: IM Bus Data Input/Output

39 EA (normally at GND)

40 Mains: Mains Switch Input/Output

41 Reset Input

42 Clck: Memory Clock Output

43 T1: T1 Input

44 Xtal: Oscillator Input

#### 4.3. Pin Descriptions for 44-Pin PLCC

#### Pin 1 - Vsup

This pin must be connected to the positive of the 5 V supply.

#### Pin 2 - Ground

This pin must be connected to the negative of the supply.

#### Pin 3 – Vstb: Standby Supply pin +5 V

Via this pin, clock oscillator, reset circuit and remote—control decoder are powered. By means of this, it is possible to switch on the TV receiver by remote control. The standby consumption is very small.

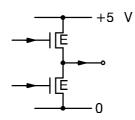

#### Pins 4 to 7, 8 to 21 – Port P2, Bits 0 to 7

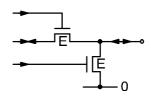

The internal configuration of these in/outputs is shown in Fig. 4–3. Direct data transfer with the  $\mu$ C can be executed via this port. The push–pull outputs drive one TTL gate.

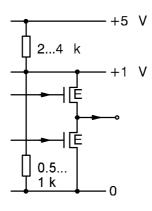

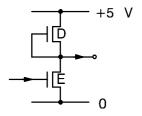

#### Pins 8 to 11 - Port P1, Bits 4 to 7

The internal configuration of these in/outputs is shown in Fig. 4–4. Direct data transfer with the  $\mu C$  can be executed via this port. The outputs are open–drain with a 12 V rating. Four outputs are available in the 44–pin PLCC package. In the 40–pin DIL package up to two P1–outputs (instead of analog outputs) are available by changing the bonding.

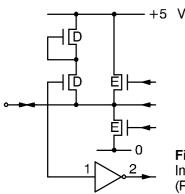

# Pins 12 and 13 – Vertical and Horizontal synchronization Inputs

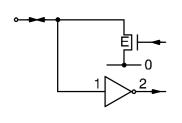

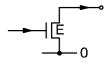

These inputs are shown in Fig. 4–5. They are used to synchronize the on–screen display. Negative pulses are needed. The internal delayed–clock–generator for the OSD section synchronizes to the positive edge of the Hin signal.

#### Pin 14 – Fast Blank Output

This output, which is shown in Fig. 4–6, is used to stop the normal display, and thus characters can be displayed on the screen.

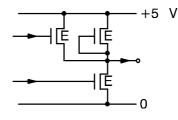

# Pins 15 to 17 – Video Outputs Red, Green and Blue (RGB)

These outputs are shown in Fig. 4-7 and used for on-

screen display outputs. Therefore, there are different colors to represent the output.

#### Pins 22 to 29 - Port P3, Bits 0 to 7

The diagram of these open—drain outputs is shown in Fig. 4–8. The voltage handling capability of Port—bits 0 and 1 (pins 28 and 29) is limited to Vsup, but supplies a high output current. The Port—bits 2 to 7 (pins 22 to 27) are outputs with a 12 V rating and a lower output current. In standby, bit 7 of P3 is grounded.

#### Pin 30 - Tuning Voltage Output

Fig. 4–9 shows the diagram of this push–pull output. Pin 30 supplies the tuning voltage for the capacitance diodes of the TV tuner in the shape of a pulsewidth–modulated signal. After amplification by an external transistor, the tuner DC voltage is derived by multiple RC filtering. A temperature–compensated Zener diode ZTK 33 must be provided for stabilizing the tuning voltage against variations of supply voltage and ambient temperature.

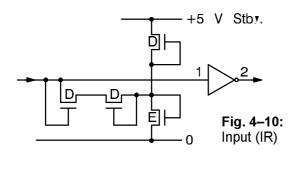

#### Pin 31 - IR: Remote-Control Input

The internal configuration of this pin is shown in Fig. 4–10. Via an external coupling capacitor of 10 nF, the remote–control signal, amplified by the TBA 2800 preamplifier IC, is fed to the remote–control decoder. The input is self–biasing to approximately 1.4 V, and the input DC resistance is approximately 150 kOhm. For highest input sensitivity, this pin must not be loaded resistively. A small capacitor connected from pin 31 to ground can be useful to suppress steep transients.

#### Pins 32 to 35 - Analog Outputs

These pins are open—drain outputs with diagram shown in Fig. 4–11. They supply the squarewave signals whose variable pulse/interval ratio is described in section 2.5. These signals serve for actuating the analog control elements. External pull—up resistors are required to produce the squarewave output signals.

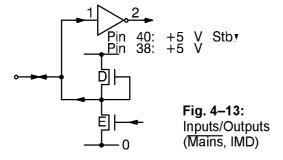

#### Pins 36 to 38 - IM Bus Connections

The internal configuration of these pins are shown in Figs. 4–12 and 4–13. Via these pins, the TVPO 2066 is connected to the IM bus (see section 2.3.). This bus interlinks the TVPO 2066 and the non–volatile memory. The ident and clock outputs are unidirectional (see Fig. 4–12). The data pin acts as input and output for reading and writing data (Fig. 4–13).

#### Pin 40 – Mains: Mains Switch Input/Output

The internal configuration of this input/output is shown in Fig. 4–13. Pin 40 represents the output of the mains flip–flop with a resistive pull–up. The output is active low (mains on). In the case of infrared remote control, this pin acts as output and drives an external switching amplifier, the mains relay, In the case of direct operation, this pin is used as input for switching on the TV receiver by means of an active low level applied to this pin, which sets the main flip–flop. More information is given in section 2.3.

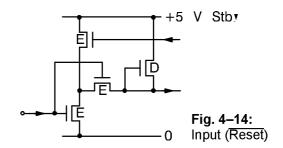

#### Pin 41 – Reset: Reset Input

The internal configuration of this input is shown in Fig. 4–14. The function of this pin is explained in section 2.4. The input circuit is of a Schmitt trigger configuration and provides some noise immunity. In critical applications, however, an additional ceramic capacitor, connected between this pin and GND, may be necessary to increase noise immunity.

# +5 V

Fig. 4–5: Inputs (Vin, Hin)

#### Pin 42 - Osc Out: fosc/4096 Output

The internal configuration of this output is shown in Fig. 4–15. This push–pull output provides the memory clock signal for the non–volatile memory MDA 2062 EEPROM (1 kHz). The drive capability of this pin is one TTL gate. This pin is not needed for the non–volatile memory NVM 3060.

Fig. 4–6: Output (Fast Blank)

#### Pin 43 – T1: T1 Input

This input can be used as timer input or normal input (e.g. to count the pulses of the horizontal frequency for autosearch function in analog TV sets). For more details about this input, see the CCU 2030, CCU 2050, CCU2070 data sheet.

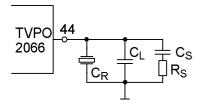

#### Pin 44 - Xtal: Oscillator Crystal

The internal configuration of this input/output is shown in Fig. 4–16. For normal use, a 4 MHz crystal is connected to this oscillator pin and to GND. The input is self-biasing to approximately 3.8 V, input DC resistance is approx. 350 kOhm. The output signal is the 4 MHz clock signal of the TVPO 2066.

Fig. 4–7: Outputs (RGB)

#### 4.4. Pin Circuits

Fig. 4–3: Inputs and Outputs (Port 2)

Fig. 4–8: Outputs (Port 3)

Fig. 4–4: Inputs and Outputs (Port 1)

Fig. 4-9: Output (VS)

Fig. 4–11: Outputs (DAC1...4)

Fig. 4–12: Outputs (IMC, IMI)

+5 V

Fig. 4–15:

Output (Mem Osc.)

Fig. 4-16: Oscillator (Xtal)

## 4.5. Electrical Characteristics

All voltages are referred to pin 2. Pins for 44-pin PLCC package.

## 4.5.1. Absolute Maximum Ratings

| Symbol            | Parameter                                          | Pin No.              | Min.         | Max.                                 | Unit     |

|-------------------|----------------------------------------------------|----------------------|--------------|--------------------------------------|----------|

| T <sub>A</sub>    | Ambient Operating Temperature                      | _                    | 0            | 65                                   | ∘C       |

| T <sub>S</sub>    | Storage Temperature                                | _                    | <b>-40</b>   | +125                                 | ∘C       |

| V <sub>SUP</sub>  | Supply Voltage                                     | 1                    | _            | 6                                    | V        |

| V <sub>Stby</sub> | Standby Voltage                                    | 3                    | _            | 6                                    | V        |

|                   | Output Voltages                                    |                      |              |                                      |          |

| $V_{P1O}$         | Port P1                                            | 8 to 11              | -0.3         | +13.5                                | V        |

| V <sub>P2O</sub>  | Port P2 Open Drain Configuration TTL Configuration | 4 to 7,<br>18 to 21  | -0.3<br>-0.3 | V <sub>SUP</sub><br>V <sub>SUP</sub> | V<br>V   |

| $V_{P3O}$         | Port P3, Bits 0 to 1<br>Bits 2 to 7                | 28 to 29<br>22 to 27 | -0.3<br>-0.3 | V <sub>SUP</sub><br>+13.5            | V<br>V   |

| $V_{AO}$          | Analog                                             | 32 to 35             | -0.3         | +13.5                                | V        |

| $V_{TO}$          | Tuning                                             | 30                   | -0.3         | V <sub>SUP</sub>                     | V        |

| $V_{IMO}$         | IM Bus                                             | 36 to 38             | -0.3         | $V_{SUP}$                            | V        |

| $V_{MO}$          | Mains                                              | 40                   | -0.3         | $V_{SUP}$                            | V        |

| V <sub>oo</sub>   | Oscillator                                         | 42                   | -0.3         | V <sub>SUP</sub>                     | V        |

|                   | Output Currents                                    |                      |              |                                      |          |

| I <sub>P10</sub>  | Port P1                                            | 8 to 11              | _            | 5                                    | mA       |

| I <sub>P2O</sub>  | Port P2 Open Drain Configuration TTL Configuration | 4 to 7,<br>18 to 21  | -<br>-2      | 5<br>5                               | mA<br>mA |

| I <sub>P3O</sub>  | Port P3                                            | 22 to 27<br>28, 29   | _<br>_       | 5<br>25                              | mA<br>mA |

| $I_{AO}$          | Analog                                             | 32 to 35             | _            | 5                                    | mA       |

| I <sub>TO</sub>   | Tuning<br>TTL Configuration                        | 30                   | <b>-</b> 2   | 5                                    | mA       |

| I <sub>IMO</sub>  | IM Bus<br>TTL Configuration                        | 36 to 38             | <b>-</b> 2   | 5                                    | mA       |

| I <sub>MO</sub>   | Mains<br>TTL Configuration                         | 40                   | <b>-</b> 2   | 5                                    | mA       |

| l <sub>00</sub>   | Oscillator<br>TTL Configuration                    | 42                   | <b>-</b> 2   | 5                                    | mA       |

| V <sub>I</sub>    | Input Voltages,                                    |                      |              |                                      |          |

| $V_{ln}$          | all Inputs except Pins 8 to 11                     |                      | -0.3         | V <sub>SUP</sub>                     | V        |

| $V_{IP1}$         | Port P1                                            | 8 to 11              | -0.3         | 13.5                                 | V        |

## 4.5.2. Recommended Operating Conditions

| Symbol                               | Parameter                                                                                                         | Pin No.            | Min.     | Тур.   | Max.                | Unit       |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------|----------|--------|---------------------|------------|

| V <sub>SUP</sub>                     | Supply Voltage                                                                                                    | 1                  | 4.75     | 5.0    | 5.25                | V          |

| V <sub>Stby</sub>                    | Standby Voltage                                                                                                   | 3                  | 4.75     | 5.0    | 5.25                | V          |

|                                      | Input Voltages                                                                                                    |                    |          |        |                     |            |

| V <sub>IRI</sub>                     | IR                                                                                                                | 31                 | 400      | -      | _                   | mVpp       |

| V <sub>MIL</sub>                     | Mains (active)                                                                                                    | 40                 | _        | _      | 0.8                 | V          |

|                                      | Reset                                                                                                             | 41                 |          |        |                     |            |

| V <sub>RIL</sub><br>V <sub>RIH</sub> | (active)<br>(inactive)                                                                                            |                    | _<br>1.8 | -<br>- | 0.8<br><del>-</del> | V<br>V     |

|                                      | All other inputs                                                                                                  |                    |          |        |                     |            |

| V <sub>nIH</sub><br>V <sub>nIL</sub> |                                                                                                                   |                    | 2.4<br>- | -<br>- | _<br>0.8            | V<br>V     |

| f <sub>cr</sub>                      | Clock Frequency                                                                                                   | 44                 | 3.5      | _      | 4.6                 | MHz        |

| f <sub>S</sub>                       | Ser. Resonance Freqency of the Crystal at C <sub>L</sub> = 20 pF                                                  |                    | 3.5      | -      | 4.6                 | MHz        |

| R <sub>r</sub>                       | Effective Series Resistance of the Crystal at $C_L = 20 \text{ pF}$ Equivalent Load Configuration (in addition to |                    | -        | -      | 60                  | Ω          |

|                                      | the crystal, see Fig. 4–17)                                                                                       |                    |          |        |                     |            |

| CL                                   | Load Capacitance                                                                                                  |                    | _        | _      | 3                   | pF         |

| C <sub>S</sub>                       | Series Load Capacitance                                                                                           |                    | _        | _      | 5                   | pF         |

| R <sub>S</sub>                       | Series Load Resistance                                                                                            |                    | 300      | _      | _                   | <b>k</b> Ω |

| C31                                  | Coupling Capacitor at Pin 31                                                                                      | 31                 | -        | 10     | _                   | nF         |

| CL                                   | Load Capacitance<br>at Pins 30 and 42<br>at Pins 14 to 17                                                         | 30, 42<br>14 to 17 | -<br>-   | -<br>- | 150<br>15           | pF<br>pF   |

Fig. 4–17: Maximum equivalent load configuration

# **TVPO 2066**

# **4.5.3. Characteristics** at $V_{SUP}$ = $V_{Stby}$ = 5 V, $T_A$ = 25 °C

| Sym-<br>bol                        | Parameter                              | Pin No.                                      | Min.                      | Тур.     | Max.            | Unit    | Test Conditions                                       |

|------------------------------------|----------------------------------------|----------------------------------------------|---------------------------|----------|-----------------|---------|-------------------------------------------------------|

|                                    | Current Consumption                    |                                              |                           |          |                 |         |                                                       |

| I <sub>SUP</sub>                   |                                        | 1                                            | _                         | 90       | 115             | mA      |                                                       |

| I <sub>Stby</sub>                  |                                        | 3                                            | _                         | 10       | 20              | mA      |                                                       |

|                                    | Output Voltages                        |                                              |                           |          |                 |         |                                                       |

|                                    | Port P2, FB<br>TTL Configuration       | 4 to 7, 14,<br>18 to 21                      |                           |          |                 |         |                                                       |

|                                    | Tuning, Osc.                           | 30, 42                                       |                           |          |                 |         |                                                       |

| V <sub>OH</sub><br>V <sub>OL</sub> |                                        |                                              | 2.7<br>-                  | -<br>-   | <b>-</b><br>0.4 | V<br>V  | -I <sub>OH</sub> = 100 μA<br>I <sub>OL</sub> = 1.6 mA |

|                                    | Port P1                                | 8 to 11                                      |                           |          |                 |         |                                                       |

|                                    | Port P3 Bits 2 to 7                    | 22 to 27                                     |                           |          |                 |         |                                                       |

|                                    | Analog                                 | 32 to 35                                     |                           |          |                 |         |                                                       |

| V <sub>OL</sub>                    |                                        |                                              | -                         | -        | 0.4             | V       | I <sub>OL</sub> = 4 mA                                |

| VoH                                | Port P3 Bits 0 and 1                   | 28 to 29                                     | -                         | _        | 0.5             | V       | I <sub>OL</sub> = 20 mA                               |

|                                    | RGB                                    | 15 to 17                                     |                           |          |                 |         |                                                       |

| V <sub>OH</sub><br>V <sub>OL</sub> |                                        |                                              | 0.8<br><del>-</del>       | 1.0<br>- | 1.2<br>100      | V<br>mV | -I <sub>OH</sub> = 25 μA<br>I <sub>OL</sub> = 25 μA   |

|                                    | IM Bus                                 | 36 to 38                                     |                           |          |                 |         |                                                       |

| V <sub>OH</sub><br>V <sub>OL</sub> |                                        |                                              | 2.7<br>-                  | -<br>-   | -<br>0.4        | V<br>V  | -I <sub>OH</sub> = 200 μA<br>I <sub>OL</sub> = 200 μA |

|                                    | Mains                                  | 40                                           |                           |          |                 |         |                                                       |

| VoH                                |                                        |                                              | V <sub>Stby</sub><br>–0.4 | _        | _               | V       | –I <sub>OH</sub> = 100 μA                             |

| V <sub>OL</sub>                    |                                        |                                              | _                         | _        | 1               | V       | I <sub>OL</sub> = 1.0 mA                              |

|                                    | Output Leakage Currents                |                                              |                           |          |                 |         |                                                       |

|                                    | Port P1                                | 8 to 11                                      |                           |          |                 |         |                                                       |

|                                    | Port P3 Bits 2 to 7                    | 22 to 27                                     |                           |          |                 |         |                                                       |

|                                    | Analog                                 | 32 to 35                                     |                           |          |                 |         |                                                       |

| I <sub>R</sub>                     |                                        |                                              | _                         | _        | 20              | μΑ      | V <sub>O</sub> = 12 V                                 |

| I <sub>R</sub>                     | Port P3 Bits 0 and 1                   | 28, 29                                       | _                         | _        | 20              | μΑ      | V <sub>O</sub> = 5 V                                  |

| -I <sub>K</sub>                    | Short Circuit Output Current<br>IM Bus | 36 to 38                                     | -                         |          | 2.8             | mA      | V <sub>O</sub> = 0                                    |

| Cl                                 | Input Capacitance                      | 12, 13                                       | _                         | 5        | _               | pF      |                                                       |

|                                    | Code of the Infrared<br>Transmitter    | see Data Sheets SAA 1250, IRT 1250, IRT 1260 |                           |          |                 |         |                                                       |

## 5. Appendix

## 5.1. DAC Poly-Counter Code

Table 5–1: DAC Poly–Counter Code

| Step | Code<br>[bin] | Code<br>[hex] | Step | Code<br>[bin] | Code<br>[hex] |

|------|---------------|---------------|------|---------------|---------------|

| 1    | 00111111      | 3F            | 33   | 00110110      | 36            |

| 2    | 00011111      | 1F            | 34   | 00011011      | 1B            |

| 3    | 00101111      | 2F            | 35   | 00101101      | 2D            |

| 4    | 00101111      | 37            | 36   | 00010110      | 16            |

| 5    | 0011011       | 3B            | 37   | 00001011      | 0B            |

| 6    | 00111101      | 3D            | 38   | 00100101      | 25            |

| 7    | 00011110      | 1E            | 39   | 00010010      | 12            |

| 8    | 00001111      | oF            | 40   | 00001001      | 09            |

| 9    | 00100111      | 27            | 41   | 00000100      | 04            |

| 10   | 00110011      | 33            | 42   | 00100010      | 22            |

| 11   | 00111001      | 39            | 43   | 00010001      | 11            |

| 12   | 00011100      | 1C            | 44   | 00001000      | 08            |

| 13   | 00101110      | 2E            | 45   | 00100100      | 24            |

| 14   | 00010111      | 17            | 46   | 00110010      | 32            |

| 15   | 00101011      | 2B            | 47   | 00011001      | 19            |

| 16   | 00110101      | 35            | 48   | 00001100      | 0C            |

| 17   | 00011010      | 1A            | 49   | 00100110      | 26            |

| 18   | 00001101      | 0D            | 50   | 00010011      | 13            |

| 19   | 00000110      | 06            | 51   | 00101001      | 29            |

| 20   | 00000011      | 03            | 52   | 00010100      | 14            |

| 21   | 00100001      | 21            | 53   | 00101010      | 2A            |

| 22   | 00010000      | 10            | 54   | 00010101      | 15            |

| 23   | 00101000      | 28            | 55   | 00001010      | 0A            |

| 24   | 00110100      | 24            | 56   | 00000101      | 15            |

| 25   | 00111010      | 3A            | 57   | 00000010      | 02            |

| 26   | 00011101      | 1D            | 58   | 00000001      | 01            |

| 27   | 00001110      | 0E            | 59   | 00000000      | 00            |

| 28   | 00000111      | 07            | 60   | 00100000      | 20            |

| 29   | 00100011      | 23            | 61   | 01100000      | 30            |

| 30   | 00110001      | 31            | 62   | 00111000      | 38            |

| 31   | 00011000      | 18            | 63   | 00111100      | 3C            |

| 32   | 00101100      | 2C            | 64   | 00111110      | 3E            |

## 5.2. On-Screen Display Format

Fig. 5-1: On-screen display format

#### 5.3. Character Set

#### Also available:

- character set 2: code 0EH = 'A' instead of '+' - character set 3: code 0EH = 'A' instead of '+'

- code 0FH = 'D' instead of ' '

#### 5.4. Programmed Versions of TVPO 2066

Some programmed versions of the TVPO 2066 are available (all versions use the non-volatile-memory NVM 3060):

TVPO 2066–A25 for analog TV–sets. With auto–searching of stations,

4 multi-standards, up to 99 stations, sleep-timer, Teletext with TPU 2735 with FLOF & exended characters (Spanish, Polish, Hungarian and Turkish).

#### - TVPO 2066-D03

for digital TV–sets. Along with the VSP 2860 and the VCU 2133 it offers a very economical solution of digital TV–sets (simple TV). Some features are 4 standards: PAL, NTSC, SECAM East/West, up to 99 stations, 3 video modes, auto–searching analog output for analog audio (volume) control and more.

Separate data sheets are available for analog and digital versions. Application diagrams will be found there. The last page shows an application diagram for analog TV–sets.

#### 5.5. User Options

If the manufacturer writes his own software for the TVPO 2066, he can choose some options by program mask or diffusion mask.

For explanation of the RESET option see section 2.3.

Table 5-2: Options

| Option                                                          | Default Setting                      | Alternative Setting                       |

|-----------------------------------------------------------------|--------------------------------------|-------------------------------------------|

| Reset                                                           | Reset 1                              | none or Reset 2                           |

| Port 2 configuration                                            | TTL                                  | open–drain                                |

| address and commands for power on in the remote–control decoder | address 16, commands 3, 1726, 35, 36 | up to 5 groups in a binary decoder matrix |

| Character set                                                   | Set 1                                | Set 2, Set 3 or customer specific setting |

**5.6. Application Circuit** (pin numbers for 40-pin DIL package)

ITT Semiconductors Group World Headquarters INTERMETALL Hans-Bunte-Strasse 19 D-7800 Freiburg Tel. (0761) 517-0, Telex 772 715 Telefax (0761) 517-174

Printed in Germany by A. Simon & Sohn, Freiburg (9/92) Order No. 6251-327-3E Reprinting is generally permitted, indicating the source. However, our consent must be obtained in all cases. Information furnished by ITT is believed to be accurate and reliable. However, no responsibility is assumed by ITT for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of ITT. The information and suggestions are given without obligation and cannot give rise to any liability; they do not indicate the availability of the components mentioned. Delivery of development samples does not imply any obligation of ITT to supply larger amounts of such units to a fixed term. To this effect, only written confirmation of orders will be binding.