TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

# TC74LCX652FS

#### Low-Voltage Octal Bus Transceiver/Register with 5-V Tolerant Inputs and Outputs

The TC74LCX652FS is a high-performance CMOS octal bus transceiver/register. Designed for use in 3.3-V systems, it achieves high-speed operation while maintaining the CMOS low power dissipation.

This device is designed for low-voltage (3.3 V) VCC applications, but it could be used to interface to 5-V supply environment for both inputs and outputs.

This device is bus transceiver with 3-state outputs, D-type flip-flops, and control circuitry arranged for multiplexed transmission of data directly from the internal registers.

All inputs are equipped with protection circuits against static discharge.

Weight: 0.14 g (typ.)

#### **Features**

- Low-voltage operation: V<sub>CC</sub> = 2.0 to 3.6 V

- High-speed operation:  $t_{pd} = 7.0 \text{ ns (max) (VCC} = 3.0 \text{ to } 3.6 \text{ V)}$

- Output current:  $|I_{OH}|/I_{OL} = 24 \text{ mA (min)} (V_{CC} = 3.0 \text{ V})$

- Latch-up performance: ±500 mA

- Available in SSOP

- Bidirectional interface between 5 V and 3.3 V signals

- Power-down protection provided on all inputs and outputs

- Pin and function compatible with the 74 series (74AC/F/ALS/LS etc.) 652 type

Note 1: Do not apply a signal to any bus pins when it is in the output mode. Damage may result.

All floating (high impedance) bus pins must have their input levels fixed by means of pull-up or pull-down resistors.

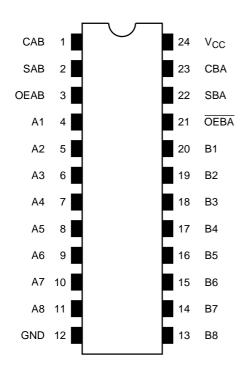

# Pin Assignment (top view)

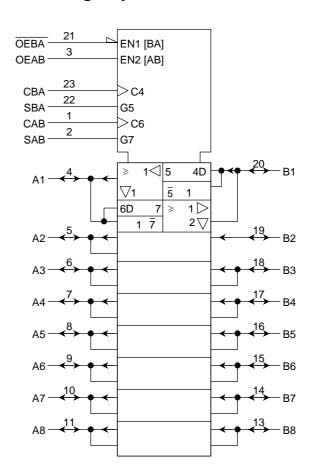

# **IEC Logic Symbol**

#### **Truth Table**

|      |      | Contro   | I Inputs |     |     | В      | us                     | Function                                                                                                                           |   |   |                                             |   |   |        |                                                   |  |

|------|------|----------|----------|-----|-----|--------|------------------------|------------------------------------------------------------------------------------------------------------------------------------|---|---|---------------------------------------------|---|---|--------|---------------------------------------------------|--|

| OEAB | OEBA | CAB      | CBA      | SAB | SBA | Α      | В                      | Function                                                                                                                           |   |   |                                             |   |   |        |                                                   |  |

|      |      | X*       | X*       | Х   | Х   | Input  | Input                  | The output functions of A and B busses are                                                                                         |   |   |                                             |   |   |        |                                                   |  |

|      |      | *        | ^.       | ^   | ^   | Z Z    |                        | disabled.                                                                                                                          |   |   |                                             |   |   |        |                                                   |  |

| L    | Н    | <b>\</b> |          | Х   | Х   | Х      | Х                      | Both A and B busses are used as inputs to the internal flip-flops. Data on the bus will be stored on the rising edge of the Clock. |   |   |                                             |   |   |        |                                                   |  |

|      |      |          |          |     |     | Input  | Output                 |                                                                                                                                    |   |   |                                             |   |   |        |                                                   |  |

|      |      | X*       | X*       | L   | X   | L      | L                      | The data on the A bus are displayed on the B bus.                                                                                  |   |   |                                             |   |   |        |                                                   |  |

|      |      |          |          |     |     | Н      | Н                      |                                                                                                                                    |   |   |                                             |   |   |        |                                                   |  |

|      |      | <b>↑</b> | X*       | L   | X   | L      | L                      | The data on the A bus are displayed on the                                                                                         |   |   |                                             |   |   |        |                                                   |  |

| н    | Н    |          | ^*       | L   | ^   | н      | Н                      | B bus, and are stored into the A storage flip-flops on the rising edge of CAB.                                                     |   |   |                                             |   |   |        |                                                   |  |

|      |      | X*       | X*       | Н   | Х   | х      | Qn                     | The data in the A storage flop-flops are displayed on the B bus.                                                                   |   |   |                                             |   |   |        |                                                   |  |

|      |      | _        |          |     |     |        |                        |                                                                                                                                    | L | L | The data on the A bus are stored into the A |   |   |        |                                                   |  |

|      |      | <b>_</b> | X*       | Н   | Х   | Н      | Н                      | storage flip-flops on the rising edge of CAB, and the stored data propagate directly onto the B bus.                               |   |   |                                             |   |   |        |                                                   |  |

|      |      |          |          |     | L   | L      | L                      | L                                                                                                                                  | L | L | L                                           | L |   | Output | Input                                             |  |

|      |      | X*       | X*       | X   |     |        |                        |                                                                                                                                    |   |   |                                             |   | L | L      | The data on the B bus are displayed on the A bus. |  |

|      |      |          |          |     |     | Н      | Н                      |                                                                                                                                    |   |   |                                             |   |   |        |                                                   |  |

|      |      | X*       | _        | Х   |     | L      | L The data on the B by | The data on the B bus are displayed on the                                                                                         |   |   |                                             |   |   |        |                                                   |  |

| L    | L    | Α**      |          | ^   | L   | Н      | Н                      | A bus, and are stored into the B storage flip-flops on the rising edge of CBA.                                                     |   |   |                                             |   |   |        |                                                   |  |

|      |      | X*       | X*       | Х   | Н   | Qn     | Х                      | The data in the B storage flip-flops are displayed on the A bus.                                                                   |   |   |                                             |   |   |        |                                                   |  |

|      |      |          | <b>↑</b> |     |     | L      | L                      | The data on the B bus are stored into the B                                                                                        |   |   |                                             |   |   |        |                                                   |  |

|      |      | X*       |          | X   | Н   | н      | н                      | storage flip-flops on the rising edge of CBA,<br>and the stored data propagate directly onto<br>the A bus.                         |   |   |                                             |   |   |        |                                                   |  |

|      |      |          |          |     |     | Output | Output                 |                                                                                                                                    |   |   |                                             |   |   |        |                                                   |  |

| н    | L    | X*       | X*       | н   | н   | Qn     | Qn                     | The data in the A storage flop-flops are displayed on the B bus, and the data in the B storage flop-flops are displayed on the A.  |   |   |                                             |   |   |        |                                                   |  |

X: Don't care

Z: High impedance

Qn: The data stored into the internal flip-flops by most recent low to high transition of the clock inputs.

\*: The clocks are not internally gated with either OEAB or  $\overline{\text{OEBA}}$ .

Therefore, data on the A and/or B busses may be clocked into the storage flip-flops at any time.

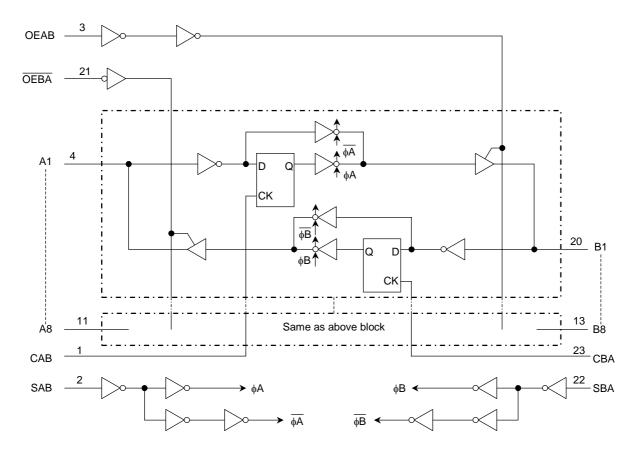

# **System Diagram**

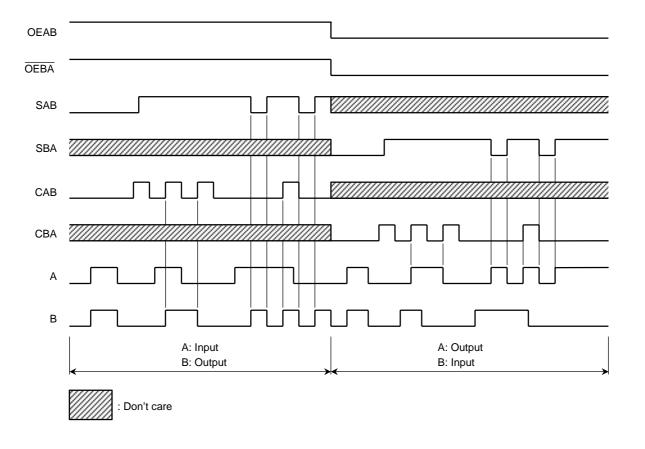

# **Timing Chart**

### **Maximum Ratings**

| Characteristics                                      | Symbol                            | Rating                        | Unit |  |

|------------------------------------------------------|-----------------------------------|-------------------------------|------|--|

| Power supply voltage                                 | V <sub>CC</sub>                   | −0.5 to 7.0                   | V    |  |

| DC input voltage<br>(CAB, CBA, SAB, SBA, OEAB, OEBA) | V <sub>IN</sub>                   | -0.5 to 7.0                   | V    |  |

|                                                      |                                   | -0.5 to 7.0 (Note 2)          |      |  |

| DC bus I/O voltage                                   | V <sub>I/O</sub>                  | -0.5 to V <sub>CC</sub> + 0.5 | V    |  |

|                                                      |                                   | (Note 3)                      |      |  |

| Input diode current                                  | I <sub>IK</sub>                   | -50                           | mA   |  |

| Output diode current                                 | lok                               | ±50 (Note 4)                  | mA   |  |

| DC output current                                    | lout                              | ±50                           | mA   |  |

| Power dissipation                                    | $P_{D}$                           | 180                           | mW   |  |

| DC V <sub>CC</sub> /ground current                   | I <sub>CC</sub> /I <sub>GND</sub> | ±100                          | mA   |  |

| Storage temperature                                  | T <sub>stg</sub>                  | -65 to 150                    | °C   |  |

Note 2: Output in OFF state

Note 3: High or low state. I<sub>OUT</sub> absolute maximum rating must be observed.

Note 4:  $V_{OUT} < GND, V_{OUT} > V_{CC}$

## **Recommended Operating Conditions**

| Characteristics                                   | Symbol                           | Rating                        | Unit |  |

|---------------------------------------------------|----------------------------------|-------------------------------|------|--|

| Power supply voltage                              | V                                | 2.0 to 3.6                    | V    |  |

| Fower supply voltage                              | V <sub>CC</sub>                  | 1.5 to 3.6 (Note 5)           | V    |  |

| Input voltage<br>(CAB, CBA, SAB, SBA, OEAB, OEBA) | V <sub>IN</sub>                  | 0 to 5.5                      | V    |  |

| Bus I/O voltage                                   | V                                | 0 to 5.5 (Note 6)             | V    |  |

| Bus I/O Voltage                                   | V <sub>I/O</sub>                 | 0 to V <sub>CC</sub> (Note 7) | V    |  |

| Output current                                    | la/la.                           | ±24 (Note 8)                  | mA   |  |

| Output current                                    | I <sub>OH</sub> /I <sub>OL</sub> | ±12 (Note 9)                  | ША   |  |

| Operating temperature                             | T <sub>opr</sub>                 | -40 to 85                     | °C   |  |

| Input rise and fall time                          | dt/dv                            | 0 to 10 (Note 10)             | ns/V |  |

Note 5: Data retention only

Note 6: Output in OFF state

Note 7: High or low state

Note 8:  $V_{CC} = 3.0 \text{ to } 3.6 \text{ V}$

Note 9:  $V_{CC} = 2.7 \text{ to } 3.0 \text{ V}$

Note 10:  $V_{IN} = 0.8$  to 2.0 V,  $V_{CC} = 3.0$  V

5

TC74LCX652FS

### **Electrical Characteristics**

# DC Characteristics ( $Ta = -40 \text{ to } 85^{\circ}\text{C}$ )

| Characteristics                  |            | Symbol                                          | Test Condition                                       |                           |                     | Min                      | Max   | Unit |

|----------------------------------|------------|-------------------------------------------------|------------------------------------------------------|---------------------------|---------------------|--------------------------|-------|------|

|                                  |            |                                                 |                                                      |                           | V <sub>CC</sub> (V) |                          |       |      |

| Input voltage                    | H-level    | V <sub>IH</sub>                                 | _                                                    |                           | 2.7 to 3.6          | 2.0                      | —     | V    |

| input voltage                    | L-level    | V <sub>IL</sub>                                 | _                                                    |                           | 2.7 to 3.6          |                          | 0.8   | V    |

|                                  |            | V <sub>OH</sub>                                 |                                                      | $I_{OH} = -100 \ \mu A$   | 2.7 to 3.6          | V <sub>CC</sub><br>- 0.2 | _     | V    |

|                                  | H-level    |                                                 | V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | $I_{OH} = -12 \text{ mA}$ | 2.7                 | 2.2                      |       |      |

|                                  |            |                                                 |                                                      | $I_{OH} = -18 \text{ mA}$ | 3.0                 | 2.4                      | _     |      |

| Output voltage                   |            |                                                 |                                                      | $I_{OH} = -24 \text{ mA}$ | 3.0                 | 2.2                      | _     |      |

|                                  | I lavel    |                                                 | $V_{IN} = V_{IH}$ or $V_{IL}$                        | I <sub>OL</sub> = 100 μA  | 2.7 to 3.6          | _                        | 0.2   |      |

|                                  |            |                                                 |                                                      | I <sub>OL</sub> = 12 mA   | 2.7                 | _                        | 0.4   |      |

|                                  | L-level    | VoL                                             |                                                      | I <sub>OL</sub> = 16 mA   | 3.0                 | _                        | 0.4   |      |

|                                  |            |                                                 |                                                      | I <sub>OL</sub> = 24 mA   | 3.0                 | _                        | 0.55  |      |

| Input leakage current            |            | I <sub>IN</sub>                                 | V <sub>IN</sub> = 0 to 5.5 V                         |                           | 2.7 to 3.6          | _                        | ±5.0  | μΑ   |

| 2 state sutput OFF sta           | to ourront | 1                                               | $V_{IN} = V_{IH}$ or $V_{IL}$                        |                           | 0.74-0.0            |                          | .5.0  |      |

| 3-state output OFF state current |            | loz                                             | V <sub>OUT</sub> = 0 to 5.5 V                        |                           | 2.7 to 3.6          | _                        | ±5.0  | μА   |

| Power-off leakage current        |            | I <sub>OFF</sub>                                | V <sub>IN</sub> /V <sub>OUT</sub> = 5.5 V            |                           | 0                   | _                        | 10.0  | μА   |

| Quiescent supply current         |            | l                                               | V <sub>IN</sub> = V <sub>CC</sub> or GND             |                           | 2.7 to 3.6          | _                        | 10.0  |      |

|                                  |            | $I_{CC}$ $V_{IN}/V_{OUT} = 3.6 \text{ to } 5.5$ |                                                      | 5 V                       | 2.7 to 3.6          | _                        | ±10.0 | μΑ   |

| Increase in Icc per input        |            | Δl <sub>CC</sub>                                | $V_{IH} = V_{CC} - 0.6 V$                            |                           | 2.7 to 3.6          | _                        | 500   |      |

#### AC Characteristics ( $Ta = -40 \text{ to } 85^{\circ}\text{C}$ )

| Characteristics S       |                                 | Test Condition               |                     | Min | Max | Unit |

|-------------------------|---------------------------------|------------------------------|---------------------|-----|-----|------|

|                         |                                 |                              | V <sub>CC</sub> (V) |     |     |      |

| Maximum clock frequency | f <sub>max</sub>                | Figure 1, Figure 2           | 2.7                 | _   | —   | MHz  |

|                         | max                             | 3 , 3                        | $3.3 \pm 0.3$       | 150 |     |      |

| Propagation delay time  | t <sub>pLH</sub>                | Figure 1, Figure 2           | 2.7                 | _   | 8.0 | ns   |

| (An, Bn-Bn, An)         | t <sub>pHL</sub>                | Figure 1, Figure 2           | $3.3 \pm 0.3$       | 1.5 | 7.0 |      |

| Propagation delay time  | t <sub>pLH</sub>                | Figure 4 Figure 5            | 2.7                 | _   | 9.5 |      |

| (CAB, CBA-Bn, An)       | t <sub>pHL</sub>                | Figure 1, Figure 5           | $3.3 \pm 0.3$       | 1.5 | 8.5 | ns   |

| Propagation delay time  | t <sub>pLH</sub>                | F: 4 F: 0                    | 2.7                 |     | 9.5 |      |

| (SAB, SBA-Bn, An)       | t <sub>pHL</sub>                | Figure 1, Figure 2           | $3.3 \pm 0.3$       | 1.5 | 8.5 | ns   |

| Output enable time      | t <sub>pZL</sub>                | Figure 4 Figure 2 Figure 4   | 2.7                 | _   | 9.5 |      |

| (OEAB, OEBA -An, Bn)    | r) Figure 1, Figure 3, Figure 4 | $3.3 \pm 0.3$                | 1.5                 | 8.5 | ns  |      |

| Output disable time     | t <sub>pLZ</sub>                | Figure 1, Figure 3, Figure 4 | 2.7                 | _   | 9.5 | ns   |

| (OEAB, OEBA -An, Bn)    | t <sub>pHZ</sub>                |                              | $3.3 \pm 0.3$       | 1.5 | 8.5 |      |

| Minimum nula a width    | t <sub>W</sub> (H)              | Figure 1, Figure 5           | 2.7                 | 3.3 | _   | - ns |

| Minimum pulse width     | t <sub>W</sub> (L)              |                              | $3.3 \pm 0.3$       | 3.3 | _   |      |

| Minimum setup time      | 4                               | Figure 4 Figure 5            | 2.7                 | 2.5 | _   |      |

| Minimum setup time      | t <sub>s</sub>                  | Figure 1, Figure 5           | $3.3 \pm 0.3$       | 2.5 | _   | ns   |

| Minimum hold time       | 4.                              | E. 1 E. E                    | 2.7                 | 1.5 | _   | 20   |

| Minimum noid time       | th                              | Figure 1, Figure 5           | $3.3 \pm 0.3$       | 1.5 | _   | ns   |

| Output to output alrays | t <sub>osLH</sub>               | (Note 11)                    | 2.7                 | _   | _   | 20   |

| Output to output skew   | t <sub>osHL</sub>               |                              | $3.3 \pm 0.3$       | _   | 1.0 | ns   |

Note 11: Parameter guaranteed by design.  $(t_{OSLH} = |t_{DLHm} - t_{DLHn}|, t_{OSHL} = |t_{DHLm} - t_{DHLn}|)$

#### **Dynamic Switching Characteristics**

(Ta = 25°C, input:  $t_r = t_f = 2.5 \text{ ns}$ ,  $C_L = 50 \text{ pF}$ ,  $R_L = 500 \Omega$ )

| Characteristics                              | Symbol           | Test Condition                                          | V <sub>CC</sub> (V) | Тур. | Unit |

|----------------------------------------------|------------------|---------------------------------------------------------|---------------------|------|------|

| Quiet output maximum dynamic V <sub>OL</sub> | V <sub>OLP</sub> | $V_{IH} = 3.3 \text{ V}, V_{IL} = 0 \text{ V}$ (Note 1  | 2) 3.3              | 0.8  | V    |

| Quiet output minimum dynamic V <sub>OL</sub> | V <sub>OLV</sub> | $V_{IH} = 3.3 \text{ V}, V_{IL} = 0 \text{ V}$ (Note 1) | 2) 3.3              | 0.8  | V    |

Note 12: Characterized with 7 outputs switching from high-to-low or low-to- high. The remaining output is measured in the low state.

#### **Capacitive Characteristics (Ta = 25°C)**

| Characteristics               | Symbol           | Test Condition                 |           | V <sub>CC</sub> (V) | Тур. | Unit |

|-------------------------------|------------------|--------------------------------|-----------|---------------------|------|------|

| Input capacitance             | C <sub>IN</sub>  | OEAB, OEBA, CAB, CBA, SAB, SBA |           | 3.3                 | 7    | pF   |

| Bus input capacitance         | C <sub>I/O</sub> | An, Bn                         |           | 3.3                 | 8    | pF   |

| Power dissipation capacitance | C <sub>PD</sub>  | f <sub>IN</sub> = 10 MHz       | (Note 13) | 3.3                 | 25   | pF   |

Note 13: C<sub>PD</sub> is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption without load.

7

Average operating current can be obtained by the equation:

$I_{CC (opr)} = C_{PD} \cdot V_{CC} \cdot f_{IN} + I_{CC}/8 \text{ (per bit)}$

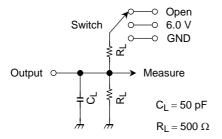

#### **AC Test Circuit**

| Parameter                                                           | Switch |

|---------------------------------------------------------------------|--------|

| t <sub>pLH</sub> , t <sub>pHL</sub>                                 | Open   |

| $t_{pLZ}, t_{pZL}$                                                  | 6.0 V  |

| t <sub>pHZ</sub> , t <sub>pZH</sub>                                 | GND    |

| t <sub>w</sub> , t <sub>s</sub> , t <sub>h</sub> , f <sub>max</sub> | Open   |

Figure 1

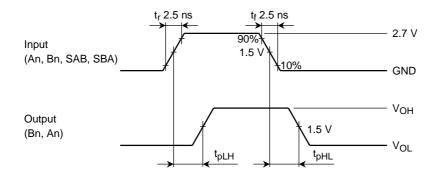

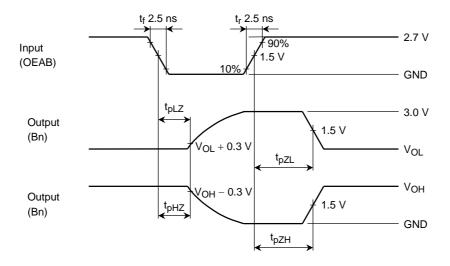

#### **AC Waveform**

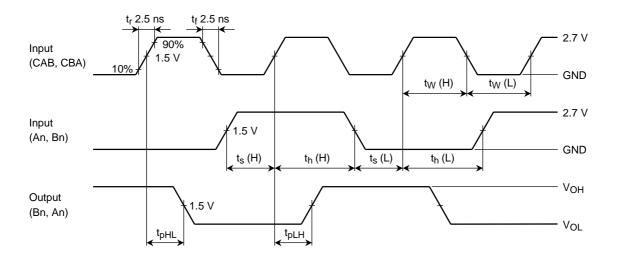

Figure 2 t<sub>pLH</sub>, t<sub>pHL</sub>

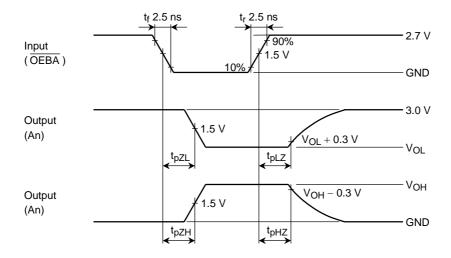

$Figure \ 3 \quad t_{pLZ}, \, t_{pHZ}, \, t_{pZL}, \, t_{pZH}$

8

Figure 4  $t_{pLZ}, t_{pHZ}, t_{pZL}, t_{pZH}$

$\label{eq:figure 5} \textbf{Figure 5} \quad t_{pLH},\,t_{pHL},\,t_{w},\,t_{s},\,t_{h}$

0.45±0.2

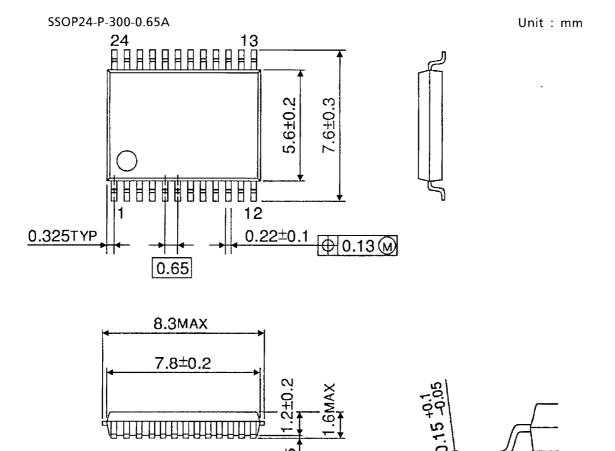

# **Package Dimensions**

Weight: 0.14 g (typ.)

#### **RESTRICTIONS ON PRODUCT USE**

000707EBA

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

- The information contained herein is subject to change without notice.