March 2007

# FAN7602B Green Current-Mode PWM Controller

#### **Features**

- Green Current-Mode PWM Control

- Fixed 65kHz Operation

- Internal High-Voltage Start-up Switch

- Burst-Mode Operation

- Line Voltage Feedforward to Limit Maximum Power

- Line Under-Voltage Protection

- Latch Protection & Internal Soft-Start (10ms) Function

- Overload Protection

- Over-Voltage Protection

- Low Operation Current: 1mA Typical

- 8-pin DIP/SOP

# **Applications**

- Adapter

- LCD Monitor Power

- Auxiliary Power Supply

# **Related Application Notes**

■ AN6014 - Green Current Mode PWM Controller FAN7602

## **Description**

The FAN7602B is a green current-mode PWM controller. It is specially designed for off-line adapter applications; DVDP, VCR, LCD monitor applications; and auxiliary power supplies.

The internal high-voltage start-up switch and the burst-mode operation reduce the power loss in standby mode. As a result, it is possible to supply 0.5W load, limiting the input power under 1W when the input line voltage is 265V<sub>AC</sub>. On no-load condition, input power is under 0.3W.

The maximum power can be limited constantly, regardless of the line voltage change, using the power limit function.

The switching frequency is internally fixed at 65kHz.

The FAN7602B includes various protections for the system reliability and the internal soft-start prevents the output voltage over-shoot at start-up.

# **Ordering Information**

| Part Number | Operating Temp.<br>Range | Pb-Free | Package | Packing Method | Marking<br>Code |

|-------------|--------------------------|---------|---------|----------------|-----------------|

| FAN7602BN   |                          |         | 8-DIP   | Rail           | FAN7602B        |

| FAN7602BM   | -25°C to +125°C          | Yes     | 8-SOP   | Rail           | FAN7602B        |

| FAN7602BMX  |                          |         | 0-3UF   | Tape & Reel    | FAN7602B        |

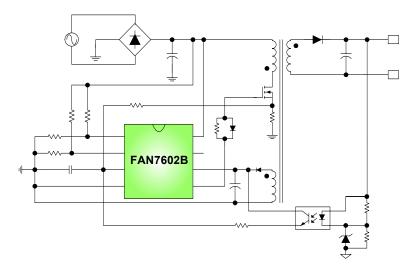

# **Typical Application Diagram**

Figure 1. Typical Flyback Application

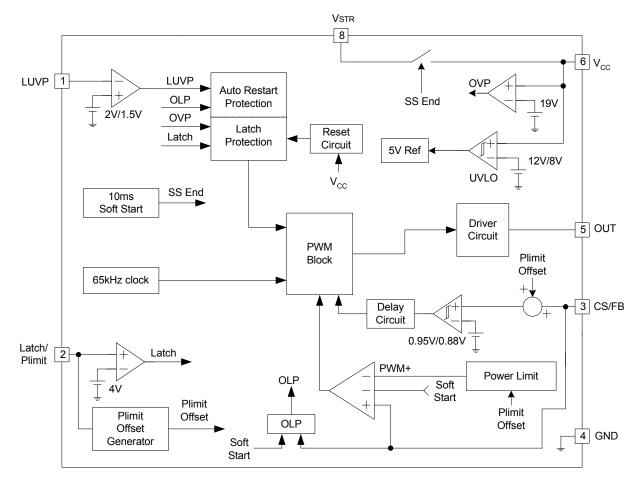

# **Internal Block Diagram**

Figure 2. Functional Block Diagram of FAN7602B

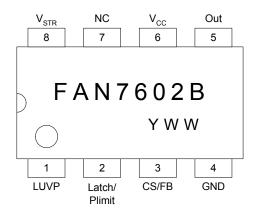

# **Pin Assignments**

Figure 3. Pin Configuration (Top View)

# **Pin Definitions**

| Pin# | Name             | Description                                                                                                                                                                                                                                                              |

|------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | LUVP             | <b>Line Under-Voltage Protection Pin</b> . This pin is used to protect the set when the input voltage is lower than the rated input voltage range.                                                                                                                       |

| 2    | Latch/Plimit     | <b>Latch Protection and Power Limit Pin</b> . When the pin voltage exceeds 4V, the latch protection works; the latch protection is reset when the $V_{CC}$ voltage is lower than 5V. For the power limit function, the OCP level decreases as the pin voltage increases. |

| 3    | CS/FB            | <b>Current Sense and Feedback Pin</b> . This pin is used to sense the MOSFET current for the current mode PWM and OCP. The output voltage feedback information and the current sense information are added using an external RC filter.                                  |

| 4    | GND              | <b>Ground Pin</b> . This pin is used for the ground potential of all the pins. For proper operation, the signal ground and the power ground should be separated.                                                                                                         |

| 5    | OUT              | <b>Gate Drive Output Pin.</b> This pin is an output pin to drive an external MOSFET. The peak sourcing current is 450mA and the peak sinking current is 600mA. For proper operation, the stray inductance in the gate driving path must be minimized.                    |

| 6    | V <sub>CC</sub>  | <b>Supply Voltage Pin</b> . IC operating current and MOSFET driving current are supplied using this pin.                                                                                                                                                                 |

| 7    | NC               | No Connection.                                                                                                                                                                                                                                                           |

| 8    | V <sub>STR</sub> | <b>Start-up Pin.</b> This pin is used to supply IC operating current during IC start-up. After start-up, the internal JFET is turned off to reduce power loss.                                                                                                           |

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol                            | Parameter                            | Value      | Unit |

|-----------------------------------|--------------------------------------|------------|------|

| V <sub>CC</sub>                   | Supply Voltage                       | 20         | V    |

| I <sub>OH</sub> , I <sub>OL</sub> | Peak Drive Output Current            | +450/-600  | mA   |

| V <sub>CS/FB</sub>                | CS/FB Input Voltage                  | -0.3 to 20 | V    |

| V <sub>LUVP</sub>                 | LUVP Input Voltage                   | -0.3 to 10 | V    |

| V <sub>Latch</sub>                | Latch/Plimit Input Voltage           | -0.3 to 10 | V    |

| V <sub>STR</sub>                  | V <sub>STR</sub> Input Voltage       | 600        | V    |

| T <sub>J</sub>                    | Operating Junction Temperature       | 150        | °C   |

| T <sub>A</sub>                    | Operating Temperature Range          | -25 to 125 | °C   |

| T <sub>STG</sub>                  | Storage Temperature Range            | -55 to 150 | °C   |

| $P_{D}$                           | Power Dissipation                    | 1.2        | W    |

| V <sub>ESD_HBM</sub>              | ESD Capability, Human Body Model     | 2.0        | kV   |

| V <sub>ESD_MM</sub>               | ESD Capability, Machine Model        | 200        | V    |

| V <sub>ESD_CDM</sub>              | ESD Capability, Charged Device Model | 500        | V    |

# **Thermal Impedance**

| Symbol            | Parameter                               |       | Value | Unit |

|-------------------|-----------------------------------------|-------|-------|------|

| $\theta_{\sf JA}$ | Thermal Resistance, Junction-to-Ambient | 8-DIP | 100   | °C/W |

#### Note:

1. Regarding the test environment and PCB type, please refer to JESD51-2 and JESD51-10.

# **Electrical Characteristics**

$V_{CC}$  = 14V,  $T_A$  = -25°C~125°C, unless otherwise specified

| Symbol                  | Parameter                                  | Condition                                             | Min. | Тур.     | Max. | Unit     |

|-------------------------|--------------------------------------------|-------------------------------------------------------|------|----------|------|----------|

| START UP                | SECTION                                    |                                                       |      |          |      | •        |

| I <sub>STR</sub>        | V <sub>STR</sub> Start-up Current          | V <sub>STR</sub> = 30V, T <sub>A</sub> = 25°C         | 0.7  | 1.0      | 1.4  | mA       |

| UNDER VO                | OLTAGE LOCK OUT SECTION                    |                                                       |      |          |      | •        |

| V <sub>th</sub> (start) | Start Threshold Voltage                    | V <sub>CC</sub> increasing                            | 11   | 12       | 13   | V        |

| V <sub>th</sub> (stop)  | Stop Threshold Voltage                     | V <sub>CC</sub> decreasing                            | 7    | 8        | 9    | V        |

| HY(uvlo)                | UVLO Hysteresis                            |                                                       | 3.6  | 4.0      | 4.4  | V        |

| SUPPLY C                | URRENT SECTION                             |                                                       | •    | •        | •    |          |

| I <sub>STR</sub>        | Start-up Supply Current                    | T <sub>A</sub> = 25°C                                 |      | 250      | 320  | μΑ       |

| I <sub>CC</sub>         | Operating Supply Current                   | Output no switching                                   |      | 1.0      | 1.5  | mA       |

| SOFT-STA                | RT SECTION                                 |                                                       | •    | ·        | •    |          |

| t <sub>SS</sub>         | Soft-Start Time <sup>(1)</sup>             |                                                       | 5    | 10       | 15   | ms       |

| PWM SEC                 | TION                                       | I                                                     | 1    | I.       | 1    | ı        |

| f <sub>OSC</sub>        | Operating Frequency                        | V <sub>CS/FB</sub> = 0.2V, T <sub>A</sub> = 25°C      | 59   | 65       | 73   | kHz      |

| V <sub>CS/FB1</sub>     | CS/FB Threshold Voltage                    | T <sub>A</sub> = 25°C                                 | 0.9  | 1.0      | 1.1  | V        |

| t <sub>D</sub>          | Propagation Delay to Output <sup>(1)</sup> |                                                       |      | 100      | 150  | ns       |

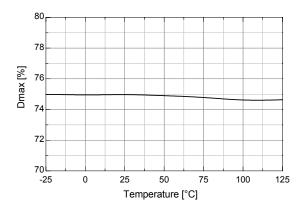

| D <sub>MAX</sub>        | Maximum Duty Cycle                         |                                                       | 70   | 75       | 80   | %        |

| D <sub>MIN</sub>        | Minimum Duty Cycle                         |                                                       |      |          | 0    | %        |

| BURST MO                | DDE SECTION                                |                                                       |      | I        |      | I        |

| V <sub>CS/FB2</sub>     | Burst On Threshold Voltage                 | T <sub>A</sub> = 25°C                                 | 0.84 | 0.95     | 1.06 | V        |

| V <sub>CS/FB3</sub>     | Burst Off Threshold Voltage                | T <sub>A</sub> = 25°C                                 | 0.77 | 0.88     | 0.99 | V        |

|                         | MIT SECTION                                |                                                       | 1    | <u> </u> | 1    | l        |

| K <sub>Plimit</sub>     | Offset Gain                                | V <sub>Latch/Plimit</sub> = 2V, T <sub>A</sub> = 25°C | 0.12 | 0.16     | 0.20 |          |

| OUTPUT S                | ECTION                                     |                                                       | 1    |          | 1    | <u>l</u> |

| V <sub>OH</sub>         | Output Voltage High                        | T <sub>A</sub> = 25°C, I <sub>source</sub> = 100mA    | 11.5 | 12.0     | 14.0 | V        |

| V <sub>OL</sub>         | Output Voltage Low                         | T <sub>A</sub> = 25°C, I <sub>sink</sub> = 100mA      |      | 1.0      | 2.5  | V        |

| t <sub>R</sub>          | Rising Time <sup>(1)</sup>                 | T <sub>A</sub> = 25°C, C <sub>L</sub> = 1nF           |      | 45       | 150  | ns       |

| t <sub>F</sub>          | Falling Time <sup>(1)</sup>                | T <sub>A</sub> = 25°C, C <sub>L</sub> = 1nF           |      | 35       | 150  | ns       |

| PROTECTI                | ION SECTION                                |                                                       |      |          |      | I.       |

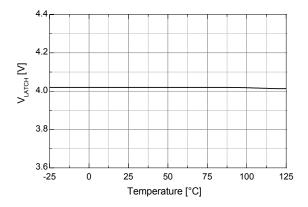

| V <sub>Latch</sub>      | Latch Voltage                              |                                                       | 3.6  | 4.0      | 4.4  | V        |

| t <sub>OLP</sub>        | Overload Protection Time (1)               |                                                       | 20   | 22       | 24   | ms       |

| t <sub>OLP_ST</sub>     | Overload Protection Time at Start-<br>up   |                                                       | 30   | 37       | 44   | ms       |

| V <sub>OLP</sub>        | Overload Protection Level                  |                                                       | 1    | 0        | 0.1  | V        |

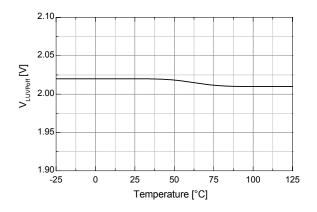

| V <sub>LUVPoff</sub>    | Line Under-Voltage Protection On to Off    | T <sub>A</sub> = 25°C                                 | 1.9  | 2.0      | 2.1  | V        |

| V <sub>LUVPon</sub>     | Line Under-Voltage Protection Off to On    | T <sub>A</sub> = 25°C                                 | 1.4  | 1.5      | 1.6  | V        |

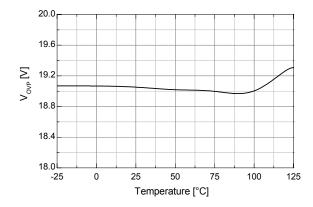

| V <sub>OVP</sub>        | Over-Voltage Protection                    | T <sub>A</sub> = 25°C                                 | 18   | 19       | 20   | V        |

#### Note:

${\bf 1.}\ These\ parameters,\ although\ guaranteed\ by\ design,\ are\ not\ tested\ in\ production.$

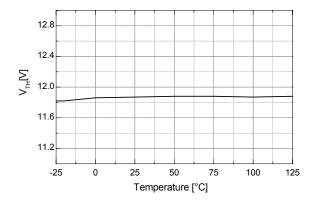

# **Typical Performance Characteristics**

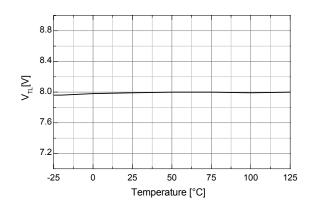

Figure 4. Start Threshold Voltage vs. Temp.

Figure 5. Stop Threshold Voltage vs. Temp.

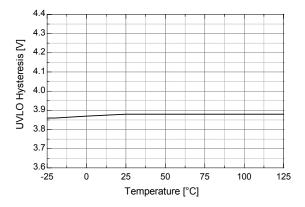

Figure 6. UVLO Hysteresis vs. Temp.

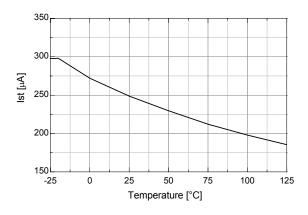

Figure 7. Start-up Supply Current vs. Temp.

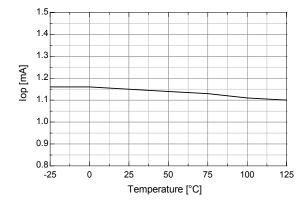

Figure 8. Operating Supply Current vs. Temp.

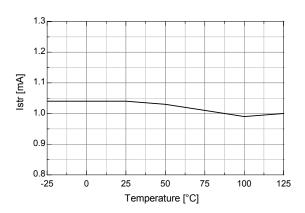

Figure 9.  $V_{STR}$  Star-up Current vs. Temp.

# **Typical Performance Characteristics** (Continued)

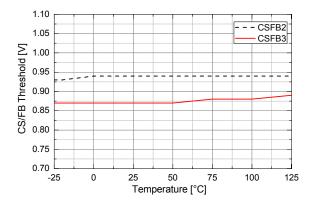

Figure 10. Burst On/Off Voltage vs. Temp.

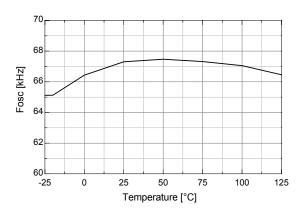

Figure 11. Operating Frequency vs. Temp.

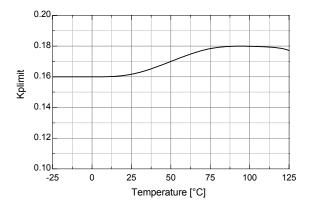

Figure 12. Offset Gain vs. Temp.

Figure 13. Maximum Duty Cycle vs. Temp.

Figure 14. OVP Voltage vs. Temp.

Figure 15. Latch Voltage vs. Temp.

# **Typical Performance Characteristics** (Continued)

1.70

1.65

2 1.60

1.55

1.50

1.40

-25 0 25 50 75 100 125

Temperature [°C]

Figure 16. LUVP On-to-Off Voltage vs. Temp.

Figure 17. LUVP Off-to-On Voltage vs. Temp.

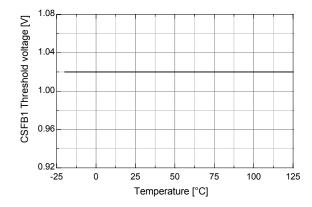

Figure 18. CS/FB Threshold Voltage vs. Temp.

# **Applications Information**

## 1. Start-up Circuit and Soft Start Block

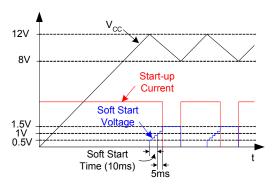

The FAN7602B contains a start-up switch to reduce the power loss of the external start-up circuit of the conventional PWM converters. The internal start-up circuit charges the V<sub>CC</sub> capacitor with 0.9mA current source if the AC line is connected. The start-up switch is turned off 15ms after IC starts up, as shown in Figure 19. The softstart function starts when the V<sub>CC</sub> voltage reaches the start threshold voltage of 12V and ends when the internal soft-start voltage reaches 1V. The internal start-up circuit starts charging the V<sub>CC</sub> capacitor again if the Vcc voltage is lowered to the minimum operating voltage, 8V. The UVLO block shuts down the output drive circuit and some blocks to reduce the IC operating current and the internal soft-start voltage drops to zero. If the V<sub>CC</sub> voltage reaches the start threshold voltage, the IC starts switching again and the soft-start block works as well.

During the soft-start, the pulse-width modulated (PWM) comparator compares the CS/FB pin voltage with the soft-start voltage. The soft-start voltage starts from 0.5V and the soft-start ends when it reaches 1V and the soft-start time is 10ms. The start-up switch is turned off when the soft-start voltage reaches 1.5V.

Figure 19. Start-up Current and V<sub>CC</sub> Voltage

#### 2. Oscillator Block

The oscillator frequency is set internally. The switching frequency is 65kHz.

## 3. Current Sense and Feedback Block

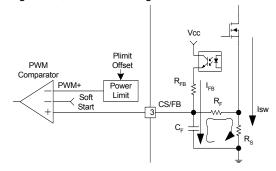

The FAN7602B performs the current sensing for the current-mode PWM and the output voltage feedback with only one pin, pin3. To achieve the two functions with one pin, an internal leading edge blanking (LEB) circuit to filter the current-sense noise is not included because the external RC filter is necessary to add the output voltage feedback information and the current-sense information. Figure 20 shows the current-sense and feedback circuits.  $R_{\rm S}$  is the current-sense resistor to sense the switch current. The current-sense information is filtered by an RC filter composed of  $R_{\rm F}$  and  $C_{\rm F}$ . According to the output voltage feedback information,  $I_{\rm FB}$  charges or stops

charging  $C_F$  to adjust the offset voltage. If  $I_{FB}$  is zero,  $C_F$  is discharged through  $R_F$  and  $R_S$  to lower offset voltage.

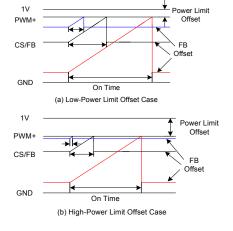

Figure 21 shows typical voltage waveforms of the CS/FB pin. The current-sense waveform is added to the offset voltage, as shown in Figure 21. The CS/FB pin voltage is compared with PWM+ that is 1V - Plimit offset. If the CS/FB voltage meets PWM+, the output drive is shut off. If the feedback offset voltage is low, the switch on time is increased. If the feedback offset voltage is high, the switch on time is decreased. In this way, the duty cycle is controlled according to the output load condition. In general, the maximum output power increases as the input voltage increases because the current slope during switch on-time increases.

To limit the output power of the converter constantly, a power-limit function is included. Sensing the converter input voltage through the Latch/Plimit pin, the Plimit offset voltage is subtracted from 1V. As shown in Figure 21, the Plimit offset voltage is subtracted from 1V and the switch on-time decreases as the Plimit offset voltage increases. If the converter input voltage increases, the switch on-time decreases, keeping the output power constant. The offset voltage is proportional to the Latch/Plimit pin voltage and the gain is 0.16; if the Latch/Plimit voltage is 1V, the offset voltage is 0.16V.

Figure 20. Current-Sense and Feedback Circuits

Figure 21. CS/FB Pin Voltage Waveforms

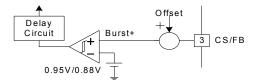

#### 4. Burst-Mode Block

The FAN7602B contains the burst-mode block to reduce the power loss at a light load and no load. A hysteresis comparator senses the offset voltage of the Burst+ for the burst mode, as shown in Figure 22. The Burst+ is the sum of the CS/FB voltage and Plimit offset voltage. The FAN7602B enters burst mode when the offset voltage of the Burst+ is higher than 0.95V and exits the burst mode when the offset voltage is lower than 0.88V. The offset voltage is sensed during the switch off time.

Figure 22. Burst-Mode Block

#### 5. Protection Block

The FAN7602B contains several protection functions to improve system reliability.

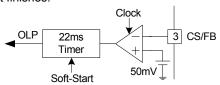

#### 5.1 Overload Protection (OLP)

The FAN7602B contains the overload protection function. If the output load is higher than the rated output current, the output voltage drops and the feedback error amplifier is saturated. The offset of the CS/FB voltage representing the feedback information is almost zero. As shown in Figure 23, the CS/FB voltage is compared with 50mV reference when the internal clock signal is high and, if the voltage is lower than 50mV, the OLP timer starts counting. If the OLP condition persists for 22ms, the timer generates the OLP signal. This protection is reset by the UVLO. The OLP block is enabled after the soft-start finishes.

Figure 23. Overload Protection Circuit

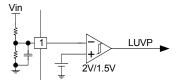

#### 5.2 Line Under-Voltage Protection

If the input voltage of the converter is lower than the minimum operating voltage, the converter input current increases too much, causing component failure. Therefore, if the input voltage is low, the converter should be protected. In the FAN7602B, the LUVP circuit senses the input voltage using the LUVP pin and, if this voltage is lower than 2V, the LUVP signal is generated. The comparator has 0.5V hysteresis. If the LUVP signal is generated, the output drive block is shut down, the output

voltage feedback loop is saturated, and the OLP initiates if the LUVP condition persists more than 22ms.

Figure 24. Line UVP Circuit

#### 5.3 Latch Protection

The latch protection is provided to protect the system against abnormal conditions using the Latch/Plimit pin. The Latch/Plimit pin can be used for the output overvoltage protection and/or other protections. If the Latch/Plimit pin voltage is made higher than 4V by an external circuit, the IC is shut down. The latch protection is reset when the  $V_{CC}$  voltage is lower than 5V.

## 5.4 Over-Voltage Protection (OVP)

If the  $V_{CC}$  voltage reaches 19V, the IC shuts down and the OVP protection is reset when the  $V_{CC}$  voltage is lower than 5V.

### 6. Output Drive Block

The FAN7602B contains a single totem-pole output stage to drive a power MOSFET. The drive output is capable of up to 450mA sourcing current and 600mA sinking current with typical rise and fall time of 45ns and 35ns, respectively, with a 1nF load.

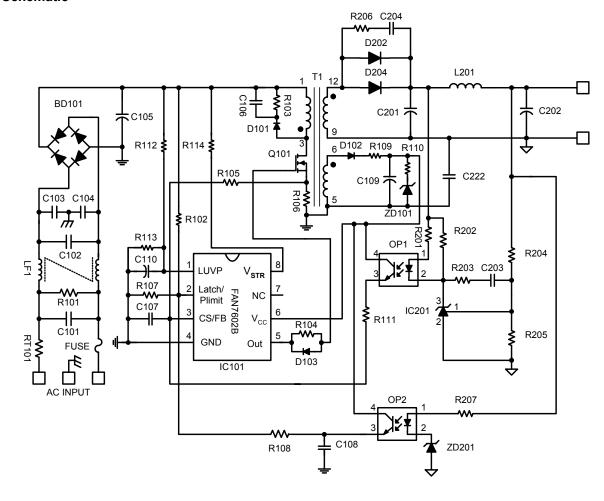

# **Typical Application Circuit**

| Application | Output Power | Input Voltage                            | Output Voltage |

|-------------|--------------|------------------------------------------|----------------|

| Adapter     | 48W          | Universal input (85~265V <sub>AC</sub> ) | 12V            |

#### **Features**

- Low stand-by power (<0.3W at 265V<sub>AC</sub>)

- Constant output power control

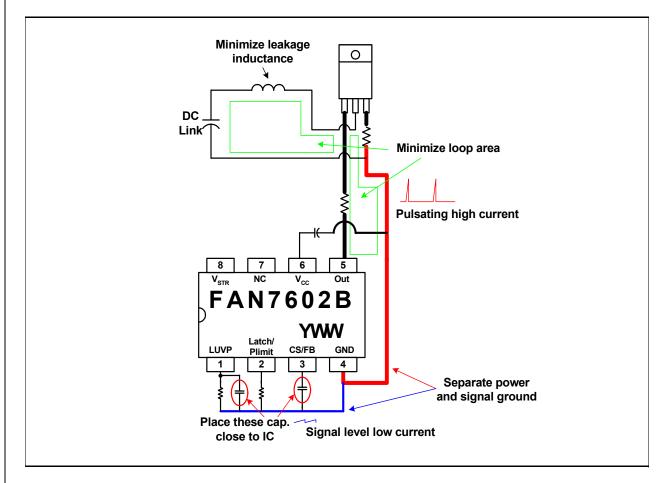

## **Key Design Notes**

- All the IC-related components should be placed close to IC, especially C107 and C110.

- If R106 value is too low, there can be subharmonic oscillation.

- R109 should be designed carefully to make V<sub>CC</sub> voltage higher than 8V when the input voltage is 265V<sub>AC</sub> at no load.

- R110 should be designed carefully to make V<sub>CC</sub> voltage lower than OVP when the input voltage is 85V<sub>AC</sub> at full load.

- R103 should be designed to keep the MOSFET V<sub>DS</sub> voltage lower than maximum rating when the output is shorted.

#### 1. Schematic

Figure 25. Schematic

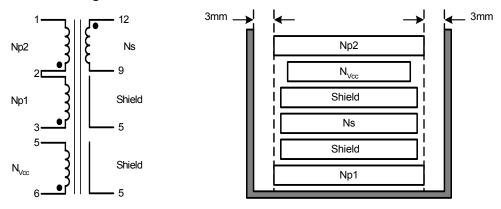

# 2. Inductor Schematic Diagram

Figure 26. Inductor Schematic Diagram

# 3. Winding Specification

| No                                              | Pin (s→f)                                             | Wire                      | Turns | Winding Method   |  |  |

|-------------------------------------------------|-------------------------------------------------------|---------------------------|-------|------------------|--|--|

| Np1                                             | 3 → 2                                                 | $0.3^{\varphi} \times 2$  | 31    | Solenoid Winding |  |  |

| Insulation: F                                   | Polyester Tape t = 0.03r                              | nm, 2 Layers              |       |                  |  |  |

| Shield                                          | 5                                                     | Copper Tape               | 0.9   | Not Shorted      |  |  |

| Insulation: F                                   | olyester Tape t = 0.03r                               | nm, 2 Layers              |       |                  |  |  |

| Ns                                              | 12 → 9                                                | $0.65^{\varphi} \times 3$ | 10    | Solenoid Winding |  |  |

| Insulation: F                                   | olyester Tape t = 0.03r                               | nm, 2 Layers              |       |                  |  |  |

| Shield                                          | 5                                                     | Copper Tape               | 0.9   | Not Shorted      |  |  |

| Insulation: P                                   | olyester Tape t = 0.03m                               | nm, 2 Layers              |       |                  |  |  |

| N <sub>Vcc</sub>                                | 6 → 5                                                 | $0.2^{\varphi}\times 1$   | 10    | Solenoid Winding |  |  |

| Insulation: Polyester Tape t = 0.03mm, 2 Layers |                                                       |                           |       |                  |  |  |

| Np2                                             | 2 → 1                                                 | $0.3^{\varphi} \times 2$  | 31    | Solenoid Winding |  |  |

| Outer Insula                                    | Outer Insulation: Polyester Tape t = 0.03mm, 2 Layers |                           |       |                  |  |  |

## 4. Electrical Characteristics

|            | Pin   | Specification | Remarks        |

|------------|-------|---------------|----------------|

| Inductance | 1 - 3 | 607μΗ         | 100kHz, 1V     |

| Inductance | 1 - 3 | 15μH          | 9 - 12 shorted |

#### 5. Core & Bobbin

■ Core: EER2828

■ Bobbin: EER2828

■ Ae(mm²): 82.1

# 6. Demo Circuit Part List

| Part          | Value          | Note                    | Part         | Value      | Note                    |  |  |

|---------------|----------------|-------------------------|--------------|------------|-------------------------|--|--|

| •             | Fuse           |                         |              | Capacitor  |                         |  |  |

| FUSE          | 1A/250V        |                         | C101         | 220nF/275V | Box Capacitor           |  |  |

| •             |                | NTC                     | C102         | 150nF/275V | Box Capacitor           |  |  |

| RT101         | 5D-9           |                         | C103, C104   | 102/1kV    | Ceramic                 |  |  |

| •             | Re             | esistor                 | C105         | 150μF/400V | Electrolytic            |  |  |

| R102,<br>R112 | 10ΜΩ           | 1/4W                    | C106         | 103/630V   | Film                    |  |  |

| R103          | 56kΩ           | 1/2W                    | C107         | 271        | Ceramic                 |  |  |

| R104          | 150Ω           | 1/4W                    | C108         | 103        | Ceramic                 |  |  |

| R105          | 1kΩ            | 1/4W                    | C109         | 22μF/25V   | Electrolytic            |  |  |

| R106          | 0.5Ω           | 1/2W                    | C110         | 473        | Ceramic                 |  |  |

| R107          | 56kΩ           | 1/4W                    | C201, C202   | 1000μF/25V | Electrolytic            |  |  |

| R108          | 10kΩ           | 1/4W                    | C203         | 102        | Ceramic                 |  |  |

| R109          | Ω0             | 1/4W                    | C204         | 102        | Ceramic                 |  |  |

| R110          | 1kΩ            | 1/4W                    | C222         | 222/1kV    | Ceramic                 |  |  |

| R111          | $6$ k $\Omega$ | 1/4W                    |              | MOSF       | ET                      |  |  |

| R113          | 180kΩ          | 1/4W                    | Q101         | FQPF8N60C  | Fairchild Semiconductor |  |  |

| R114          | 50k $Ω$        | 1/4W                    |              | Diod       | e                       |  |  |

| R201          | 1.5kΩ          | 1/4W                    | D101, D102   | UF4007     | Fairchild Semiconductor |  |  |

| R202          | 1.2kΩ          | 1/4W                    | D103         | 1N5819     | Fairchild Semiconductor |  |  |

| R203          | 20kΩ           | 1/4W                    | D202, D204   | FYPF2010DN | Fairchild Semiconductor |  |  |

| R204          | 27kΩ           | 1/4W                    | ZD101, ZD201 | 1N4744     | Fairchild Semiconductor |  |  |

| R205          | 7kΩ            | 1/4W                    | BD101        | KBP06      | FairchildSemiconductor  |  |  |

| R206          | 10Ω            | 1/2W                    |              | TNR        |                         |  |  |

| R207          | 10kΩ           | 1/4W                    | R101         | 471        | 470V                    |  |  |

|               | IC             |                         | Filter       |            |                         |  |  |

| IC101         | FAN7602B       | Fairchild Semiconductor | LF101        | 23mH       | 0.8A                    |  |  |

| IC201         | KA431          | Fairchild Semiconductor | L201         | 10μΗ       | 4.2A                    |  |  |

| OP1, OP2      | H11A817B       | Fairchild Semiconductor |              |            |                         |  |  |

# 7. PCB Layout

Figure 27. PCB Layout Recommendations for FAN7602B

## 8. Performance Data

|                          | 85V <sub>AC</sub> | 110V <sub>AC</sub> | 220V <sub>AC</sub> | 265V <sub>AC</sub> |

|--------------------------|-------------------|--------------------|--------------------|--------------------|

| Input Power at No Load   | 105.4mW           | 119.8mW            | 184.7mW            | 205.5mW            |

| Input Power at 0.5W Load | 739.4mW           | 761.4mW            | 825.4mW            | 872.2mW            |

| OLP Point                | 4.42A             | 4.66A              | 4.60A              | 4.40A              |

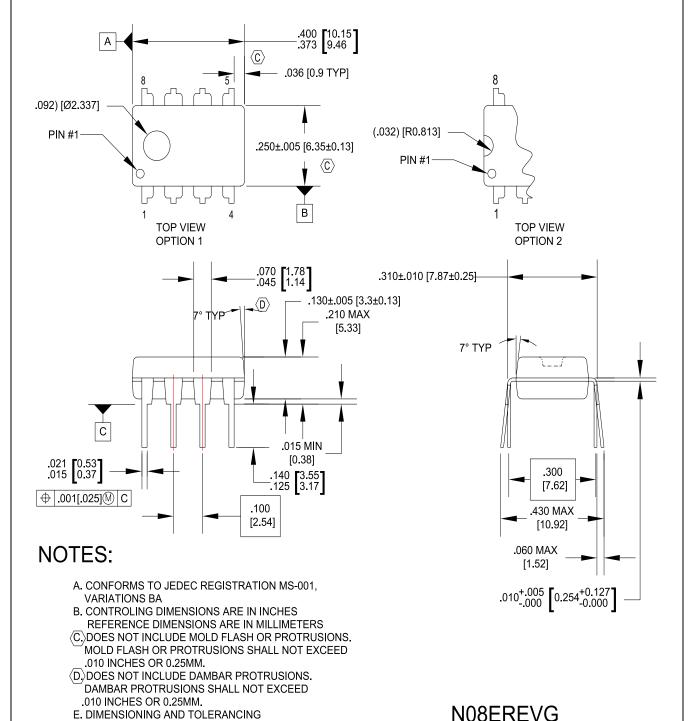

## **Mechanical Dimensions**

#### 8-DIP

Dimensions are in inches (millimeters) unless otherwise noted.

Figure 28. 8-Lead Small Dual In-line Package (DIP)

E. DIMENSIONING AND TOLERANCING

PER ASME Y14.5M-1994.

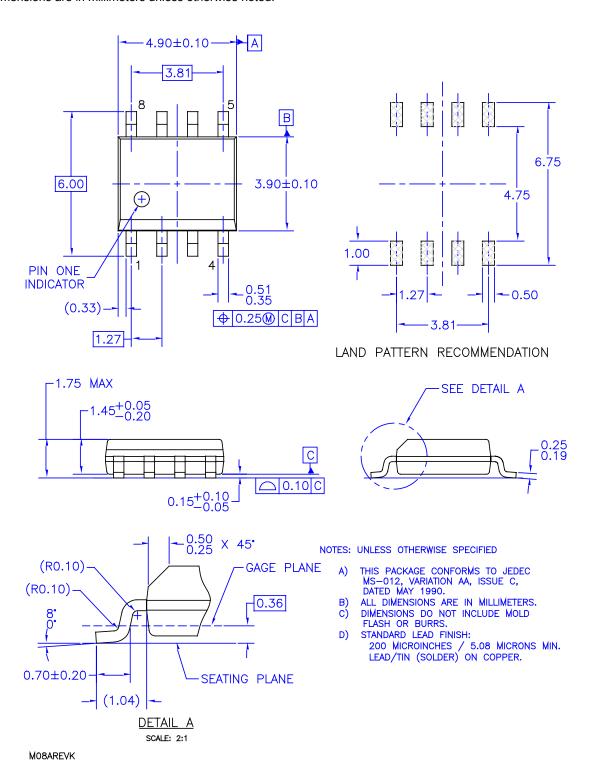

# **Mechanical Dimensions** (Continued)

## 8-SOP

Dimensions are in millimeters unless otherwise noted.

Figure 29. 8-Lead Small Outline Package (SOP)

#### **TRADEMARKS**

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

TinyLogic<sup>®</sup> HiSeC™ Programmable Active Droop™ Across the board. Around the world.™ i-Lo™ QFET<sup>0</sup> **TINYOPTO™** QS™ TinyPower™ ActiveArrav™ ImpliedDisconnect™ Bottomless™ QT Optoelectronics™ TinyWire™ IntelliMAX™ Build it Now™ ISOPLANAR™ Quiet Series™ TruTranslation™ CoolFET™ MICROCOUPLER™ RapidConfigure™ μSerDes™ UHC  $CROSSVOLT^{\text{TM}}$ RapidConnect™ MicroPak™  $\mathsf{CTL}^{\mathsf{TM}}$ UniFET™ MICROWIRE™ ScalarPump™ Current Transfer Logic™ VCX™ SMART START™ MSX™ DOME™ SPM® Wire™ MSXPro™ E<sup>2</sup>CMOS™ STEALTH™  $OCX^{\mathsf{TM}}$ EcoSPARK® SuperFET™  $OCXPro^{TM}$ EnSigna™ OPTOLOGIC® SuperSOT™-3 FACT Quiet Series™ OPTOPLANAR® SuperSOT™-6 FACT<sup>®</sup> PACMAN™ SuperSOT™-8  $\mathsf{FAST}^{\scriptscriptstyle{\circledR}}$ SyncFET™ РОР™ FASTr™ Power220® ТСМ™ **FPS™** The Power Franchise® Power247<sup>®</sup>  $\mathsf{FRFET}^{\scriptscriptstyle{(\!\varrho)}}$ PowerEdae™ GlobalOptoisolator™ PowerSaver™ TinyBoost™

PowerTrench®

#### **DISCLAIMER**

GTO™

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

TinyBuck™

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

## PRODUCT STATUS DEFINITIONS

#### **Definition of Terms**

| Datasheet Identification | Product Status         | Definition                                                                                                                                                                                               |

|--------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative or In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |

| Preliminary              | First Production       | This datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production        | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design.                                                   |

| Obsolete                 | Not In Production      | This datasheet contains specifications on a product that has been discontinued by Fairchild Semiconductor. The datasheet is printed for reference information only.                                      |

Rev. I24