# PCI-to-PCI Bridge Data Book

www.DataSheetAll.com

# PCI 6140 (HB1) PCI-to-PCI Bridge Data Book

Version 2.0

May 2003

Website: <a href="http://www.plxtech.com">http://www.plxtech.com</a>

Technical Support: <a href="http://www.plxtech.com/support">http://www.plxtech.com/support</a>

**Phone:** 408 774-9060

800 759-3735

Fax: 408 774-2169

© 2003 PLX Technology, Inc. All rights reserved.

PLX Technology, Inc. retains the right to make changes to this product at any time, without notice. Products may have minor variations to this publication, known as errata. PLX assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of PLX products.

PLX Technology and the PLX logo are registered trademarks of PLX Technology, Inc. Other brands and names are property of their respective owners.

This device is not designed, intended, authorized, or warranted to be suitable for use in medical, life-support applications, devices or systems or other critical applications.

PLX Part Number: PCI 6140-AA33PC; Former HiNT Part Number: HB1

Order Number: 6140-SIL-DB-P1-2.0

Printed in the USA, May 2003

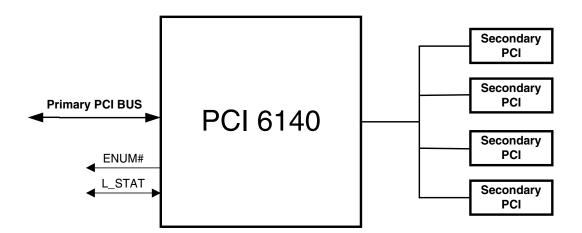

# 32-Bit, 33 MHz PCI-to-PCI Bridge

The world's first, Patent Pending PCI 6140 provides very low cost, PCI-to-PCI bridging functions. It is optimized to provide PCI masters to achieve optional **Zero Clock latency** in bursting data through the PCI 6140 PCI-to-PCI bridge. It supports up to 4 Secondary PCI master devices.

#### Optimized for the following applications:

- PCI Latency Sensitive Systems

- PCI-Retry Penalty Sensitive Systems

- PCI Slave Access Intensive bridging functions

- High Performance and Low cost PCI-to-PCI bridging functions

- Low Power and PCI ClockRun support

- Compact PCI with Hot Swap

- 3.3V, 33 MHz, PCI 2.1 and Compact PCI Hot Swap friendly features

- PC99 Power Management D3 Cold Wakeup Capable\*

- Very efficient, low power, low cost and easy to use

- PCI ClockRun support.

- Optional Zero clock latency when bursting data across PCI 6140 to preserve maximum data rate

- PCI compatible cycle completion without PCI Retry penalty of a traditional PCI bridge

- Legacy VGA and Audio IO address support

- Provides arbitration support for 4 bus masters on secondary interface

- Supports PCI Type 1 to Type 0 and Type 1 configuration command conversion

- Supports 1-Clock Latency Mode

- Synchronous Primary and Secondary Ports

- 128-pin PQFP package

<sup>\*</sup> Supported only in latest revision of PCI 6140, PCI register 82h bits 15-11 is set to 11110b, indicating PME# assertion possible during D1 state.

# History

| Rev     | Date    | Description                                     | Eng Chk | Mkt Chk |

|---------|---------|-------------------------------------------------|---------|---------|

| Rev 2.0 | 5/23/03 | This release reflects PLX part numbering.       |         |         |

|         |         | Changed S_IDEN signal to reserved               |         |         |

|         |         | Added operating ambient temperature information |         |         |

# **Contents**

| HISTORY                                                      | 6  |

|--------------------------------------------------------------|----|

| 1 PIN DIAGRAM AND PACKAGE OUTLINE                            | 11 |

| 2 PIN DESCRIPTION                                            | 13 |

|                                                              |    |

| 3 PCI 6140 CONFIGURATION REGISTERS                           | 15 |

| 3.1 Configuration Space Address Map                          | 15 |

| 3.1 Configuration Space Address Map                          | 19 |

| 3.2 Configuration Register Description                       | 16 |

| 3.2.1 Vendor ID Register (RO) (offset 00h)                   | 16 |

| 3.2.2 Device ID Register (RO) (offset 02h)                   | 16 |

| 3.2.3 Command Register (offset 04h)                          | 17 |

| 3.2.4 Primary Status Register (offset 06h)                   | 18 |

| 3.2.5 Revision ID Register (RO) (offset 08h)                 | 19 |

| 3.2.6 Class Code Register (RO) (offset 09h)                  | 19 |

| 3.2.7 Cache Line Size Register (R/W) (offset 0Ch)            | 19 |

| 3.2.8 Latency Timer (R/W) (offset 0Dh)                       | 19 |

| 3.2.9 Header Type Register (RO) (offset 0Eh)                 | 19 |

| 3.2.10 Secondary Bus Number Register (R/W) (offset 19h)      |    |

| 3.2.11 Subordinate Bus Number Register (R/W) (offset 1Ah)    |    |

| 3.2.12 Secondary Latency Timer Register (R/W) (offset 1Bh)   | 19 |

| 3.2.13 I/O Base Register (R/W) (offset 1Ch)                  | 19 |

| 3.2.14 I/O Limit Register (R/W) (offset 1Dh)                 | 20 |

| 3.2.15 Secondary Status Register (offset 1Eh)                | 20 |

| 3.2.16 Memory Base Register (R/W) (offset 20h)               | 21 |

| 3.2.17 Memory Limit Register (R/W) (offset 22h)              | 21 |

| 3.2.18 Prefetchable Memory Base Register (R/W) (offset 24h)  | 21 |

| 3.2.19 Prefetchable Memory Limit Register (R/W) (offset 26h) | 21 |

| 3.2.20 Capability Pointer(R) (offset 34h)                    | 21 |

| 3.2.21 Expansion ROM Base Address(R) (offset 38h)            | 21 |

| 3.2.22 Interrupt Line Register(R/W) (offset 3Ch)             | 21 |

| 3.2.23 Interrupt Pin(R) (offset 3Dh)                         | 21 |

| 3.2.24 Bridge Control (offset 3Eh)                           | 22 |

| 3.2.25 Subsystem Vendor ID(R/W) (offset 40h)                 | 23 |

| 3.2.26 Subsystem ID (R/W) (offset 42h)                       | 23 |

| 3.2.27 Secondary Clock Disable Register (R/W) (offset 6Ch)   | 23 |

| 3.2.28 Clock run control Register (R/W) (offset 6Fh)         | 24 |

| 3.2.29 Capability Identifier (R) (offset 80h)                |    |

| 3.2.30 Next Item Pointer (R) (offset 81h)                    |    |

| 3.2.31 Power Management Capabilities(R) (offset 82h)         | 25 |

| 3.2.32 Power Management Control/ Status(R/W) (offset 84h)    | 26 |

| 3.2.33 PMCSR Bridge Support(R) (offset 86h)                  | 26 |

| 3.4.34 Cadadiiity idefitiilei (ft) (Oliset 9011)             | 2/ |

| 3.2.35 Next Item Pointer (R) (offset 91h)                | 27       |

|----------------------------------------------------------|----------|

| 3.2.36 Hot Swap Register(R/W) (offset 92h)               | 27       |

| 3.2.37 PCI 6140 mode register (offset C0h)               | 28       |

| 4 PCI BUS OPERATION (TRANSPARENT MODE)                   | 29       |

| 4.1 Types of Transactions                                | 30       |

| 4.2 Address Phase                                        | 31       |

| 4.3 Device Select (LDEV#) Generation                     | 31       |

| 4.4 Data Phase                                           | 31       |

| 4.5 Write Transactions                                   | 31       |

| 4.6 Read Transactions                                    | 32       |

| 4.7 Configuration Transactions                           |          |

| 4.7.1 Type 0 Access to PCI 6140                          |          |

| 4.7.2 Type 1 to Type 0 Translation                       | 35       |

| 4.7.3 Type 1 to Type 1 Forwarding                        | 37       |

| 4.7.4 Special Cycles                                     | 38       |

| 4.8 Transaction Termination                              |          |

| 4.8.1 Master Termination Initiated by PCI 6140           |          |

| 4.8.2 Master Abort Received by PCI 6140                  |          |

| 4.8.3 Target Termination Received by PCI 6140            | 40       |

| 4.8.4 Target Termination Initiated by PCI 6140           | 43       |

| 5 ADDRESS DECODING                                       | 45       |

| 5.1 Address Ranges                                       | 45       |

| 5.2 I/O Address Decoding                                 | 45       |

| 5.2.1 I/O Base and Limit Address Registers               | 46<br>46 |

| 5.2.2 ISA Mode                                           | 47       |

| 5.3 Memory Address Decoding                              | 48       |

| 5.3.1 Memory-Mapped I/O Base and Limit Address Registers | 48       |

| olon mapped to bace and billit radiose registere         | -10      |

| 6 PCI BUS ARBITRATION                                    | 50       |

| 6.1 Primary PCI Bus Arbitration                          | 50       |

| 6.2 Secondary PCI Bus Arbitration                        | 50       |

| ONE CLOCK LATENCY MODE                                                                                                     |    |  |

|----------------------------------------------------------------------------------------------------------------------------|----|--|

| 8 ERROR HANDLING                                                                                                           | 52 |  |

| 8.1 Address Parity Errors                                                                                                  | 52 |  |

| 8.2 Data Parity Errors                                                                                                     | 53 |  |

| 8.2.1 Configuration Write Transactions to Configuration Space                                                              | 53 |  |

| 8.2.2 Read Transactions                                                                                                    | 53 |  |

| 8.3 Data Parity Error Reporting Summary                                                                                    | 54 |  |

| 8.4 System Error (SERR#) Reporting                                                                                         | 57 |  |

| 9 RESET                                                                                                                    | 58 |  |

| 9.1 Primary Interface Reset                                                                                                | 58 |  |

| 9.2 Secondary Interface Reset                                                                                              | 58 |  |

| 10 BRIDGE BEHAVIOR                                                                                                         | 59 |  |

| 10.1 Abnormal Termination (Initiated by Bridge Master)                                                                     | 60 |  |

| 10.1.1 Master Abort                                                                                                        | 60 |  |

| 10.1.2 PCI Master on Primary Bus                                                                                           | 60 |  |

| Configuration type #1 to type #0 conversion                                                                                | 60 |  |

| Configuration type #1 to type #1 by-passing                                                                                | 61 |  |

| Type-0 Configuration cycle filter mode                                                                                     | 61 |  |

| <u>Decoding</u>                                                                                                            | 61 |  |

| Secondary master                                                                                                           | 62 |  |

| PCI clock run feature                                                                                                      | 62 |  |

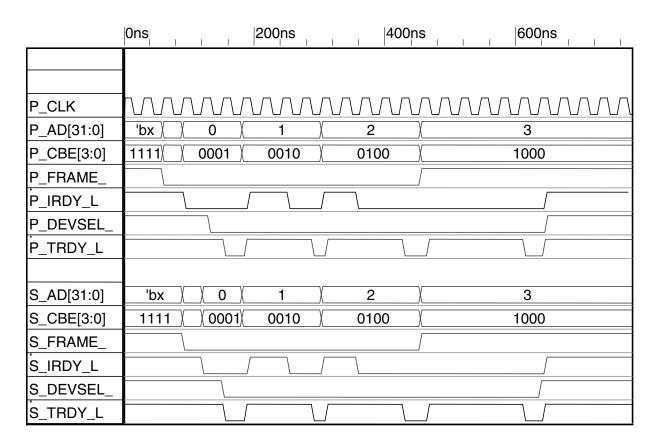

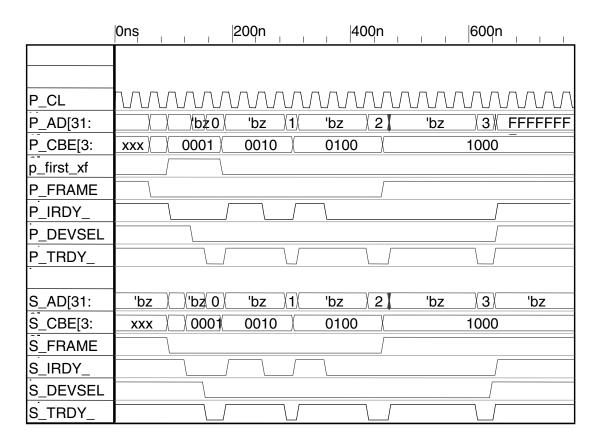

| 11 TIMING DIAGRAMS                                                                                                         | 63 |  |

| 11.1 Zero-clock Latency Mode                                                                                               |    |  |

| 11.1.1 Write Transaction in Zero-clock Latency Mode                                                                        | 63 |  |

| 11.1.2 Read Transaction in Zero-clock Latency mode                                                                         | 64 |  |

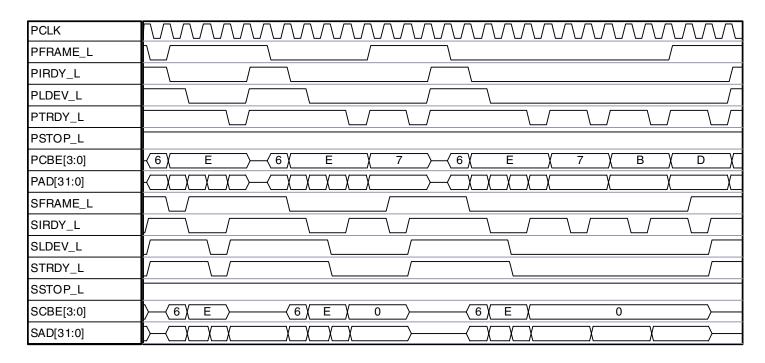

| 11.2 One-Clock Latency Mode                                                                                                |    |  |

| 11.2.1 Primary to Secondary Write Transaction                                                                              |    |  |

| 11.2.2 Primary to Secondary Read Transaction  11.2.3 Memory Read Line / Memory Read Multiple Transaction (Block Read Mode) | 67 |  |

| <u>12.</u> | <u>. ELECTRICAL SPECIFICATIONS</u>         | 68 |

|------------|--------------------------------------------|----|

|            | Maximum Ratings                            | 68 |

|            | DC Electrical Characteristics              |    |

|            | AC Specifications                          |    |

|            | 5V Signal Tolerant                         |    |

|            | Maximum Power                              |    |

| <u>13.</u> | PCI Clock Timing Parameters                | 70 |

| <u>AP</u>  | PENDIX A. INTERRUPT -DEVICE NUMBER BINDING | 71 |

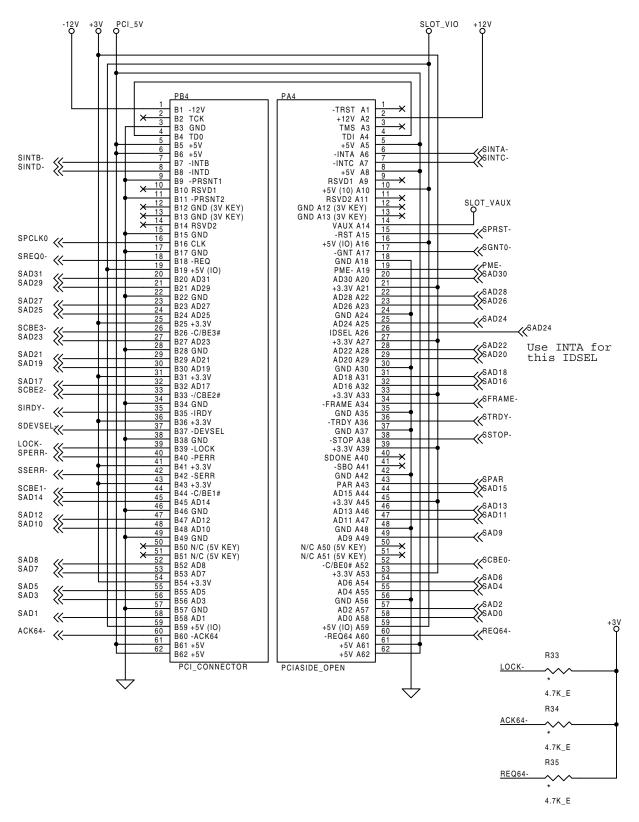

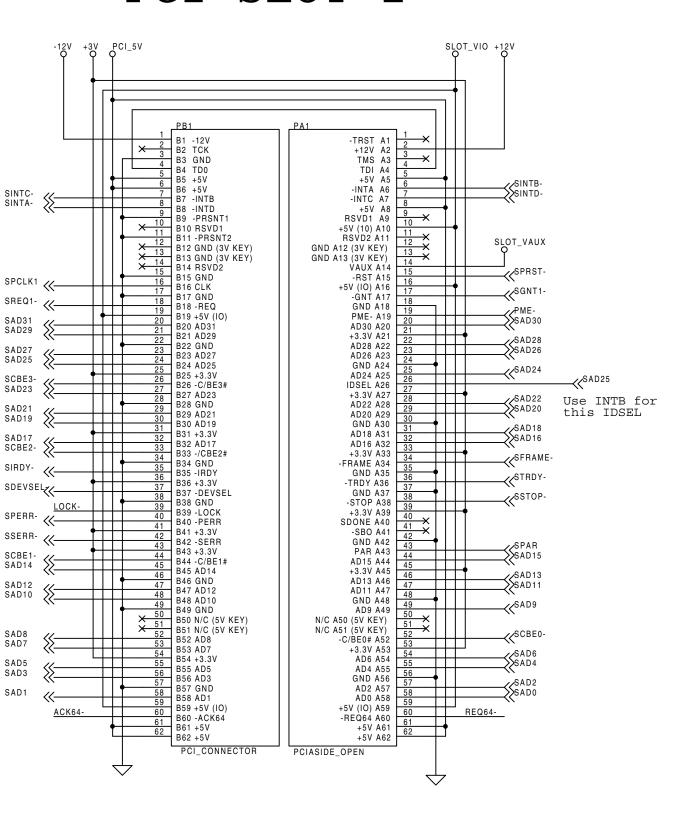

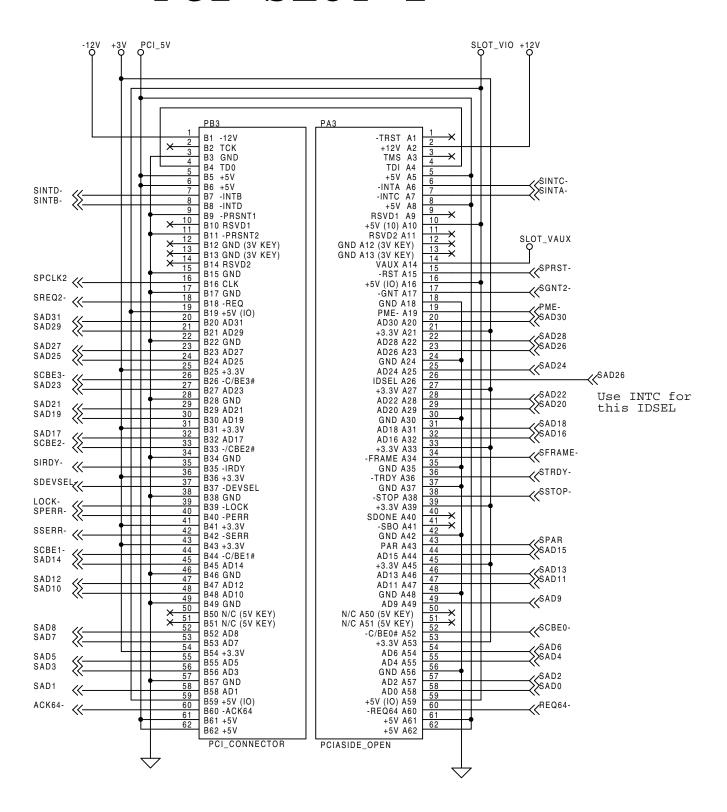

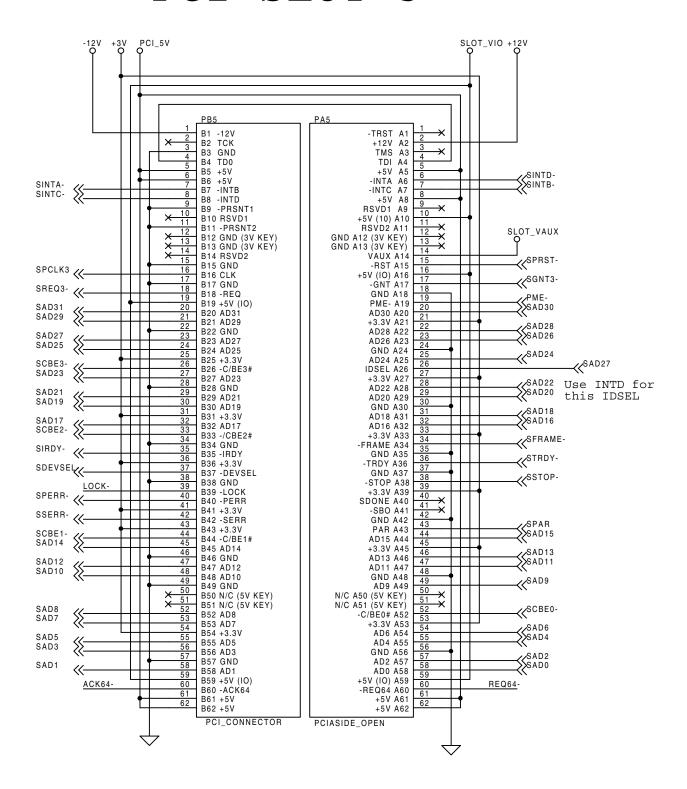

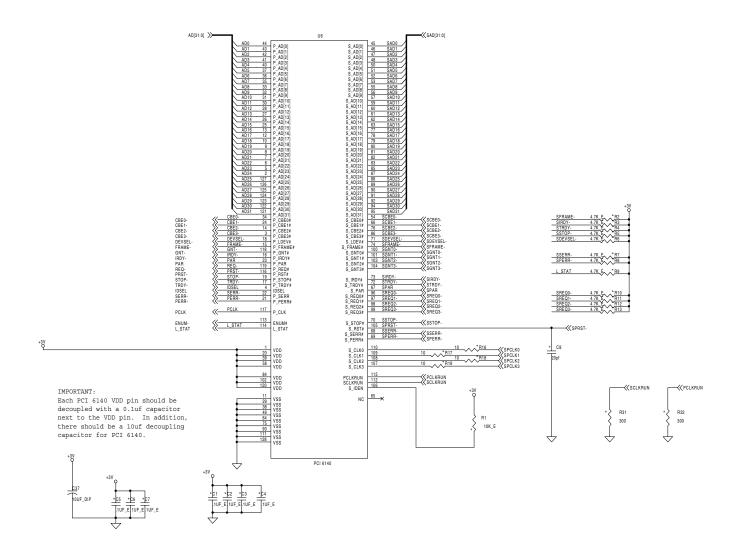

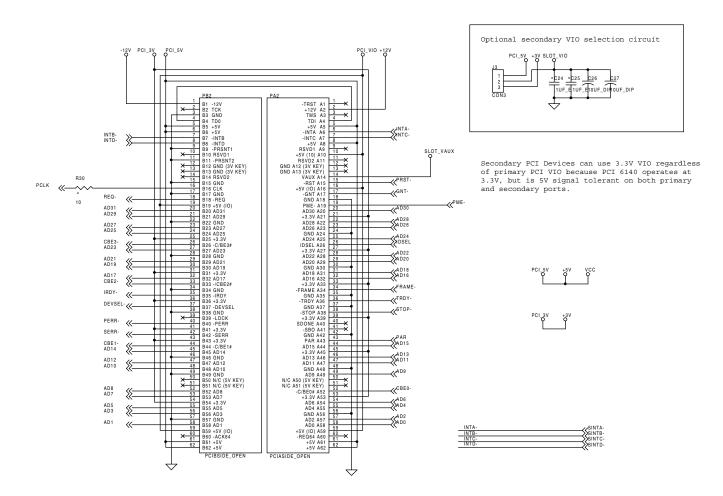

| ΑP         | PPENDIX B. SAMPLE APPLICATION SCHEMATICS   | 73 |

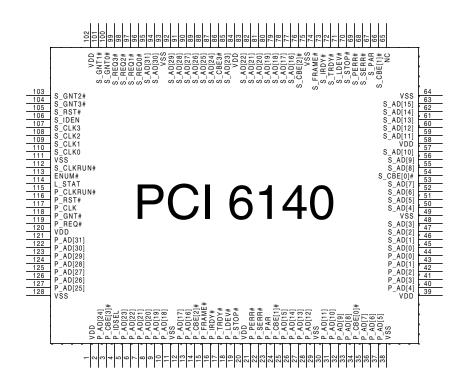

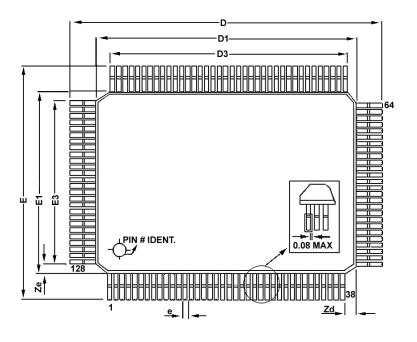

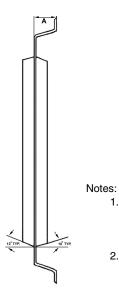

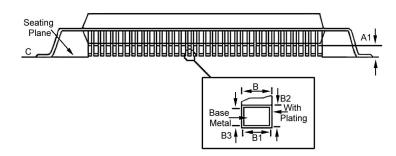

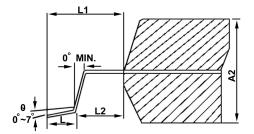

# 1 Pin Diagram and Package Outline

- Controlling dimensions are in millimeters (mm)

- 2. Dimension

D1/E1 do not include mold protrusion

| Symbol | Min        | Max   |

|--------|------------|-------|

| A      | -          | 3.4   |

| A1     | 0.25       | -     |

| A2     | 2.60       | 3.00  |

| В      | 0.17       | 0.27  |

| B1     | 0.17       | 0.23  |

| B2     | 0.13       | 0.23  |

| B3     | 0.13       | 0.17  |

| С      | 0.076      | -     |

| D      | 23.00      | 23.40 |

| D1     | 19.90      | 20.10 |

| D3     | 18.50 REF. | -     |

| E      | 17.00      | 17.40 |

| E1     | 13.90      | 14.10 |

| E3     | 12.50 REF. | -     |

| e      | 0.50 BSC   | -     |

| L      | 0.65       | 0.95  |

| L1     | 1.60 REF   | -     |

| L2     | 0.4        | -     |

| Zd     | 0.75 REF   | -     |

| Ze     | 0.75 REF   | -     |

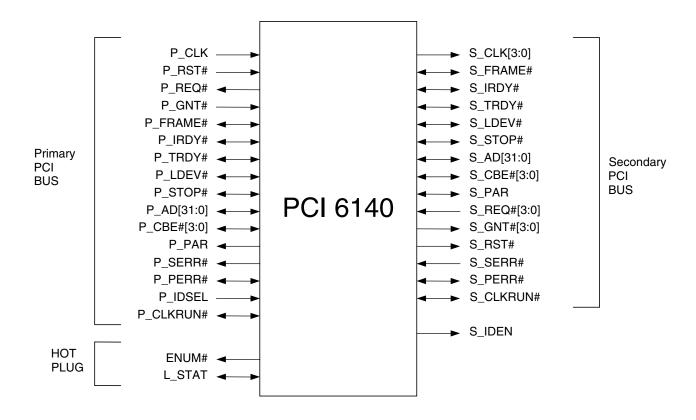

# 2 Pin Description

| SIGNAL        | PIN       | I/O      | DESCRIPTION                                         |  |

|---------------|-----------|----------|-----------------------------------------------------|--|

| P_CLK         | 117       | I        | PCI system clock                                    |  |

| P_RST#        | 116       | I        | PCI system reset                                    |  |

| P_REQ#        | 119       | 0        | PCI bus request                                     |  |

| P_GNT#        | 118       | I        | PCI bus grant                                       |  |

| P_FRAME#      | 15        | I/O      | PCI FRAME, input during slave, output during        |  |

|               |           |          | master.                                             |  |

| P_IRDY#       | 16        | 1/0      | PCI IRDY, input during slave, output during master. |  |

| P_TRDY#       | 17        | I/O      | PCI TRDY, output during slave, input during master. |  |

| P_LDEV#       | 18        | I/O      | PCI LDEV, output during slave, input during master. |  |

| P_STOP#       | 19        | I/O      | PCI STOP, output during slave, input during master. |  |

| P_IDSEL       | 4         | I        | PCI IDSEL signal                                    |  |

| P_AD[31:0]    | 121,122,  | I/O      | PCI address/data.                                   |  |

|               | 123,124,  |          | Slave mode: output only during data read phase.     |  |

|               | 125,126,  |          | Master mode: output during address phase and        |  |

|               | 127,2,5,  |          | data write phase.                                   |  |

|               | 6,7,8,9,  |          |                                                     |  |

|               | 10,12,13, |          |                                                     |  |

|               | 25,26,27, |          |                                                     |  |

|               | 28,30,31, |          |                                                     |  |

|               | 32,33,35, |          |                                                     |  |

|               | 36,37,40, |          |                                                     |  |

|               | 41,42,43, |          |                                                     |  |

| D. ODE #[0.0] | 44        | 1/0      | DOI                                                 |  |

| P_CBE#[3:0]   | 3,14,24,  | I/O      | PCI command/byte-enable, input during slave,        |  |

| D DAD         | 34        |          | output during master.                               |  |

| P_PAR         | 23        | 0        | PCI parity                                          |  |

| P_PERR#       | 21        | 1/0      | PCI parity error                                    |  |

| P_SERR#       | 22        | 0        | PCI system error                                    |  |

| P_CLKRUN#     | 115       | I/O      | Primary PCI bus clock run. Used by the central      |  |

| 0. 01 1/10.01 | 110 100   |          | resource to stop the PCI clock or to slow it down   |  |

| S_CLK[3:0]    | 110,109,  | 0        | Secondary PCI clock                                 |  |

| CIDEN         | 108,107   |          | Decembed Must be multed high                        |  |

| S_IDEN        | 106       | 0        | Reserved. Must be pulled high.                      |  |

| S_RST#        | 105<br>74 | 0<br>I/O | Secondary PCI reset                                 |  |

| S_FRAME#      |           |          | Secondary PCI FRAME                                 |  |

| S_IRDY#       | 73        | 1/0      | Secondary PCI IRDY                                  |  |

| S_TRDY#       | 72        | 1/0      | Secondary PCLL DEV                                  |  |

| S_LDEV#       | 71        | I/O      | Secondary PCI STOP                                  |  |

| S_STOP#       | 70        | I/O      | Secondary PCI STOP                                  |  |

| S_AD[31:0]  | 95,94,92,<br>91,90,89,<br>88,87,85,<br>83,82,81,<br>80,79,78,<br>77,63,62,<br>61,60,59,<br>57,56,55,<br>53,52,51,<br>50,48,47, | I/O | Secondary PCI address/data                                                                                                                   |

|-------------|--------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------|

|             | 46,45                                                                                                                          |     |                                                                                                                                              |

| S_CBE#[3:0] | 86,76,66,<br>54                                                                                                                | I/O | Secondary PCI command/byte-enable                                                                                                            |

| S_PAR       | 67                                                                                                                             | 0   | Secondary PCI parity                                                                                                                         |

| S_SERR#     | 68                                                                                                                             | I   | Secondary PCI system error                                                                                                                   |

| S_PERR#     | 69                                                                                                                             | I/O | Secondary PCI parity error                                                                                                                   |

| S_REQ[3:0]# | 99,98,97,<br>96                                                                                                                | I   | Secondary PCI bus request                                                                                                                    |

| S_GNT[3:0]# | 104,103,<br>101,100                                                                                                            | 0   | Secondary PCI bus grant                                                                                                                      |

| S_CLKRUN#   | 112                                                                                                                            | I/O | Secondary PCI bus clock run. Drive high to stop or<br>slow down secondary PCI clock, driven by<br>secondary PCI device to keep clock running |

| ENUM#       | 113                                                                                                                            | 0   | Hot Swap Interrupt                                                                                                                           |

| L_STAT      | 114                                                                                                                            | I/O | Hot Swap LED                                                                                                                                 |

| NC          | 65                                                                                                                             |     | No connect pin                                                                                                                               |

| VSS         | 11,29,38,<br>49,64,75,<br>93,111,<br>128                                                                                       | GND | Ground Pins                                                                                                                                  |

| VDD         | 1,20,39,<br>58, 84,<br>102,120                                                                                                 | PWR | Power Pins                                                                                                                                   |

# 3 PCI 6140 Configuration Registers

The following PCI registers are supported by PCI 6140. All registers, except for register C0h follow the standard PCI register definition.

# 3.1 Configuration Space Address Map

| 31-24                             | 23-16                      | 15-8                       | 7-0                        | Address |

|-----------------------------------|----------------------------|----------------------------|----------------------------|---------|

| Device ID                         |                            | Vendor ID                  |                            | 00h     |

| Status                            |                            | Command                    |                            | 04h     |

|                                   | Class Code                 | Revision ID                |                            | 08h     |

| Reserved                          | Header Type                | Latency Timer              | Cache Line<br>Size         | 0Ch     |

|                                   | Rese                       | erved                      |                            | 10h     |

|                                   | Rese                       | erved                      |                            | 14h     |

| Secondary<br>Latency<br>Timer     | Subordinate<br>Bus Number  | Secondary Bus<br>Number    | Reserved                   | 18h     |

| Second                            | lary Status                | I/O Limit                  | I/O Base                   | 1Ch     |

| Memo                              | ory Limit                  | Memory                     | Base                       | 20h     |

| Prefetchable                      | e Memory Limit             | Prefetchable Memory Base   |                            | 24h     |

| Reserved                          |                            | erved                      |                            | 28h-33h |

| Reserved                          |                            |                            | Capability<br>Pointer = 80 | 34h     |

|                                   | Expansion ROM Base Address |                            |                            | 38h     |

| Bridge Control                    |                            | Interrupt Pin =<br>00      | Interrupt<br>Line = 00     | 3ch     |

| Subsyste                          | em ID = 0000               | Subsystem Vendor ID = 0000 |                            | 40h     |

| Reserv                            |                            | erved                      |                            | 44h-6Bh |

| CLKRUN<br>control                 |                            |                            |                            | 6Ch     |

| Reserved                          |                            |                            | 70h-7Fh                    |         |

| PMC = F601                        |                            | Next Item Ptr = 90         | Capability<br>ID = 01      | 80h     |

| Data = 00 PMCSR Bridge<br>Support |                            | PMCSR =                    | = 0000                     | 84h     |

| Reserved                  |                                                        |  | 88h-8Fh |  |

|---------------------------|--------------------------------------------------------|--|---------|--|

| Reserved                  | Reserved HSCSR = 00 Next Item Ptr = Capability ID = 06 |  |         |  |

| Reserved                  |                                                        |  | 94h-BFh |  |

| Reserved PCI 6140 control |                                                        |  | C0h     |  |

| Reserved                  |                                                        |  | C4h-FFh |  |

# 3.2 Configuration Register Description

The following subsection describes the configuration registers of PCI 6140.

Table 3-1 Register Access

| Abbreviation | Definition                       |

|--------------|----------------------------------|

| RO           | Read only. Writes have no effect |

| R/W          | Read/Write                       |

| R/WC         | Read. Write 1 to clear           |

# 3.2.1 Vendor ID Register (RO) (offset 00h)

Hardwired to 3388(h).

# 3.2.2 Device ID Register (RO) (offset 02h)

Hardwired to 0021(h)

# 3.2.3 Command Register (offset 04h)

| Bit | Function                                    | Туре | Description                                                                                                                      |

|-----|---------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------|

| 0   | I/O Space<br>Enable                         | R/W  | Controls the bridge's response to I/O accesses on the primary interface.                                                         |

|     |                                             |      | 0=ignore I/O transaction                                                                                                         |

|     |                                             |      | 1=enable response to I/O transaction                                                                                             |

|     |                                             |      | Reset to 0.                                                                                                                      |

| 1   | Memory<br>Space                             | R/W  | Controls the bridge's response to memory accesses on the primary interface.                                                      |

|     | Enable                                      |      | 0=ignore all memory transaction                                                                                                  |

|     |                                             |      | 1=enable response to memory transaction                                                                                          |

|     |                                             |      | Reset to 0.                                                                                                                      |

| 2   | Bus Master<br>Enable                        | R/W  | Controls the bridge's ability to operate as a master on the primary interface.                                                   |

|     |                                             |      | 0=do not initiate transaction on the primary interface and disable response to memory or I/O transactions on secondary interface |

|     |                                             |      | 1=enable the bridge to operate as a master on the primary interface                                                              |

|     |                                             |      | Reset to 0.                                                                                                                      |

| 3   | Special<br>Cycle Enable                     | R/O  | No special cycle implementation (set to '0').                                                                                    |

| 4   | Memory<br>Write and<br>Invalidate<br>Enable | R/O  | Memory write and invalidate not supported (set to '0').                                                                          |

| 5   | Reserved                                    | R/O  | Reserved. Reset to 0                                                                                                             |

| 6   | Parity Error                                | R/W  | Controls the bridge's response to parity errors.                                                                                 |

|     | Enable                                      |      | 0=ignore any parity errors                                                                                                       |

|     |                                             |      | 1=normal parity checking performed                                                                                               |

|     |                                             |      | Reset to 0.                                                                                                                      |

| 7   | Wait Cycle<br>Control                       | R/O  | No data stepping supported (set to '0').                                                                                         |

| 8    | Primary         | 1 1 |                                               | SERR# enable |

|------|-----------------|-----|-----------------------------------------------|--------------|

|      | SERR#<br>Enable |     | 0 = Disable SERR# driver on primary interface |              |

|      | Lilabio         |     | 1 = Enable the SERR# driver                   |              |

| 9-15 | reserved        | R/O | Reserved. Reset to 0.                         |              |

# 3.2.4 Primary Status Register (offset 06h)

| Bit  | Function                         | Туре | Description                                                                                                                                                                |

|------|----------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-3  | reserved                         | R/O  | Reserved (set to '0's).                                                                                                                                                    |

| 4    | Capabilities<br>List             | R/O  | Set to '1' indicating the presence of additional PCI Capabilities such as the power management and hot swap functions                                                      |

| 5    | 33 MHz                           | R/O  | 33 MHz maximum frequency (set to '0').                                                                                                                                     |

| 6    | UDF                              | R/O  | No User-Definable Features (set to '0').                                                                                                                                   |

| 7    | Fast Back to<br>Back<br>Capable  | R/O  | Fast back-to-back write capable on primary side ( <b>set to '1'</b> ). NOTE: Fast back-to-back mode is always enabled, even though this bit actually returns '0' on reads. |

| 8    | Data Parity<br>Error<br>Detected | R/WC | Reset to 0.                                                                                                                                                                |

| 9-10 | LDEV timing                      | R/O  | LDEV timing (default to '10').                                                                                                                                             |

| 11   | Signaled<br>Target Abort         | R/WC | Should be set (by a target device) whenever a Target Abort cycle occurs. Reset to 0.                                                                                       |

| 12   | Received<br>Target Abort         | R/WC | Set to '1' (by a master device) when transactions are terminated with Target Abort. Reset to 0.                                                                            |

| 13   | Received<br>Master Abort         | R/WC | Set to '1' (by a master) when transactions are terminated with Master Abort. Reset to 0.                                                                                   |

| 14   | Signaled<br>System Error         | R/WC | Set high to indicate SERR_L assertion. Reset to 0.                                                                                                                         |

| 15   | Detected<br>Parity Error         | R/WC | Set high to indicate data parity error. Reset to 0.                                                                                                                        |

#### **3.2.5 Revision ID Register (RO)** (offset 08h)

Hardwired to 10h.

#### **3.2.6 Class Code Register (RO)** (offset 09h)

Hardwired to 060400h.

#### **3.2.7 Cache Line Size Register (R/W)** (offset 0Ch)

Bit 5-1: Used to set the memory read line or memory read multiple size in dword unit. Must be a multiple of 2.

#### 3.2.8 Latency Timer (R/W) (offset 0Dh)

Bit 7-3: Used to satisfy PCI specifications.

#### **3.2.9 Header Type Register (RO)** (offset 0Eh)

Hardwired to 01h.

#### 3.2.10 Secondary Bus Number Register (R/W) (offset 19h)

Programmed with the number of the PCI bus to which the secondary bridge interface is connected. This value is set with configuration software. Reset to 0.

#### 3.2.11 Subordinate Bus Number Register (R/W) (offset 1Ah)

Programmed with the number of the PCI bus with the highest number that is subordinate to the bridge. This value is set with configuration software. Reset to 0.

#### 3.2.12 Secondary Latency Timer Register (R/W) (offset 1Bh)

Bit 7-3: Used to satisfy PCI specifications.

#### 3.2.13 I/O Base Register (R/W) (offset 1Ch)

This register defines the bottom address of the I/O address range for the bridge. The upper four bits define the bottom address range used by the chip to determine when to forward I/O transactions from one interface to the other. These 4 bits correspond to address bits <15:12> and are writeable. The upper 16 bits corresponding to address bits <31:16> are defined in the I/O base address upper 16 bits register. The address bits <11:0> are assumed to be 000h. The lower four bits (3:0) of this register set to '0001' (read-only) to indicate 32-bit I/O addressing. Reset to 0.

#### 3.2.14 I/O Limit Register (R/W) (offset 1Dh)

This register defines the top address of the I/O address range for the bridge. The upper four bits define the top address range used by the chip to determine when to forward I/O transactions from one interface to the other. These 4 bits correspond to address bits <15:12> and are writeable. The upper 16 bits corresponding to address bits <31:16> are defined in the I/O limit address upper 16 bits register. The address bits <11:0> are assumed to be FFFh. The lower four bits (3:0) of this register set to '0001' (read-only) to indicate 32-bit I/O addressing. Reset to 0.

#### 3.2.15 Secondary Status Register (offset 1Eh)

| Bit  | Function                         | Туре | Description                                                                                                                                                         |

|------|----------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-4  | reserved                         | R/O  | Reserved (set to '0's).                                                                                                                                             |

| 5    | 33 MHz                           | R/O  | 33 MHz maximum frequency (set to '0').                                                                                                                              |

| 6    | UDF                              | R/O  | No User-Definable Features (set to '0').                                                                                                                            |

| 7    | Fast Back to<br>Back<br>Capable  | R/O  | Fast back-to-back write capable on secondary port (set to '1'). NOTE: Fast back-to-back mode is always enabled, even though this bit actually returns '0' on reads. |

| 8    | Data Parity<br>Error<br>Detected | R/WC | Reset to 0.                                                                                                                                                         |

| 9-10 | LDEV timing                      | R/O  | Medium LDEV timing (set to '01')                                                                                                                                    |

| 11   | Signaled<br>Target Abort         | R/WC | Should be set (by a target device) whenever a Target Abort cycle occurs. Should be '0' after reset.                                                                 |

|      |                                  |      | Reset to 0.                                                                                                                                                         |

| 12   | Received<br>Target Abort         | R/WC | Set to '1' (by a master device) when transactions are terminated with Target Abort.                                                                                 |

|      |                                  |      | Reset to 0.                                                                                                                                                         |

| 13   | Received<br>Master Abort         | R/WC | Set to '1' (by a master) when transactions are terminated with Master Abort.                                                                                        |

|      |                                  |      | Reset to 0.                                                                                                                                                         |

| 14   | Received<br>System Error         | R/WC | Set high to indicate SERR_L assertion. Reset to 0.                                                                                                                  |

| 15   | Detected<br>Parity Error         | R/WC | Set high to indicate data parity error. Reset to 0.                                                                                                                 |

#### 3.2.16 Memory Base Register (R/W) (offset 20h)

This register defines the base address of the memory-mapped address range for forwarding the cycle through the bridge. The upper twelve bits corresponding to address bits <31:20> are writeable. The lower 20 address bits (19:0) are assumed to be 00000h. The 12 bits are reset to 0. The lower 4 bits are read only and set to 0.

#### 3.2.17 Memory Limit Register (R/W) (offset 22h)

This register defines the upper limit address of the memory-mapped address range for forwarding the cycle through the bridge. The upper twelve bits corresponding to address bits <31:20> are writeable. The 12 bits are reset to 0. The lower 4 bits are read only and is set to 0. The lower 20 address bits (19:0) are assumed to be FFFFFh. Reset to 0.

#### 3.2.18 Prefetchable Memory Base Register (R/W) (offset 24h)

This register defines the base address of the prefetchable memory-mapped address range for forwarding the cycle through the bridge. The upper twelve bits corresponding to address bits <31:20> are writeable. The 12 bits are reset to 0. The lower 4 bits are read only and is set to 0. The lower 20 address bits (19:0) are assumed to be 00000h. Reset to 0.

#### 3.2.19 Prefetchable Memory Limit Register (R/W) (offset 26h)

This register defines the upper limit address of the memory-mapped address range for forwarding the cycle through the bridge. The upper twelve bits correspond to address bits <31:20> are writeable. The 12 bits are reset to 0. The lower 4 bits are read only and is set to 0. The lower 20 address bits (19:0) are assumed to be FFFFFh. Reset to 0.

#### 3.2.20 Capability Pointer(R) (offset 34h)

This pointer points to the PCI power management registers

#### **3.2.21 Expansion ROM Base Address(R)** (offset 38h)

PCI 6140 does not implement the expansion ROM remapping feature. Register returns all 0s when read.

#### **3.2.22 Interrupt Line Register(R/W)** (offset 3Ch)

PCI 6140 does not implement an interrupt signal pin, thus register defaults to FFh

#### **3.2.23 Interrupt Pin(R)** (offset 3Dh)

PCI 6140 does not implement any interrupt pins, so this register returns 0s.

# 3.2.24 Bridge Control (offset 3Eh)

| Bit  | Function                 | Туре | Description                                                                                                       |

|------|--------------------------|------|-------------------------------------------------------------------------------------------------------------------|

| 0    | Parity Error<br>Response | R/W  | Specify bridge's response to parity errors on the secondary interface.                                            |

|      | Enable                   |      | 0 = ignore address and parity errors                                                                              |

|      |                          |      | 1 = enable parity error reporting                                                                                 |

| 1    | SERR<br>Enable           | R/W  | Specify forwarding of secondary interface SERR assertions to the primary interface.                               |

|      |                          |      | 0 = SERR disabled                                                                                                 |

|      |                          |      | 1 = SERR enabled                                                                                                  |

| 2    | ISA Enable               | R/W  | Controls forwarding of ISA IO transactions from the primary to the secondary.                                     |

|      |                          |      | 0 = forward all IO addresses in the address range defined by IO base and IO limit registers.                      |

|      |                          |      | 1 = Block forwarding of ISA IO addresses                                                                          |

| 3    | VGA Enable               | R/W  | Controls positive decoding and forwarding of VGA-compatible memory addresses.                                     |

|      |                          |      | 0 = do not forward VGA-compatible memory and IO addresses from the primary to the secondary interface.            |

|      |                          |      | 1 = forward VGA addresses                                                                                         |

| 4    | Reserved                 | R    | Reserved                                                                                                          |

| 5    | Master Abort<br>Mode     | R/W  | Specifies how the bridge responds to a master abort that occurs on either interface when the bridge is the master |

|      |                          |      | 0 = do not report master aborts                                                                                   |

|      |                          |      | 1 = report master aborts by signaling target abort if possible or SERR if enabled in bit 1 of this register       |

| 6    | Secondary                | R/W  | Controls assertion of S_RST#                                                                                      |

|      | Bus Reset                |      | 0 = do not force the assertion of S_RST#                                                                          |

|      |                          |      | 1 = force the assertion of S_RST#                                                                                 |

| 7    | Fast Back to<br>Back     | R    | The bridge always generates fast back to back transactions to secondary devices.                                  |

| 8-15 | Reserved                 | R    | Reserved                                                                                                          |

# 3.2.25 Subsystem Vendor ID(R/W) (offset 40h)

An add-in card manufacturer may write to this register via a device driver for identification purposes.

### **3.2.26 Subsystem ID (R/W)** (offset 42h)

An add-in card manufacturer may write to this register via a device driver for identification purposes.

# 3.2.27 Secondary Clock Disable Register (R/W) (offset 6Ch)

| Bit | Function | Туре | Description               |

|-----|----------|------|---------------------------|

| 0   | Disable  | R/W  | Disable secondary clock 0 |

|     | S_CLK0   |      | 0 = enable clock          |

|     |          |      | 1 = disable clock         |

| 1   | Disable  | R/W  | Disable secondary clock 1 |

|     | S_CLK0   |      | 0 = enable clock          |

|     |          |      | 1 = disable clock         |

| 2   | Disable  | R/W  | Disable secondary clock 2 |

|     | S_CLK0   |      | 0 = enable clock          |

|     |          |      | 1 = disable clock         |

| 3   | Disable  | R/W  | Disable secondary clock 3 |

|     | S_CLK0   |      | 0 = enable clock          |

|     |          |      | 1 = disable clock         |

| 4-7 | Reserved | R    | Reserved                  |

# 3.2.28 Clock run control Register (R/W) (offset 6Fh)

|     | 5.2.20 Clock full Control Register (11/W) (Cliset Of 11) |      |                                                                               |  |  |

|-----|----------------------------------------------------------|------|-------------------------------------------------------------------------------|--|--|

| Bit | Function                                                 | Type | Description                                                                   |  |  |

| 0   | Secondary                                                | R    | Secondary clock status                                                        |  |  |

|     | clock status                                             |      | 0 = secondary clock is running                                                |  |  |

|     |                                                          |      | 1 = secondary clock is stopped                                                |  |  |

| 1   | Secondary                                                | R/W  | Secondary clock run enable                                                    |  |  |

|     | CLKRUN#<br>enable                                        |      | 0 = disable secondary CLKRUN#                                                 |  |  |

|     | CHADIC                                                   |      | 1 = enable secondary CLKRUN# (default)                                        |  |  |

| 2   | Primary keep                                             | R/W  | Primary keep clock run                                                        |  |  |

|     | clock running                                            |      | 0 = Allow primary clock to stop when secondary clock is stopped               |  |  |

|     |                                                          |      | 1 = Keep primary clock running regardless of secondary clock                  |  |  |

| 3   | Primary                                                  | R/W  | Primary clock run enable                                                      |  |  |

|     | CLKRUN#<br>enable                                        |      | 0 = disable primary CLKRUN#                                                   |  |  |

|     | Griabio                                                  |      | 1 = enable primary CLKRUN# (default)                                          |  |  |

| 4   | CLKRUN#                                                  | R/W  | Secondary clock run mode                                                      |  |  |

|     | mode                                                     |      | 0 = Stop secondary clock when requested by primary clock source               |  |  |

|     |                                                          |      | 1 = Stop secondary clock when secondary bus is idle and no cycle from primary |  |  |

| 5-7 | Reserved                                                 | R    | Reserved                                                                      |  |  |

# 3.2.29 Capability Identifier (R) (offset 80h)

This register is set to 01h to indicate power management interface registers.

#### 3.2.30 Next Item Pointer (R) (offset 81h)

Set to 90h. This field provides an offset into the function's PCI Configuration Space pointing to the location of next item in the function's capability list. In PCI 6140, this points to the hot swap registers.

#### 3.2.31 Power Management Capabilities(R) (offset 82h)

| Bit   | Function                     | Type | Description                                                                                                                                                                   |

|-------|------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-2   | Version                      | R    | This register is set to 001b, indicating that this function complies with Rev 1.0 of the PCI Power Management Interface Specification                                         |

| 3     | PME Clock                    | R    | This bit is a '0', indicating that the PCI 6140 does not support PME# signaling.                                                                                              |

| 4     | Auxiliary<br>Power<br>Source | R    | This bit is set to '0' since PCI 6140 does not support PME# signaling                                                                                                         |

| 5     | DSI                          | R    | Device Specific Initialization . Returns '0' indicating that PCI 6140 does not need special initialization                                                                    |

| 6-8   | Reserved                     | R    | Reserved                                                                                                                                                                      |

| 9     | D1 Support                   | R    | Returns '1' indicating that PCI 6140 supports the D1 device power state                                                                                                       |

| 10    | D2 Support                   | R    | Returns '1' indicating that PCI 6140 supports the D2 device power state                                                                                                       |

| 11-15 | PME Support                  | R    | Set to '11110b' indicating that PME# can be asserted from D1,D2,D3hot and D3cold states. This is true for the latest revision 10. Earlier revisions have this set to 000000b. |

# 3.2.32 Power Management Control/ Status(R/W) (offset 84h)

| Bit   | Function    | Туре | Description                                                                                                                                                                                                                    |

|-------|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-1   | Power State | R/W  | This 2-bit field is used both to determine the current power state of a function and to set the function into a new power state. The definition of the field values is given below.  00b - D0  01b - D1  10b - D2  11b - D3hot |

| 2-7   | Reserved    | R    | Reserved                                                                                                                                                                                                                       |

| 8     | PME Enable  | R    | This bit is set to '0' since PCI 6140 does not support PME# signaling                                                                                                                                                          |

| 9-12  | Data Select | R    | This field returns '0000b' indicating PCI 6140 does not return any dynamic data                                                                                                                                                |

| 13-14 | Data Scale  | R    | Returns '00b' when read. PCI 6140 does not return any dynamic data.                                                                                                                                                            |

| 15    | PME Status  | R    | This bit is set to '0' since PCI 6140 does not support PME# signaling                                                                                                                                                          |

# 3.2.33 PMCSR Bridge Support(R) (offset 86h)

| Bit | Function                       | Туре | Description                                                                                                                                |

|-----|--------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 0-5 | Reserved                       | R    | Reserved                                                                                                                                   |

| 6   | B2/B3<br>Support for<br>D3hot  | R    | This bit returns a '1' when read indicating that when the PCI 6140 is programmed to D3hot state the secondary bus's clock is stopped.      |

| 7   | Bus Power<br>Control<br>Enable | R    | Returns '1' indicating that the power management state of the secondary bus follows that of the PCI 6140 with one exception , D3hot state. |

# 3.2.34 Capability Identifier (R) (offset 90h)

This register is set to 06h to indicate power management interface registers.

# 3.2.35 Next Item Pointer (R) (offset 91h)

Set to 00h. Indicates the end of the capabilities list.

# 3.2.36 Hot Swap Register(R/W) (offset 92h)

| Bit | Function            | Туре | Description                                                    |

|-----|---------------------|------|----------------------------------------------------------------|

| 0   | Reserved            | R    | Reserved                                                       |

| 1   | ENUM#               | R/W  | Enables or disables ENUM# assertion                            |

|     | Mask Status         |      | 0 = enable ENUM# signal                                        |

|     |                     |      | 1 = mask off ENUM# signal                                      |

| 2   | Reserved            | R    | Reserved                                                       |

| 3   | LED status          | R    | Indicates if LED is on or off                                  |

|     |                     |      | 0 = LED is off                                                 |

|     |                     |      | 1 = LED is on                                                  |

| 4-5 | Reserved            | R    | Reserved                                                       |

| 6   | Extraction<br>State | R    | Indicates assertion of ENUM# due to the device being extracted |

|     |                     |      | 0 = ENUM# asserted                                             |

|     |                     |      | 1 = ENUM# not asserted                                         |

| 7   | Insertion<br>State  | R    | Indicates assertion of ENUM# due to the device being inserted  |

|     |                     |      | 0 = ENUM# asserted                                             |

|     |                     |      | 1 = ENUM# not asserted                                         |

# 3.2.37 PCI 6140 mode register (offset C0h)

| Bit | Function                                | Туре | Description                                                                                                                                                                                            |

|-----|-----------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Primary to<br>Secondary                 | R/W  | Specify delay for transactions going from primary to secondary PCI interface                                                                                                                           |

|     | transaction<br>delay                    |      | 0 = delay Primary bus to Secondary bus transfer by 1 P_CLK                                                                                                                                             |

|     | dolay                                   |      | 1 = no delay                                                                                                                                                                                           |

| 1   | P_CBE[3:0]                              | R/W  | Specify decoding timing                                                                                                                                                                                |

|     | active                                  |      | 0 = use the correct P_CBE[3:0]                                                                                                                                                                         |

|     |                                         |      | 1 = force P_CBE[3:0] active only all remaining burst read cycle.                                                                                                                                       |

| 2   | Transparent                             | R/W  | 0 = transparent P_GNT                                                                                                                                                                                  |

|     | P_GNT                                   |      | 1 = use 1-clock delayed P_GNT                                                                                                                                                                          |

| 3-4 | Reserved                                | R/W  | Reserved                                                                                                                                                                                               |

| 5   | IRDY Mode                               | R/W  | 0 = assert IRDY only after IRDY has been active on the master side                                                                                                                                     |

|     |                                         |      | 1 = assert IRDY immediately during memory-read-line, or memory-read-multiple after IRDY has been active                                                                                                |

| 6   | Memory<br>Read<br>Termination           | R/W  | Always terminate memory read line or memory read multiple on the line boundary                                                                                                                         |

| 7   | Fast Read<br>Enable                     | R/W  | Allowing fast read during burst-read.                                                                                                                                                                  |

| 8   | Legacy<br>Audio IO<br>Address<br>Enable | R/W  | 0 = disable, 1 = enable  When enabled, IO address 200-207 (Game), 388-38B (FM), 220-233 (Audio), 330-331 (MIDI) will be claimed by PCI 6140 and such cycles will be passed onto the secondary PCI bus. |

# **4 PCI Bus Operation (Transparent Mode)**

This chapter presents detailed information about PCI transactions, transaction forwarding across PCI 6140, and transaction termination.

PCI 6140 provides a simple, but complete PCI-to-PCI bridge capability, allowing PCI master and slave on its either side. It passes control and data between primary and secondary bus to guarantee complete visibility from either side. PCI 6140 is designed to behave like an intelligent buffer.

PCI 6140 achieves its zero wait state bridging function by controlling the direction of control and data. It divides control and data into 3 signal groups; the FRAME#/IRDY#/CBE#, LDEV#/TRDY#/STOP#, and AD signal groups.

Direction of FRAME#/IRDY#/CBE# is determined by P\_GNT#. If P\_GNT# is asserted at the time FRAME# is active, direction of LDEV#/TRDY#/STOP# is determined by address decode, as described in the address decode section. Direction of AD[31:0] is determined by the combination of address decode and location of slave.

#### 4.1 Types of Transactions

This section provides a summary of PCI transactions performed by PCI 6140. Table 4–1 lists the command code and name of each PCI transaction. The Master and Target columns indicate support for each transaction when PCI 6140 initiates transactions as a master, on the primary bus and on the secondary bus, and when PCI 6140 responds to transactions as a target, on the primary bus and on the secondary bus.

Table 4–1 PCI Transactions

| Type of transaction |                      | Initiates as Master |           | Responds as Target |           |

|---------------------|----------------------|---------------------|-----------|--------------------|-----------|

|                     |                      | Primary             | Secondary | Primary            | Secondary |

| 0000                | Interrupt            | N                   | N         | N                  | N         |

|                     | acknowledge          |                     |           |                    |           |

| 0001                | Special cycle        | Υ                   | Υ         | N                  | N         |

| 0010                | I/O read             | Υ                   | Υ         | Υ                  | Υ         |

| 0011                | I/O write            | Υ                   | Υ         | Υ                  | Υ         |

| 0100                | Reserved             | N                   | N         | N                  | N         |

| 0101                | Reserved             | N                   | N         | N                  | N         |

| 0110                | Memory read          | Υ                   | Υ         | Υ                  | Υ         |

| 0111                | Memory write         | Υ                   | Υ         | Υ                  | Υ         |

| 1000                | Reserved             | N                   | N         | N                  | N         |

| 1001                | Reserved             | N                   | N         | N                  | N         |

| 1010                | Configuration        | N                   | Υ         | Υ                  | N         |

|                     | read                 |                     |           |                    |           |

| 1011                | Configuration        | Type 1              | Υ         | Υ                  | Type 1    |

|                     | write                |                     |           |                    |           |

| 1100                | Memory read multiple | Υ                   | Υ         | Υ                  | Υ         |

| 1101                | Dual address         | N                   | N         | N                  | N         |

| 1101                | cycle                | IN                  | IN .      | IN                 | IN        |

| 1110                | Memory read          | Υ                   | Υ         | Υ                  | Υ         |

|                     | line                 |                     |           |                    |           |

| 1111                | Memory write         | Υ                   | Υ         | Υ                  | Υ         |

|                     | and invalidate       |                     |           |                    |           |

As indicated in Table 4–1, the following PCI commands are not supported by PCI 6140:

- PCI 6140 never initiates a PCI transaction with a reserved command code and, as a target,

PCI 6140 ignores reserved command codes.

- PCI 6140 never initiates an interrupt acknowledge transaction and, as a target, PCI 6140 ignores interrupt acknowledge transactions. Interrupt acknowledge transactions are expected to reside entirely on the primary PCI bus closest to the host bridge.

- PCI 6140 does not respond to special cycle transactions. To generate special cycle transactions on other PCI buses, either upstream or downstream, a Type 1 configuration command must be used.

- PCI 6140 does not generate Type 0 configuration transactions on the primary interface, nor does it respond to Type 0 configuration transactions on the secondary PCI interface. The PCI-to-PCI Bridge Architecture Specification does not support configuration from the secondary bus.

- PCI 6140 does not respond to nor initiate DAC cycle transactions.

#### 4.2 Address Phase

A 32-bit address uses a single address phase. This address is driven on AD<31:0>, and the bus command is driven on P\_CBE[3:0]

#### 4.3 Device Select (LDEV#) Generation

PCI 6140 always performs positive address decoding when accepting transactions on either the primary or secondary buses. PCI 6140 never subtractively decodes. Medium LDEV# timing is used on both interfaces.

#### 4.4 Data Phase

The address phase or phases of a PCI transaction are followed by one or more data phases. A data phase is completed when IRDY# and either TRDY# or STOP# are asserted. A transfer of data occurs only when both IRDY# and TRDY# are asserted during the same PCI clock cycle. The last data phase of a transaction is indicated when FRAME# is de-asserted and both TRDY# and IRDY# are asserted, or when IRDY# and STOP# are asserted.

#### 4.5 Write Transactions

Acting as PCI bus extender, PCI 6140 responds differently according to the address and initiator.

Case 1: Primary master access device on primary bus

PCI 6140 will forward all PCI signals from primary to secondary so that any device there can track the PCI bus.

Case 2: Primary master access device on secondary bus

PCI 6140 will forward address, command, data, byte enable, P\_IRDY# to secondary while forwarding S\_LDEV#, S\_TRDY# and S\_STOP# to primary bus.

Case 3: Secondary master access device on secondary bus

PCI 6140 will forward all PCI signals from secondary to primary so that any device there can track the PCI bus.

Case 4: Secondary master access device on primary bus

PCI 6140 will forward address, command, data, byte enable, S\_IRDY# to primary while forwarding P\_LDEV#, P\_TRDY# and P\_STOP# to secondary.

There is no buffer inside PCI 6140 for write.

#### 4.6 Read Transactions

PCI 6140 responds according to the address and initiator of the read command.

Case 1: Primary master access device on primary bus

PCI 6140 will forward all PCI signals from primary to secondary so that any

PCI 6140 will forward all PCI signals from primary to secondary so that any device there can track the PCI bus.

Case 2: Primary master access device on secondary bus PCI 6140 will forward address, command, byte enable, P\_IRDY# to secondary while forwarding data, S\_LDEV#, S\_TRDY# and S\_STOP# to primary bus.

Case 3: Secondary master access device on secondary bus

PCI 6140 will forward all PCI signals from secondary to primary so that any device there can track the PCI bus.

Case 4: Secondary master access device on primary bus PCI 6140 will forward address, command, byte enable, S\_IRDY# to primary while forwarding data, P\_LDEV#, P\_TRDY# and P\_STOP# to secondary.

There is no buffer inside PCI 6140 for read.

#### **4.7 Configuration Transactions**

Configuration transactions are used to initialize a PCI system. Every PCI device has a configuration space that is accessed by configuration commands. All registers are accessible in configuration space only.

In addition to accepting configuration transactions for initialization of its own configuration space, PCI 6140 also forwards configuration transactions for device initialization in hierarchical PCI systems, as well as for special cycle generation.

To support hierarchical PCI bus systems, two types of configuration transactions are specified: Type 0 and Type 1.

Type 0 configuration transactions are issued when the intended target resides on the same PCI bus as the initiator. A Type 0 configuration transaction is identified by the configuration command and the Lowest 2 bits of the address set to 00b.

Type 1 configuration transactions are issued when the intended target resides on another PCI bus, or when a special cycle is to be generated on another PCI bus. A Type 1 configuration command is identified by the configuration command and the Lowest 2 address bits set to 01b.

The register number is found in both Type 0 and Type 1 formats and gives the Dword address of the configuration register to be accessed. The function number is also included in both Type 0 and Type 1 formats and indicates which function of a multifunction device is to be accessed. For single-function devices, this value is not decoded. Type 1 configuration transaction addresses also include a 5-bit field designating the device number that identifies the device on the target PCI bus that is to be accessed. In addition, the bus number in Type 1 transactions specifies the PCI bus to which the transaction is targeted.

#### **4.7.1 Type 0 Access to PCI 6140**

The configuration space is accessed by a Type 0 configuration transaction on the primary interface. The configuration space cannot be accessed from the secondary bus. PCI 6140 responds to a Type 0 configuration transaction by asserting P\_LDEV# when the following conditions are met during the address phase:

- The bus command is a configuration read or configuration write transaction.

- low 2 address bits P\_AD<1:0> must be 00b.

- Signal P\_IDSEL must be asserted.

- The function code is 0.

PCI 6140 limits all configuration accesses to a single Dword data transfer and returns a target disconnect with the first data transfer if additional data phases are requested. Because read transactions to configuration space do not have side effects, all bytes in the requested Dword are returned, regardless of the value of the byte enable bits.

Type 0 configuration write and read transactions do not use data buffers; that is, these transactions are completed immediately.

PCI 6140 ignores all Type 0 transactions initiated on the secondary interface.

#### 4.7.2 Type 1 to Type 0 Translation

Type 1 configuration transactions are used specifically for device configuration in a hierarchical PCI bus system. A PCI-to-PCI bridge is the only type of device that should respond to a Type 1 configuration command. Type 1 configuration commands are used when the configuration access is intended for a PCI device that resides on a PCI bus other than the one where the Type 1 transaction is generated.

PCI 6140 performs a Type 1 to Type 0 translation when the Type 1 transaction is generated on the primary bus and is intended for a device attached directly to the secondary bus. PCI 6140 must convert the configuration command to a Type 0 format so that the secondary bus device can respond to it. Type 1 to Type 0 translations are performed only in the downstream direction; that is, PCI 6140 generates a Type 0 transaction only on the secondary bus, and never on the primary bus.

PCI 6140 responds to a Type 1 configuration transaction and translates it into a Type 0 transaction on the secondary bus when the following conditions are met during the address phase:

- The low 2 address bits on P\_AD<1:0> are 01b.

- The bus number in address field P\_AD<23:16> is equal to the value in the secondary bus number register in configuration space.

- The bus command on P\_CBE<3:0> is a configuration read or configuration write transaction.

When PCI 6140 translates the Type 1 transaction to a Type 0 transaction on the secondary interface, it performs the following translations to the address:

- Sets the low 2 address bits on S\_AD<1:0> to 00b.

- Decodes the device number and drives the bit pattern specified in Table 4–6 on S\_AD<31:16> for the purpose of asserting the device's IDSEL signal.

- Sets S\_AD<15:11> to 0.

- Leaves unchanged the function number and register number fields.

PCI 6140 Data Book v2.0 © 2003 PLX Technology, Inc. All rights reserved.

PCI 6140 asserts a unique address line based on the device number. These address lines may be used as secondary bus IDSEL signals. The mapping of the address lines depends on the device number in the Type 1 address bits P\_AD<15:11>. Table 4–6 presents the mapping that PCI 6140 uses.

Table 4–6 Device Number to IDSEL S AD Pin Mapping

| Device | P_AD<15:11 | Secondary IDSEL S_AD<31:16>              | S_AD Bit |

|--------|------------|------------------------------------------|----------|

| Number | >          |                                          |          |

| 0h     | 00000      | 0000 0000 0000 0001                      | 16       |

| 1h     | 00001      | 0000 0000 0000 0010                      | 17       |

| 2h     | 00010      | 0000 0000 0000 0100                      | 18       |

| 3h     | 00011      | 0000 0000 0000 1000                      | 19       |

| 4h     | 00100      | 0000 0000 0001 0000                      | 20       |

| 5h     | 00101      | 0000 0000 0010 0000                      | 21       |

| 6h     | 0110       | 0000 0000 0100 0000                      | 22       |

| 7h     | 00111      | 0000 0000 1000 0000                      | 23       |