# SED1230 Series

# **Dot Matrix LCD Controller Driver**

• 12 Character  $\times$  4 Line (5  $\times$  7 dot)

液晶之友 电话 ●Built-in Character Cenerator RÓM and RAM / Circuit for LCD

Http://www.lcdfriends.com

# DESCRIPTION

The SED1230 Series is a dot matrix LCD controller driver for character display, and can display a maximum of 48 characters, 4 user-defined characters, and a maximum of 64 symbols by means of 4-bit, 8-bit or serial data sent from a microcomputer.

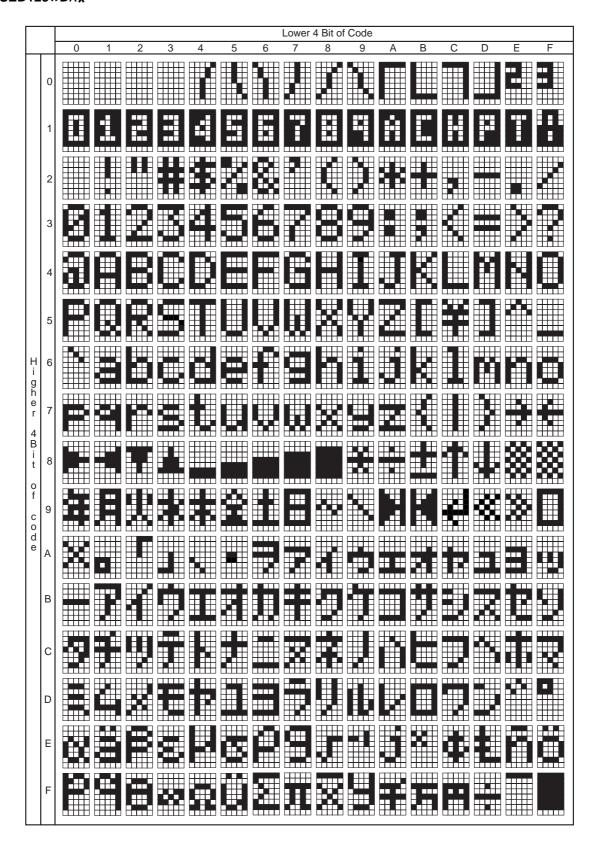

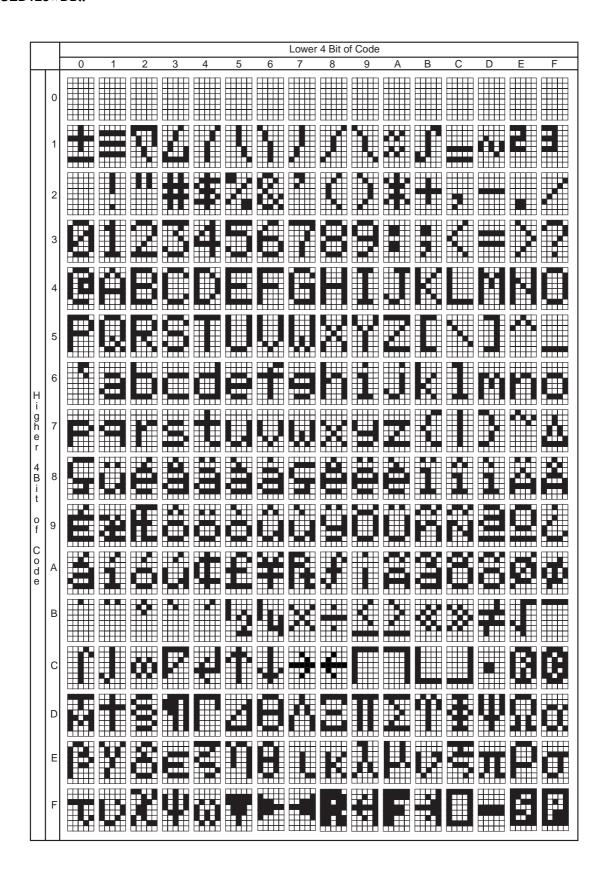

A built-in character generator ROM is prepared for 256 character types, and each character font consists of 5 imes7 dots. A user-defined character RAM for four characters of  $5 \times 7$  dots are incorporated, and a symbol register is also incorporated. With these, it is possible to apply this Series to display with a high degree of freedom. This Series can operate handy units with a minimum power consumption by means of its low power consumption and standby mode.

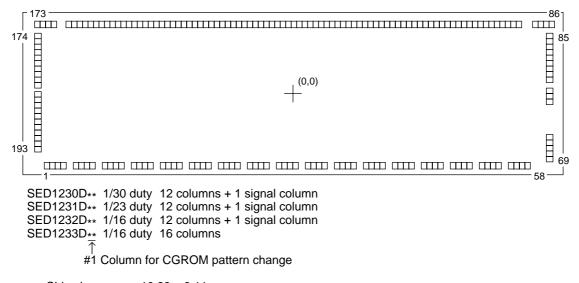

The SED1230 Series are classified into SED1230, SED1231, SED1232, and SED1233 depending on the duty of use and the number of display columns.

#### **■ FEATURES**

Built-in display RAM

48 characters + 4 user-defined characters + 64 symbols

- CGROM (for up to 256 characters), CGRAM (4 characters), and symbol register (64 symbols)

- Number of display columns × number of lines

(12 columns + 1 column for signal) × 4 lines + 52 symbols: SED1230

(12 columns + 1 column for signal) × 3 lines + 52 symbols: SED1231

(12 columns + 1 column for signal) × 2 lines + 52 symbols: SED1232

16 columns × 2 lines + 64 symbols: SED1233

- CR oscillating circuit (incorporating C and R)

- High-speed MPU interface

Interfacing with both 68 series and 80 series MPU

Interfacing in 4 bits/8 bits

- Serial interface

- Character font  $5 \times 7$  dots

- Duty ratio 1/16 (SED1232, SED1233)

1/23 (SED1231)

1/30 (SED1230)

- Simple command setting

- Built-in liquid crystal driving power circuit

Voltage boosting circuit, voltage regulating circuit, voltage follower × 4

- Built-in electronic volume function

- Low power consumption

100 μA Max. (In normal operation mode:

20 μA Max.

Power supply

Journal of the built-in power supply)

Journal Supply

VDD - VSS (logic section): -2.4 V to -3.6 V

VDD - V5 (liquid crystal drive section): -5.0 V to -11.0 V (In the case of external power supply)

Nide operating temperature range

Ta = -30 to 85°C

MOS process

Cackage: Die form SED123\*D\*B, SED123\*D\*E (Au bump)

SED123\*D\*A, SED123\*D\*C (Al pad)

TCP SED123\*T\*\*

his IC is not designed with a protection against radioactive rays.

Wide operating temperature range

- CMOS process

- Package:

This IC is not designed with a protection against radioactive rays.

# **■ BLOCK DIAGRAM**

**EPSON** SED1230 Series

### **■ PAD SPECIFICATION**

Chip size:  $10.23\times3.11~mm$ Pad pitch: 110 μm (Min.)

625 ± 25 μm (SED123\*D\*A, SED123\*D\*B) Chip thickness: 525  $\pm$  25  $\mu$ m (SED123 $\star$ D $\star$ C, SED123 $\star$ D $\star$ E)

1) A1 pad specification (SED123\*D\*A)

Pad size: A  $86 \mu m \times 135 \mu m$

B  $135 \,\mu\text{m} \times 86 \,\mu\text{m}$

2) Au bump specification (SED123\*D\*B\*)

For reference:

Bump size A  $80 \mu m \times 129 \mu m$ B  $129 \mu m \times 80 \mu m$ Bump height  $22.5 \mu m \pm 5.5 \mu m$

#### ■ ABSOLUTE MAXIMUM RATINGS

| Rating                   |           | Symbol           | Value                  | Unit |

|--------------------------|-----------|------------------|------------------------|------|

| Power supply voltage     | : (1)     | Vss              | -6.0 to +0.3           | V    |

| Power supply voltage     | (2)       | V5               | -16.0 to +0.3          | V    |

| Power supply voltage (3) |           | V1, V2, V3, V4   | V <sub>5</sub> to +0.3 | V    |

| Input voltage            |           | VIN              | Vss-0.3 to +0.3        | V    |

| Output voltage           |           | Vo               | Vss-0.3 to +0.3        | V    |

| Operating temperature    |           | Topr             | -30 to +85             | °C   |

| Storage temperature      | TCP       | T <sub>str</sub> | -55 to +100            | °C   |

| Otorago temperature      | Bare chip | ·Sti             | -75 to +125            |      |

Notes: 1. All the voltage values are based on VDD = 0 V.

- 2. For voltages of V<sub>1</sub>, V<sub>2</sub>, V<sub>3</sub> and V<sub>4</sub>, keep the condition of V<sub>DD</sub>  $\geq$  V<sub>1</sub>  $\geq$  V<sub>2</sub>  $\geq$  V<sub>3</sub>  $\geq$  V<sub>4</sub>  $\geq$  V<sub>5</sub> at all times.

- 3. If the LSI is used exceeding the absolute maximum ratings, it may lead to permanent destruction. In ordinary operation, it is desirable to use the LSI in the condition of electrical characteristics. If the LSI is used out of this condition, it may cause a malfunction of the LSI and have a bad effect on the reliability of the LSI.

#### **■ DC CHARACTERISTICS**

$(VDD = 0 \text{ V}, \text{Vss} = -3.6 \text{ V} \text{ to } -2.4 \text{ V}, \text{Ta} = -30 \text{ to } 85^{\circ}\text{C} \text{ unless otherwise specified.})$

| Characteristic                  |                      |                                     |               | Symbol                                        | Condition             |           | Min.              | Тур.            | Max.    | Unit            | Applicable pin |        |

|---------------------------------|----------------------|-------------------------------------|---------------|-----------------------------------------------|-----------------------|-----------|-------------------|-----------------|---------|-----------------|----------------|--------|

| Power Recommon Supply operation |                      | mended                              | Vss           |                                               |                       |           | -3.6              | -3.0            | -2.4    | V               | Vss            |        |

|                                 | voltage (1) Operable |                                     | , ,,,,        |                                               |                       |           | -5.5              | -3.0            | -2.0    |                 | *1             |        |

| Powe                            |                      | Recommended                         |               |                                               |                       |           |                   | -11.0           |         | -5.0            | V              | V5     |

| supply operation                |                      | ion                                 | V5            |                                               |                       |           |                   |                 |         |                 |                |        |

| volta                           | ge (2)               | Operable                            |               |                                               |                       |           |                   | -11.0           |         | -4.5            |                | *2     |

|                                 |                      | Operal                              | ole           | V1, V2                                        |                       |           |                   | 0.6 <b>X</b> V5 |         | VDD             | V              | V1, V2 |

|                                 |                      | Operable                            |               | V3, V4                                        |                       |           |                   | VDD             |         | 0.8 <b>X</b> V5 | ٧              | V3, V4 |

| High-level input voltage        |                      |                                     | VIHC          |                                               |                       |           | 0.2XVss           |                 | VDD     | ٧               | *3             |        |

| Low-level input voltage         |                      |                                     | VILC          |                                               |                       |           | Vss               |                 | 0.8×Vss | ٧               | *3             |        |

| Input leakage current           |                      |                                     | ILI           | Vin:                                          | = VDD or              | Vss       | -1.0              |                 | 1.0     | μΑ              | *3             |        |

| LC driver ON resistance         |                      |                                     | Ron           |                                               | 25°C<br>:0.1V         | V5=-7.0V  |                   | 20              | 40      | ΚΩ              | COM,SEG<br>*4  |        |

| Static current consumption      |                      |                                     | IDDQ          |                                               |                       |           |                   | 0.1             | 5.0     | μΑ              | VDD            |        |

| Dynamic current IDD             |                      |                                     | Display S     | play State V <sub>5</sub> = -7 V without load |                       |           |                   |                 | 100     | μΑ              | VDD *5         |        |

| cons                            | consumption          |                                     | Standby state |                                               | Oscillat<br>Power (   | •         |                   |                 | 20      | μΑ              | VDD *6         |        |

|                                 |                      |                                     |               | Sleep sta                                     | ep state              |           | ation OFF,<br>OFF |                 |         | 5               | μΑ             | VDD    |

|                                 |                      |                                     | Access st     | Access state fcyc=200KHz                      |                       |           |                   |                 | 500     | μΑ              | VDD *7         |        |

| Input pin capacity              |                      |                                     | CIN           | T                                             | a=25°C                | f=1MHz    |                   | 5.0             | 8.0     | pF              | *3             |        |

| Reset time                      |                      |                                     | <b>t</b> R    |                                               |                       |           | 1.0               |                 |         | μs              | *8             |        |

| Reset pulse width               |                      | <b>t</b> rw                         |               |                                               |                       | 10        |                   |                 | μs      | *9              |                |        |

| Built-in power supply           | Input                | out voltage                         |               | Vss                                           |                       |           |                   | -3.6            |         | -2.4            | V              | *10    |

|                                 | Boost                | ooster output voltage               |               | Vout                                          | Do                    | ouble boo | osting state      | -7.2            |         |                 | V              | Vout   |

|                                 |                      |                                     |               |                                               | Triple boosting state |           |                   | -10.8           |         |                 |                |        |

|                                 | •                    | oltage follower<br>perating voltage |               | V5                                            |                       |           |                   | -11.0           |         | -4.5            | V              |        |

| Mil.                            |                      | eference voltage                    |               | VREG                                          | Ta                    | = 25°C    |                   | -3.5            | -3.1    | -2.7            | V              |        |

- \*1: A wide operating voltage range is guaranteed but an abrupt voltage variation in the access status of the MPU is not guaranteed.

- \*2: The operating voltage range is applicable to the case where an external power supply is used.

- \*3: D0 D5, D6 (SCL), D7 (SI), A0, RES, CS, WR (E), P/S, IF

- \*4: This is a resistance value when a voltage of 0.1 V is applied between output pin SEGn, SEGSn, COMn or COMSn, and each power pin (V1, V2, V3 or V4). It is specified in the range of operating voltage (2).

RON = 0.1 V / ΔI

- ( $\Delta I$ : Current flowing when 0.1 V is applied between the power and output)

- \*5: Character " display. This is applicable to the case where no access is made from the MPU and the built-in power circuit and oscillating circuit are in operation.

- \*6: This is applicable to the case where the built-in power circuit is OFF and the oscillating circuit is in operation in the standby mode.

- \*7: Current consumption when data is always written by fcyc.

- The current consumption in the access state is almost proportional to the access frequency (fcyc).

When no access is made, only IDD (I) occurs.

- \*8: tk (reset time) indicates the internal circuit reset completion time from the edge of the RES signal. Accordingly, the SED123\* usually enters the operating state after tk.

- \*9: The minimum pulse width of the RES signal is specified.

- To cause a reset operation, it is necessary to input a pulse width exceeding tRW.

- \*10: When operating the boosting circuit, the power supply Vss must be used within the input voltage range.

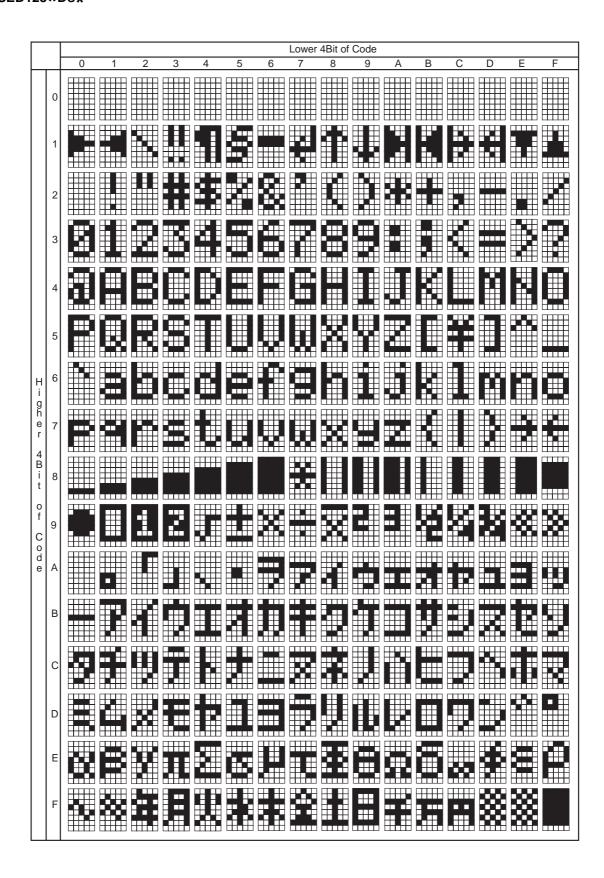

# ■ CHARACTOR FONT (JIS TYPE STANDARD)

● SED123\*DA\*

#### ● SED123\*DB\*

#### ● SED123\*DG\*

**EPSON**

SED1230 Series

#### **NOTICE**

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Control Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

All product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

©Seiko Epson Corporation 1998 All rights reserved.

#### **SEIKO EPSON CORPORATION**

**ELECTRONIC DEVICES MARKETING DIVISION**

**Electronic Device Marketing Department IC Marketing & Engineering Group**

421-8, Hino, Hino-shi, Tokyo 191-8501, JAPAN Phone: +81-(0)42-587-5816 Fax: +81-(0)42-587-5624

ED International Marketing Department I (Europe & U.S.A.)

421-8, Hino, Hino-shi, Tokyo 191-8501, JAPAN Phone: +81-(0)42-587-5812 Fax: +81-(0)42-587-5564

**ED International Marketing Department II (Asia)**

421-8, Hino, Hino-shi, Tokyo 191-8501, JAPAN Phone: +81-(0)42-587-5814 Fax: +81-(0)42-587-5110

Electric Device Information of EPSON WWW server

http://www.epson.co.jp