### 74F764-1/74F765-1

#### **FEATURES**

- Allows two microprocessors to access the same bank of dynamic RAM

- Performs arbitration, signal timing, address multiplexing and refresh

- 9 Address output pins allow direct control of up to 256K dynamic RAMs

- External address multiplexing enables control of 1Mbit (or greater) dynamic RAMs

- Separate refresh clock allows adjustable refresh timing

- 74F764-1 has an on-chip 18-bit address input latch

- 74F764-1/765-1 allow control of dynamic RAMs with row access times down to 40ns

74F764-1/765-1 output drivers designed for first reflected wave switching

#### **DESCRIPTION**

The 74F764-1/765-1 DRAM Dual-ported Controller is a high-speed synchronous dual-port arbiter and timing generator that allows two microprocessors, microcontrollers, or any other memory accessing device to share the same block of DRAM. The device performs arbitration, signal timing, address multiplexing, and refresh address generation, replacing up to 25 discrete devices.

### 74F764-1 vs. 74F765-1

The 74F764-1, though functionally and pin-to-pin compatible with the 74F765-1, differs from the later in that it has an on-chip

address input latch. This is useful in systems that have unlatched or multiplexed address and data bus.

The specialized outputs eliminate the need for signal terminations in essentially all applications.

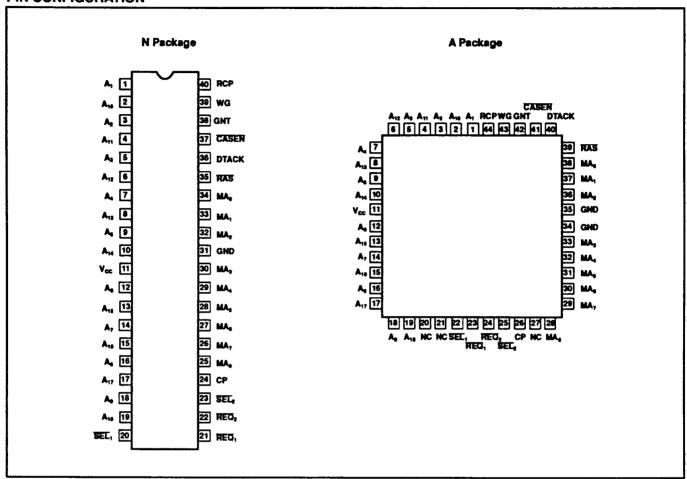

Both devices are available in 40-pin plastic DIP or 44-pin PLCC with pinouts designed to allow convenient placement of microprocessors, DRAMs, and other support chips.

#### **ORDERING INFORMATION**

| PACKAGES    | COMMERCIAL RANGE<br>V <sub>CC</sub> = 5V±10%,<br>T <sub>A</sub> = 0°C to 70°C |

|-------------|-------------------------------------------------------------------------------|

| Plastic Dip | 74F764-1N, 74F765-1N                                                          |

| PLCC-44     | 74F764-1A, 74F765-1A                                                          |

74F764-1/74F765-1

### **PIN CONFIGURATION**

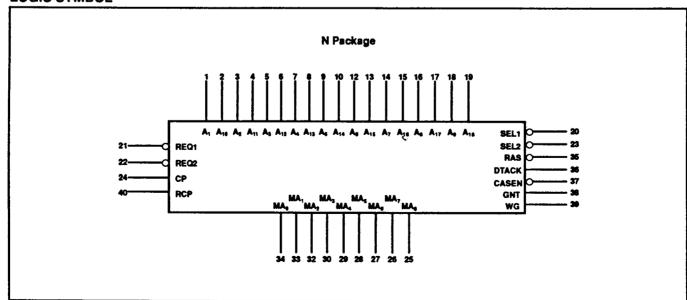

### **LOGIC SYMBOL**

### 74F764-1/74F765-1

### **PIN DESCRIPTION**

| SYMBOL PINS      |     | PINS T   |   | NAME AND FUNCTION                                                                                                                 |  |  |  |  |

|------------------|-----|----------|---|-----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                  | DIP | PLCC     |   |                                                                                                                                   |  |  |  |  |

| A <sub>1</sub>   | 1   | 1        | 1 |                                                                                                                                   |  |  |  |  |

| A <sub>2</sub>   | 3   | 3        | ı |                                                                                                                                   |  |  |  |  |

| A <sub>3</sub>   | 5   | 5        | ı |                                                                                                                                   |  |  |  |  |

| A4               | 7   | 7        | ī |                                                                                                                                   |  |  |  |  |

| A <sub>5</sub>   | 9   | 9        | i | Address inputs used to generate memory row address                                                                                |  |  |  |  |

| A <sub>6</sub>   | 12  | 12       | ī |                                                                                                                                   |  |  |  |  |

| A <sub>7</sub>   | 14  | 14       | 1 |                                                                                                                                   |  |  |  |  |

| A <sub>8</sub>   | 16  | 16       | 1 |                                                                                                                                   |  |  |  |  |

| Ag               | 18  | 18       | 1 |                                                                                                                                   |  |  |  |  |

| A <sub>10</sub>  | 2   | 2        | ı |                                                                                                                                   |  |  |  |  |

| A <sub>11</sub>  | 4   | 4        | ı |                                                                                                                                   |  |  |  |  |

| A <sub>12</sub>  | 6   | 6        | ı |                                                                                                                                   |  |  |  |  |

| A <sub>13</sub>  | 8   | 8        | 1 |                                                                                                                                   |  |  |  |  |

| A <sub>14</sub>  | 10  | 10       | ı | Address inputs used to generate memory column address                                                                             |  |  |  |  |

| A <sub>15</sub>  | 13  | 13       | ı | •                                                                                                                                 |  |  |  |  |

| A <sub>16</sub>  | 15  | 15       | ı |                                                                                                                                   |  |  |  |  |

| A <sub>17</sub>  | 17  | 17       | ī |                                                                                                                                   |  |  |  |  |

| A <sub>18</sub>  | 19  | 19       | ı |                                                                                                                                   |  |  |  |  |

| REQ <sub>1</sub> | 21  | 23       | ı | Memory access request from Microprocessor 1                                                                                       |  |  |  |  |

| REO <sub>2</sub> | 22  | 24       | I | Memory access request from Microprocessor 2                                                                                       |  |  |  |  |

| CP               | 24  | 26       | ı | Clock input which determines the master timing                                                                                    |  |  |  |  |

| RCP              | 40  | 44       | l | Refresh clock determines the period of refresh for each row after it is internally div                                            |  |  |  |  |

| SEC <sub>1</sub> | 20  | 22       | 0 | Select signal is activated in response to active REQ <sub>1</sub> input, indicating selection of Microprocessor 1                 |  |  |  |  |

| V <sub>CC</sub>  | 11  | 11       |   | Power supply +5V ±10%                                                                                                             |  |  |  |  |

| GND              | 31  | 34<br>35 |   | Ground                                                                                                                            |  |  |  |  |

| SEL <sub>2</sub> | 23  | 25       | 0 | Select signal is activated in response to active REQ <sub>2</sub> input, indicating selection of Microprocessor 2                 |  |  |  |  |

| MAo              | 34  | 38       | 0 |                                                                                                                                   |  |  |  |  |

| MA <sub>1</sub>  | 33  | 37       | 0 |                                                                                                                                   |  |  |  |  |

| MA <sub>2</sub>  | 32  | 36       | 0 |                                                                                                                                   |  |  |  |  |

| MA <sub>3</sub>  | 30  | 33       | 0 |                                                                                                                                   |  |  |  |  |

| MA <sub>4</sub>  | 29  | 32       | 0 | Memory address output pins, designed to drive address lines of the DRAM                                                           |  |  |  |  |

| MA <sub>5</sub>  | 28  | 31       | 0 |                                                                                                                                   |  |  |  |  |

| MA <sub>6</sub>  | 27  | 30       | 0 |                                                                                                                                   |  |  |  |  |

| MA <sub>7</sub>  | 26  | 29       | 0 | •                                                                                                                                 |  |  |  |  |

| MA <sub>8</sub>  | 25  | 28       | 0 |                                                                                                                                   |  |  |  |  |

| GNT              | 38  | 42       | 0 | Grant output, activated upon start of a memory access cycle                                                                       |  |  |  |  |

| RAS              | 35  | 39       | 0 | Row Address Strobe, used to latch the row address into the bank of DRAM (to be connected directly to the RAS inputs of the DRAMs) |  |  |  |  |

| WG               | 39  | 43       | 0 | Write Gate may be gated with the microprocessor's write strobe to perform an early write cycle                                    |  |  |  |  |

| CASEN            | 37  | 41       | 0 | Column Address Strobe Enable is used to latch the column address into the bank of DRAMs                                           |  |  |  |  |

| DTACK            | 36  | 40       | 0 | Data Transfer Acknowledge indicates that data on the DRAM output lines is valid o the proper access time has been met             |  |  |  |  |

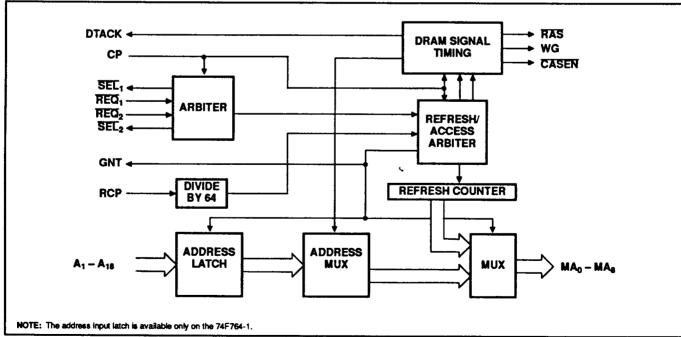

#### **ARCHITECTURE**

The 74F764-1/765-1 DRAM dual-ported controller is a synchronous device, with all signal generation being a function of the input clock (CP).

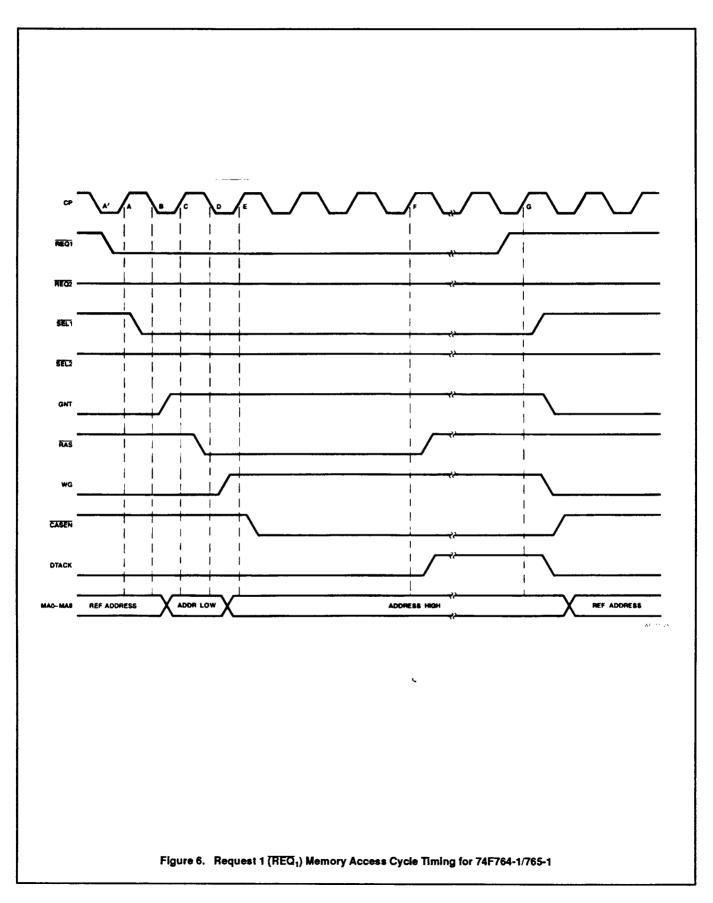

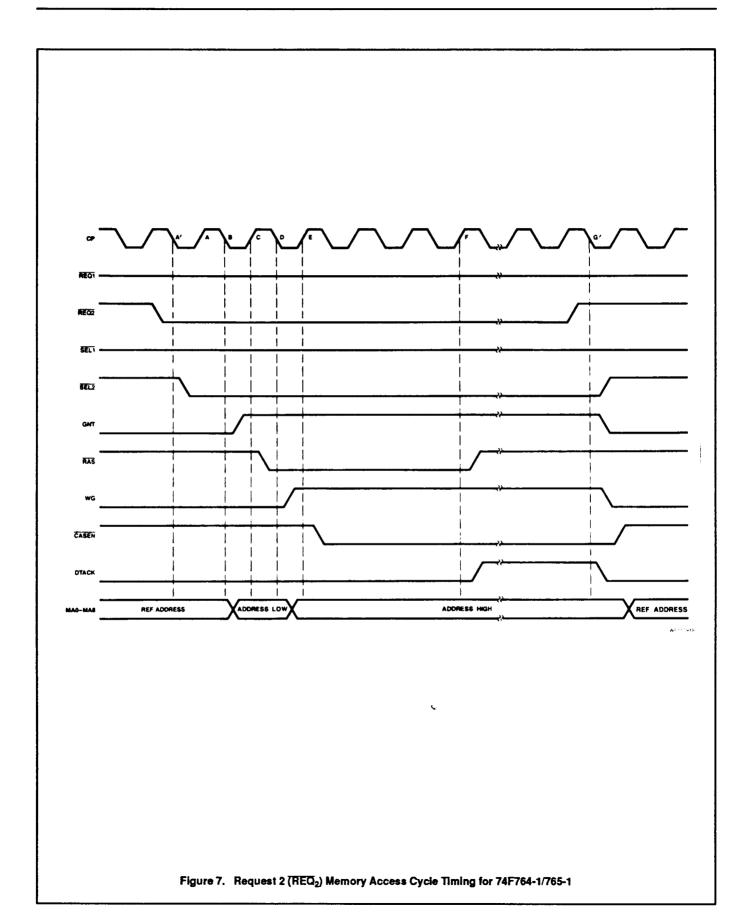

The 74F764-1/765-1 arbitration logic is divided into two stages. The first stage controls which one of the two REQ inputs will be serviced by activating the corresponding SEL output. This arbitration takes place irrespective of whether or not a refresh cycle is in progress. The arbitration is accomplished by sampling the REQ<sub>1</sub> and REQ<sub>2</sub> inputs on different edges of the CP clock. REQ<sub>1</sub> is sampled on the rising edge and REQ<sub>2</sub> on the falling edge (refer to Figures 1 and 2).

Therefore, if access to the DRAM is requested by both processors at the same time, the contention is automatically resolved. The internal flip-flops of the device used in the arbitration process have been chosen for their immunity to metastable conditions.

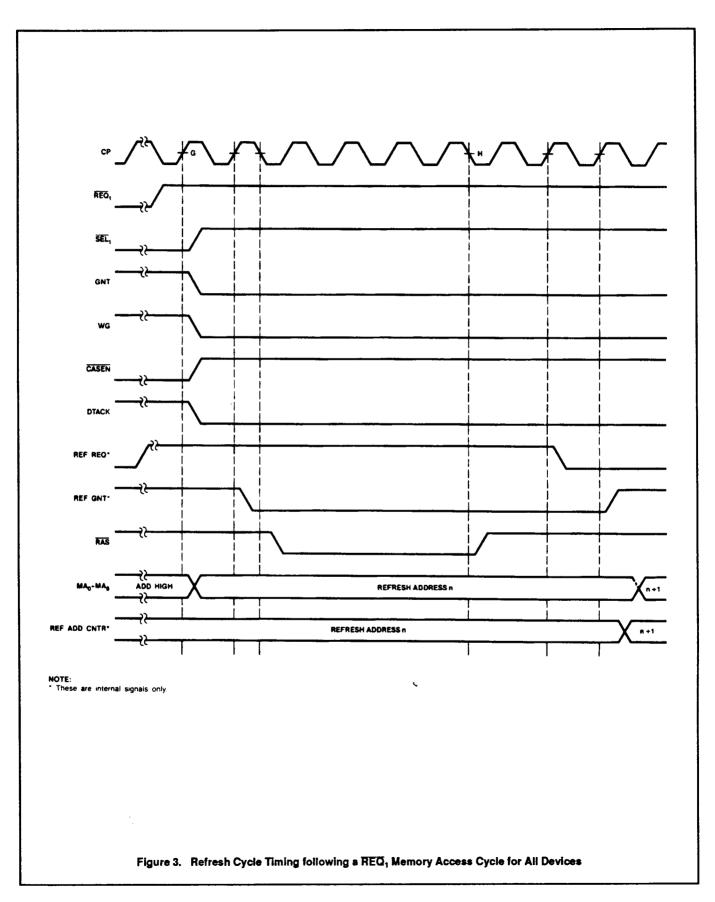

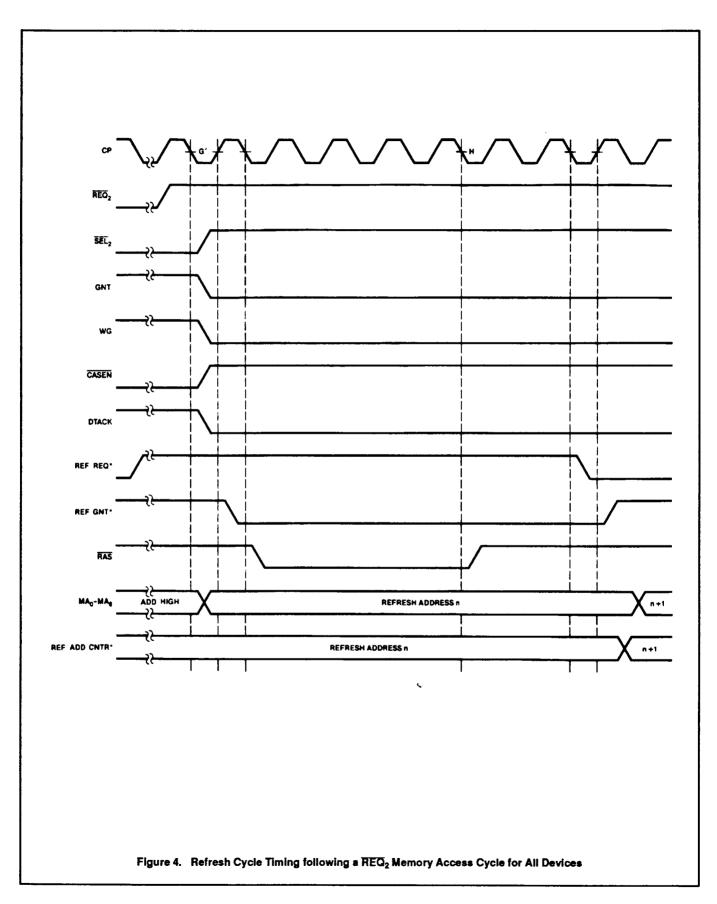

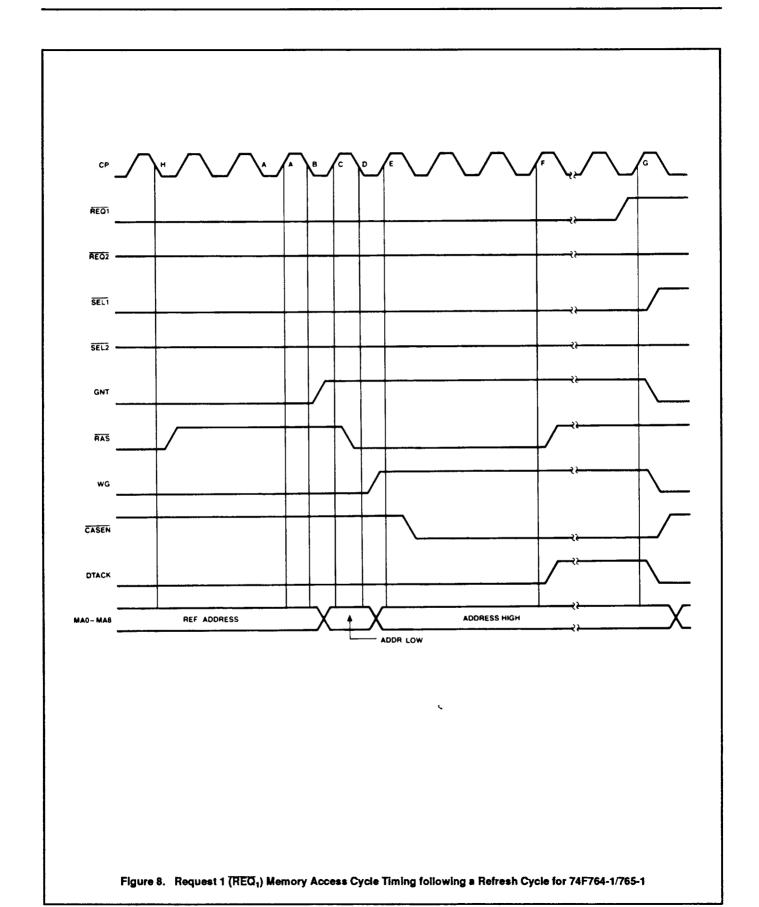

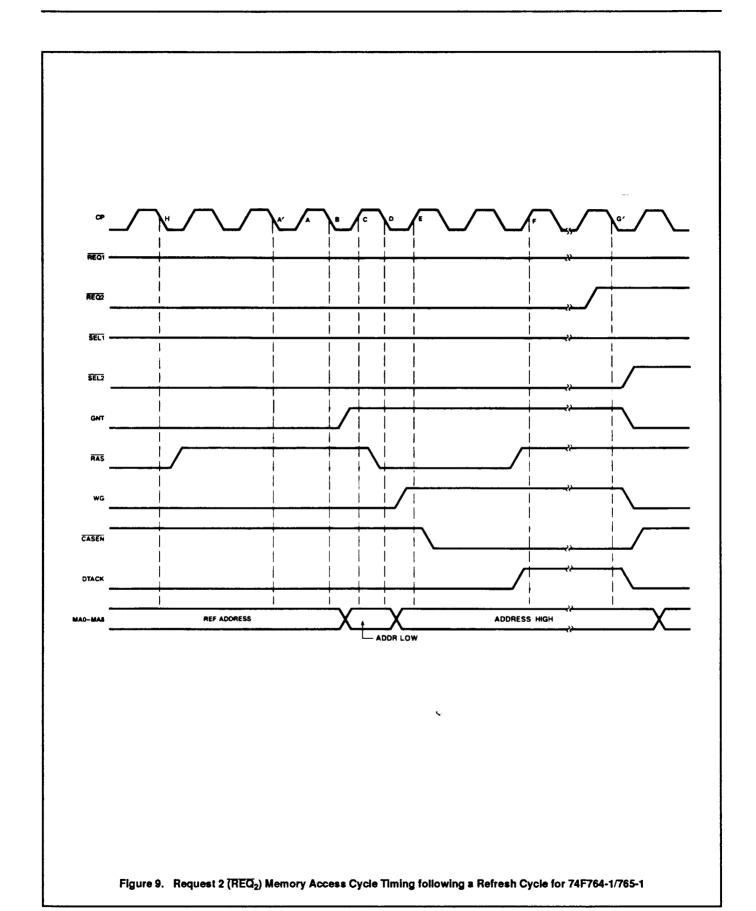

The second stage of arbitration selects between the selected processor and any internal refresh request. Refresh always has priority and is serviced immediately after the current cycle is completed (if needed). This arbitration stage also indicates the start of an access cycle by asserting the GNT output.

The Refresh Clock (RCP) input determines the period for each row. This clock may be held in the High state for external or no refresh applications. When used, a refresh request is internally generated every 64 RCP cycles. The refresh counter is incremented at the end of every refresh cycle, and provides the refresh address.

Since SEL outputs indicate which one of the two memory accessing devices has been selected to be serviced, these provide an indication of which processor's address bus should be asserted at the controller address inputs. A Data Transfer Acknowledge (DTACK) signal is generated by the timing logic and either this signal or GNT may be used with the SEL outputs to indicate the end or beginning of an access cycle for each processor.

#### **FUNCTIONAL DESCRIPTION**

As described earlier, the timing, arbitration, refresh and multiplexing functions provided by the controller are all derived from the CP input. The period of this clock for the 74F764-1/765-1 should be equal to:

(Tras(of the DRAM) + 22 - 10)/4ns plus any system guard-band required.

A microprocessor requests access to the DRAM by activating the appropriate REQ input. If a refresh cycle is not in process and the other request input is not active, the SEL output corresponding to the active REQ input will be asserted to indicate the selected processor. The GNT output then goes High to indicate the start of a memory access cycle. If however, a refresh cycle is in process, and

there is only one active REQ input, the SEL output corresponding to the active input REQ will be asserted but the GNT output will not go High until after the completion of the refresh cycle (see Figures 8 and 9).

When the device is servicing a memory access cycle and a memory access is also requested by the other processor before the current cycle is completed, the SEL output for the other processor will not be issued, though GNT is asserted at that time, because the toher processor is performing an access cycle. This will ensure that there is no contention on the address bus, i.e., the address bus is not driven by both processors at the same time.

Following the completion of the current memory access cycle, the SEL output corresponding to the awaiting REQ input will be asserted, followed by the GNT output. If however, there were any pending refresh requests, assertion of the GNT output will be held OFF until the refresh request has been serviced.

When GNT goes High, the A<sub>1</sub>-A<sub>18</sub> address inputs to the 74F764-1/765-1 are latched internally and the A<sub>1</sub>-A<sub>9</sub> signals are propagated to the MA0-MA8 outputs. The address inputs are not latched by the 74F765-1 and therefore, A<sub>1</sub>-A<sub>9</sub> inputs propagate directly to the MA<sub>0</sub>-MA<sub>8</sub> outputs.

A half-clock cycle is allowed for the address signals to propagate through to the outputs, after which the RAS output is asserted.

### BLOCK DIAGRAM

### 74F764-1/74F765-1

One half-clock cycle later, the A10-A18 latch outputs on the 74F764/764A or A10-A18 inputs to the 74F765/765A are selected and propagated to the MA0-MA8 outputs (refer to Figures 1 and 2). The Write Gate (WG) output becomes valid at this time to indicate the proper time to gate the Write signal from the selected processor to the DRAM to perform an Early Write cycle.

A half-clock cycle is again allowed for the A<sub>10</sub>-A<sub>18</sub> signals to propagate and stablize. CASEN then becomes valid. CASEN can be used as CAS output or decoded with Higher-order address signals to produce

multiple CAS signals. After CASEN is valid, the controller will wait for 2 1/2 clock cycles before negating RAS, making a total RAS pulse width of approximately 4 clock cycels. Since this width matches the standard DRAM access time, the controller next asserts DTACK output, indicating that valid data is on the DRAM data lines or that a memory access cycle is complete. DTACK may be used to assert valid data transfer acknowledge for processors requiring this signal (i.e., the 68000 family of processors).

All controller output signals are held in this final state until the selected processor

withdraws its request by driving its REQ input High. When the request is withdrawn, internal synchronization takes place, the controller output signals become inactive, and any pending memory access or refresh cycles are serviced.

A refresh cycle is serviced by propagating the 9 refresh counter address signals to the MA0-MA8 outputs. After a half-clock cycle the RAS output is asserted for four cycles and then negated for three clock cycles to meet the RAS precharge requirements of the DRAMS (see Figures 4 and 5).

- A' REO<sub>2</sub> sampled

- A REQ<sub>1</sub> sampled (REQ<sub>2</sub> disabled by SEL<sub>1</sub> circuitry) SEL<sub>1</sub> triggered (SEL<sub>1</sub> triggered by REQ<sub>1</sub> sample circuitry)

- - A1 A18 latched (Input address latch triggered by GNT circuitry)\*

- A<sub>1</sub> A<sub>9</sub> propagate to MA<sub>0</sub> MA<sub>8</sub> butputs

- C RAS triggered

- D WG triggered

- $\mbox{A}_{10}-\mbox{A}_{18}$  selected and propagated to  $\mbox{MA}_0-\mbox{MA}_8$  outputs

- E CASEN triggered

- F RAS negated DTACK triggered

- \* Only on the F764-1

Figure 1. Sequence of Events for REQ, Memory Access Cycle for 74F764-1/765-1

- A REQ<sub>2</sub> sampled

- SEL<sub>2</sub> triggered (SEL<sub>2</sub> triggered by REQ<sub>2</sub> sampling circuitry)

- A REQ<sub>1</sub> is not sampled (disabled by SEL<sub>2</sub> circuitry)

- B GNT triggered

- A<sub>1</sub> A<sub>18</sub> latched (Input address latch triggered by GNT circuitry)\*

- A<sub>1</sub> A<sub>9</sub> propagate to MA<sub>0</sub> MA<sub>8</sub> outputs

- C RAS triggered

- D WG triggered

- $A_{10}$   $A_{18}$  selected and propagated to  $MA_0$   $MA_8$  outputs

- E CASEN triggered

- F RAS negated

- DTACK triggered

- \* Only on the 'F764-1

Figure 2. Sequence of Events for REQ<sub>2</sub> Memory Access Cycle for 74F764-1/765-1

### 74F764-1/74F765-1

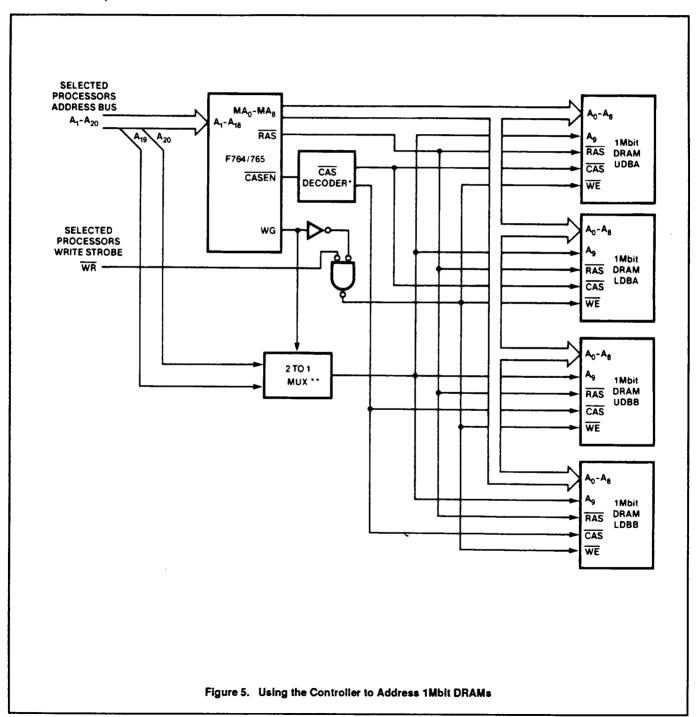

# USING THE 74F764-1/765-1 TO ADDRESS 1MBIT DRAMs

The addressing capabilities of the DRAM dual-ported controllers can be extedned to address 1Mbit (or greater) DRAMs by using an external multiplexer to multiplex additional address bits.

Figure 5 shows an application, using an external 2-to-1 multiplexer to address 1Mbit

dynamic RAMs. The 9-bit internal refresh counter of the controller provides 512 row addresses which more than meet the refreshing needs for most industry standard 1 Mbit DRAMs. Therefore, it is unnecessary to provide for any additional refresh address bits for DRAMs with up to 512 rows.

Additional address bits (for larger DRAMs) may also be multiplexed externally as long as

the DRAM refreshing requirements do not exceed 512 row addresses.

The WG output of the controller should be used to multiplex between the external row and column address bits. However, it is important that the propagation delay through the external mulitplexer does not cause column address setup violations on the dynamic RAM.

### 74F764-1/74F765-1

74F764-1/74F765-1

### **ABSOLUTE MAXIMUM RATINGS**

(Operation beyond the limits set forth in this table may impair the useful life of the device. Unless otherwise noted, these limits are over the oprating free-air temperature range.)

| SYMBOL                                             | PARAMETER                                      | 74F764-1/765-1           | UNIT |  |

|----------------------------------------------------|------------------------------------------------|--------------------------|------|--|

| Vcc                                                | Supply Voltage                                 | -0.5 to +7.0             | V    |  |

| VIN                                                | Input Voltage                                  | -0.5 to +7.0             | V    |  |

| IN                                                 | Input Current                                  | -30 to +5                | mA   |  |

| Vout                                               | Voltage applied to Output in High output state | -0.5 to +V <sub>CC</sub> | V    |  |

| IOUT Current applied to Output in Low output state |                                                | te 500                   |      |  |

| TA                                                 | Operating free-air temperature range           | 0 to +70                 | •℃   |  |

| T <sub>STG</sub>                                   | Storage temperature range                      | -65 to +150              | ∞    |  |

#### RECOMMENDED OPERATING CONDITIONS

| SYMBOL          | PARAMETER                              | 7   | 74F764-1/765-1 |     |    |  |  |  |

|-----------------|----------------------------------------|-----|----------------|-----|----|--|--|--|

|                 |                                        | MIN | NORM           | MAX |    |  |  |  |

| V <sub>CC</sub> | Supply Voltage                         | 4.5 | 5.0            | 5.5 | ٧  |  |  |  |

| V <sub>IH</sub> | High-level Input Voltage               | 2.0 |                |     | ٧  |  |  |  |

| V <sub>IL</sub> | Low-level Input Voltage                |     |                | 0.8 | V  |  |  |  |

| lik             | Input Clamp Current                    |     |                | -18 | mA |  |  |  |

| Іон             | High-level Output Current <sup>3</sup> |     |                | -20 | mA |  |  |  |

| loL             | Low-level Output Current <sup>3</sup>  |     |                | 8   | mA |  |  |  |

| T <sub>A</sub>  | Operating free-air temperature range   |     |                |     | ℃  |  |  |  |

#### NOTE:

### DC ELECTRICAL CHARACTERISTICS

| SYMBOL             | PARAMETER                                 | TEST CONDITIONS <sup>1</sup>                     |                                                  |                            | 74F764-1/765-1       |      |      | UNIT |    |

|--------------------|-------------------------------------------|--------------------------------------------------|--------------------------------------------------|----------------------------|----------------------|------|------|------|----|

|                    |                                           |                                                  |                                                  |                            |                      | TYP2 | MAX  | 1    |    |

| V <sub>OH</sub>    | High-level output voltage                 | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = MAX, | I <sub>OH</sub> = -20mA                          | ±10% V <sub>CC</sub>       | 2.4                  | 2.70 |      | ٧    |    |

|                    |                                           |                                                  | V <sub>IH</sub> = MIN                            |                            | ±5% V <sub>CC</sub>  | 2.6  | 3.0  |      | ٧  |

| V <sub>OL</sub>    | Low-level output voltage                  |                                                  | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = MAX, | I <sub>OL</sub> = 8mA      | ±10% V <sub>CC</sub> |      | 0.30 | 0.50 | ٧  |

|                    |                                           |                                                  | V <sub>IH</sub> = MIN                            |                            | ±5% V <sub>CC</sub>  |      | 0.30 | 0.50 | V  |

| V <sub>OL2</sub> 3 | Low-level output voltage                  |                                                  | 1                                                | I <sub>OL2</sub> 3 =75mA   | ±5% V <sub>∞</sub>   |      | 2.1  | 2.5  | ٧  |

| VIK                | Input clamp voltage                       | $V_{CC} = MIN, I_1 = I_{IK}$                     |                                                  |                            |                      | -0.7 | -1.2 | ٧    |    |

| i <sub>t</sub>     | Input current at maximum input voltage    | V <sub>CC</sub> = 0.0V, V <sub>I</sub> = 7.0V    |                                                  |                            |                      |      | 100  | μА   |    |

| IH                 | High-level input current                  | V <sub>CC</sub> = MAX, V <sub>I</sub> = 2.7V     |                                                  |                            |                      |      | 20   | μА   |    |

| IL.                | Low-level input current                   |                                                  | Vcc                                              | = MAX, V <sub>I</sub> = 0. | 5V                   |      | -0.2 | -0.6 | mA |

| los                | Short-circuit output current <sup>4</sup> |                                                  |                                                  | V <sub>CC</sub> = MAX      |                      | -80  | -150 | -225 | mA |

| lcc                | Supply current (total)                    | Icch                                             |                                                  | V <sub>CC</sub> = MAX      |                      |      | 120  | 165  | mA |

|                    |                                           | Iccl                                             | 1                                                |                            |                      |      | 125  | 170  | mA |

#### NOTES:

- For the conditions shown as MIN or MAX, use the appropriate value under the recommended oprating conditions for the applicable conditions.

- 2. All typical values are at  $V_{CC} = 5V$ ,  $T_A = 25$ °C.

- 3. Refer to Appendix A.

- 4. Not more than one output should be shorted at a time. For testing los, the use of hing-speed test appartus and/or sample-and-hold techniques are preferable in order to minimize internal heating and more accurately reflect operational values. Otherwise, prolonged shorting of a High output may raise the chip temperature well over the normal and thereby cause invalid readings in other parameter tests. In any sequence of parameter tests, los tests should be performed last.

<sup>3.</sup> Transient currents will exceed these values in actual operation.

### 74F764-1/74F765-1

### **AC ELECTRICAL CHARACTERISTICS**

|                  |                                                                                         |         | 74F764-1/765-1                                                                                      |     |     |                                                                                                             |     |  |  |

|------------------|-----------------------------------------------------------------------------------------|---------|-----------------------------------------------------------------------------------------------------|-----|-----|-------------------------------------------------------------------------------------------------------------|-----|--|--|

| SYMBOL           | PARAMETER                                                                               | , I     | T <sub>A</sub> = +25°C<br>V <sub>CC</sub> = +5.0V<br>C <sub>L</sub> = 300pF<br>R <sub>L</sub> = 70Ω |     |     | $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$ $V_{CC} = +5.0V \pm 10^{\circ}C$ $C_L = 300pF$ $R_L = 70\Omega$ |     |  |  |

|                  |                                                                                         | MIN     | TYP                                                                                                 | MAX | MIN | MAX                                                                                                         | 7   |  |  |

| f <sub>MAX</sub> | Maximum clock frequency                                                                 | 100     | 150                                                                                                 |     | 100 |                                                                                                             | MHz |  |  |

| <b>t</b> PLH     | Propagation delay CP(G) to SEL <sub>1</sub>                                             | 9       | 12                                                                                                  | 15  | 8   | 17                                                                                                          | ns  |  |  |

| <b>t</b> PHL     | Propagation delay CP(A) to SEL <sub>1</sub>                                             | 13      | 16                                                                                                  | 20  | 12  | 22                                                                                                          | ns  |  |  |

| <b>t</b> PLH     | Propagation delay CP(G') to SEL <sub>2</sub>                                            | 9       | 12                                                                                                  | 15  | 8   | 17                                                                                                          | ns  |  |  |

| <b>t</b> eHL     | Propagation delay CP(A') to SEL <sub>2</sub>                                            | 13      | 16                                                                                                  | 20  | 12  | 22                                                                                                          | ns  |  |  |

| ФІН              | Propagation delay CP(B) to GNT                                                          | 9       | 12                                                                                                  | 14  | 8   | 16                                                                                                          | ns  |  |  |

| <b>t</b> PHL     | Propagation delay CP(G or G') to GNT                                                    | 20      | 23                                                                                                  | 26  | 17  | 28                                                                                                          | ns  |  |  |

| фцн              | Propagation delay CP(B) to MA(row address)                                              | 11      | 14                                                                                                  | 17  | 10  | 19                                                                                                          | ns  |  |  |

| <b>t</b> PHL     |                                                                                         | 14      | 18                                                                                                  | 22  | 13  | 24                                                                                                          | 1   |  |  |

| <b>t</b> pLH     | Propagation delay CP(F or H) to RAS                                                     | 11      | 14                                                                                                  | 16  | 10  | 18                                                                                                          | ns  |  |  |

| <b>t</b> PHL     | Propagation delay CP(C) to RAS                                                          | 13      | 17                                                                                                  | 20  | 12  | 22                                                                                                          | ns  |  |  |

| ФСН              | Propagation delay CP(D) to WG                                                           | 9       | 11                                                                                                  | 14  | 8   | 16                                                                                                          | ns  |  |  |

| <b>t</b> PHL     | Propagation delay CP(G or G') to WG                                                     | 20      | 23                                                                                                  | 26  | 19  | 26                                                                                                          | ns  |  |  |

| <b>t</b> PLH     | Propagation delay CP(D) to MA(column address)                                           | 12      | 14                                                                                                  | 17  | 11  | 19                                                                                                          | ns  |  |  |

| <b>t</b> ehL     |                                                                                         | 14      | 18                                                                                                  | 21  | 13  | 23                                                                                                          |     |  |  |

| <b>t</b> PLH     | Propagation delay CP(G or G') to CASEN                                                  | 14      | 17                                                                                                  | 20  | 12  | 22                                                                                                          | ns  |  |  |

| <b>t</b> PHL     | Propagation delay CP(E) to CASEN                                                        | 14      | 16                                                                                                  | 19  | 13  | 21                                                                                                          | ns  |  |  |

| <b>t</b> PLH     | Propagation delay CP(F) to DTACK                                                        | 10      | 12                                                                                                  | 15  | 9   | 17                                                                                                          | ns  |  |  |

| <b>t</b> PHL     | Propagation delay CP(G or G') to DTACK                                                  | 20      | 23                                                                                                  | 26  | 19  | 28                                                                                                          | ns  |  |  |

|                  | 74F765                                                                                  | -1 Only |                                                                                                     |     |     | -                                                                                                           | *   |  |  |

| <b>t</b> PLH     | Propagation delay A <sub>1</sub> - A <sub>18</sub> to MA <sub>0</sub> - MA <sub>8</sub> | 9       | 11                                                                                                  | 14  | 8   | 16                                                                                                          | ns  |  |  |

| <b>t</b> PHL     |                                                                                         | 9       | 12                                                                                                  | 15  | 8   | 17                                                                                                          |     |  |  |

### **AC SETUP AND HOLD REQUIREMENTS**

|                                                        |                                                                               |           | 74F764-1/765-1                                                                                      |             |     |                                                                                      |          |  |  |

|--------------------------------------------------------|-------------------------------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------|-------------|-----|--------------------------------------------------------------------------------------|----------|--|--|

| SYMBOL                                                 | PARAMETER                                                                     | , I       | T <sub>A</sub> = +25°C<br>V <sub>CC</sub> = +5.0V<br>C <sub>L</sub> = 300pF<br>R <sub>L</sub> = 70Ω |             |     | $T_A = 0$ °C to +70°C<br>$V_{CC} = +5.0V \pm 10$ %<br>$C_L = 300$ pF<br>$R_L = 70$ Ω |          |  |  |

|                                                        |                                                                               | MIN       | TYP                                                                                                 | MAX         | MIN | MAX                                                                                  | 1        |  |  |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L)               | Setup time, High or Low REQ <sub>1</sub> , REQ <sub>2</sub> to CP             | 3         | 1                                                                                                   |             | 4   |                                                                                      | ns       |  |  |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L)               | Hold time, High or Low CP to REQ <sub>1</sub> , REQ <sub>2</sub>              | 2         | 0                                                                                                   |             | 3   |                                                                                      | ns       |  |  |

| ቴ <sub>ራ</sub> (H)<br>ቴ <sub>ራ</sub> (L)               | CP pulse width High or Low                                                    | 5 5       | 3                                                                                                   |             | 5   |                                                                                      | ns       |  |  |

| <b>t</b> <sub>w</sub> (H)<br><b>t</b> <sub>w</sub> (L) | RCP pulse width High or Low                                                   | 5         |                                                                                                     |             | 5   |                                                                                      | ns       |  |  |

|                                                        | 74F7                                                                          | 64-1 Only | ·                                                                                                   | <del></del> |     | 4                                                                                    | <u> </u> |  |  |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L)               | Setup time, High or Low A <sub>1</sub> – A <sub>18</sub> to CP (\$\ddagger\$) | 0         | -1 <sup>1</sup>                                                                                     |             | 1   |                                                                                      | ns       |  |  |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L)               | Hold time, High or Low CP (↓) to A <sub>1</sub> - A <sub>18</sub>             | 5         | 3                                                                                                   |             | 6   |                                                                                      | ns       |  |  |

NOTE:

These numbers indicate that the address inputs have a negative setup time and could be valid 1ns after the falling edge of the CP clock. It is suggested that SEL<sub>2</sub> be used to enable Address Bus 2 and the opposite polarity of the same be used, instead of SEL<sub>1</sub> to enable Address Bus 1. This will ensure that setup time for Address Bus 1 is not violated.

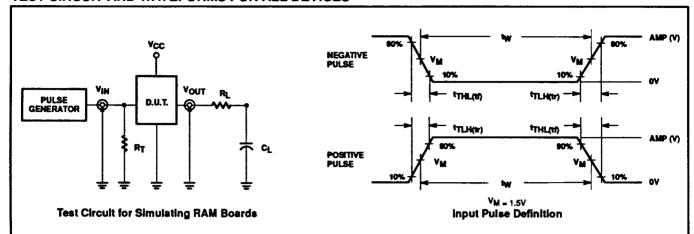

#### **TEST CIRCUIT AND WAVEFORMS FOR ALL DEVICES**

| FAMILY |           | INPUT PULSE REQUIREMENTS |       |                  |                  |  |  |  |  |  |

|--------|-----------|--------------------------|-------|------------------|------------------|--|--|--|--|--|

|        | Amplitude | Rep. Rate                | Tw    | T <sub>TLH</sub> | T <sub>THL</sub> |  |  |  |  |  |

| 74F    | 3.0V      | 1MHz                     | 500ns | 2.5ns            | 2.5ns            |  |  |  |  |  |

#### **DEFINITIONS:**

R<sub>L</sub> = Load resistor to GND, see AC Characteristics for value.

CL = Load capacitance includes jig and probe capacitance; see AC Characteristics for value.

RT = Termination resistance should be equal to Z<sub>OUT</sub> of Pulse Generators.

#### **APPLICATIONS**

The DRAM dual-ported controller can be designed into a wide range of single and dual-port interface configurations. The processors could be general or special-purpose (microcontrollers) and the data bus may differ in size.

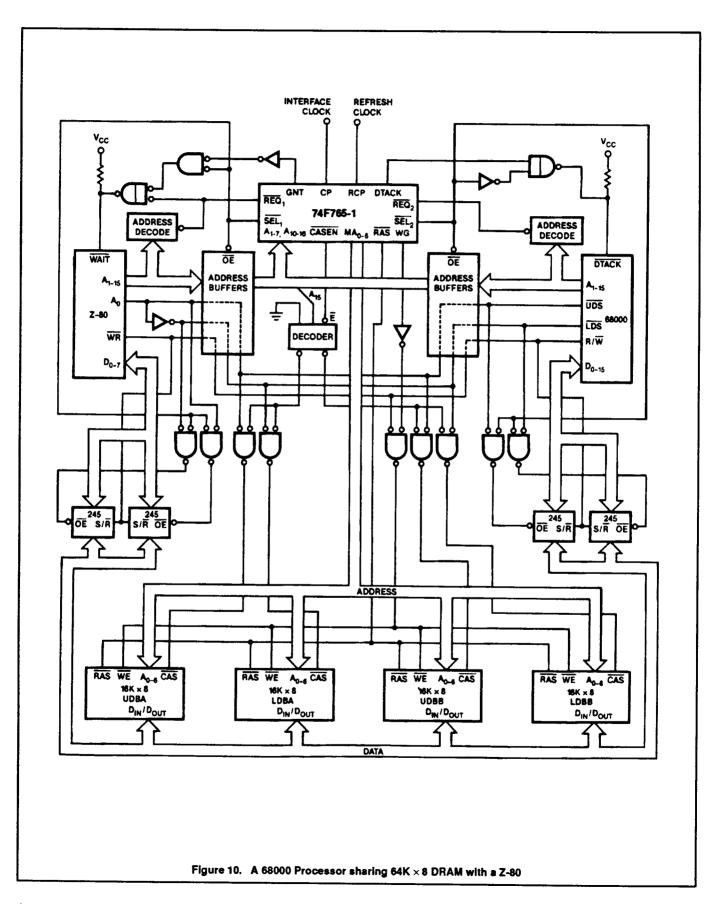

Figure 10 shows a 68000 processor sharing a 64K × 8 (two banks each consisting of sixteen 16K × 1 devices) memory with a Z-80 processor. Since neither Z-80 nor 68000 have multiplexed address and data bus, the 74F765-1 is appropriate.

Since the Z-80 has an 8-bit wide data bus, data buffers are used to convert the 16-bit memory data bus to an 8-bit wide processor

bus. Address bit (A<sub>0</sub>) from the Z-80 serves as an enable to one of the two data buffers at a given time. Address bit (A15) from either the Z-80 or the 68000 distinguishes between Memory Banks A and B. Where Bank A consists of Upper Data Byte A (UDBA) and Lower Data Byte A (LDBA) and Bank B consists of Upper Data Byte B (UDBB) and Lower Data Byte B (LDBB).

When the Z-80 is selected and  $A_{15}$  is a zero, all even bytes will be accessed from UDBA and all odd bytes from LDBA. Similarly, when  $A_{15}$  is a one, UDBB will contain all even bytes and LDBB all odd bytes.

For 68000, Upper and Lower Data Strobes (UDS and LDS) determine whether a byte or

word transfer will take place. The WAIT input on the Z-80 is asserted when REQ<sub>1</sub> is generated, and is negated when the GNT output is asserted by the controller. The additional gating circuitry is to ensure that DTACK to the 68000 is asserted only when it is selected.

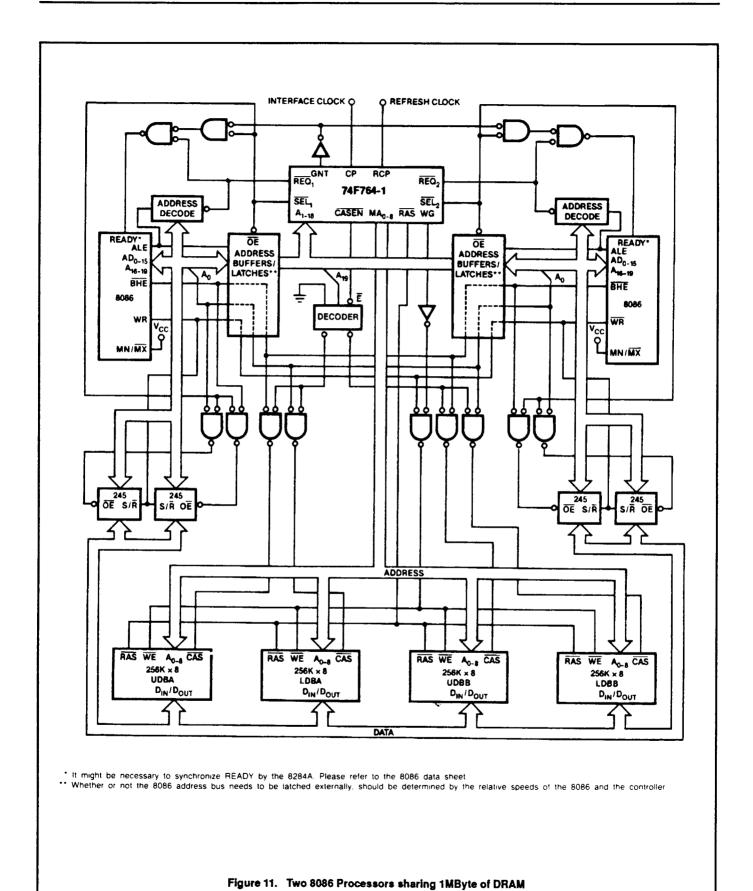

Figure 11 shows two 8086 processors sharing 1MByte (two banks each consisting of sixteen 256K × 1 devices) of dynamic RAM. Using 74F764 in this application may eliminate the need for an external address latch.

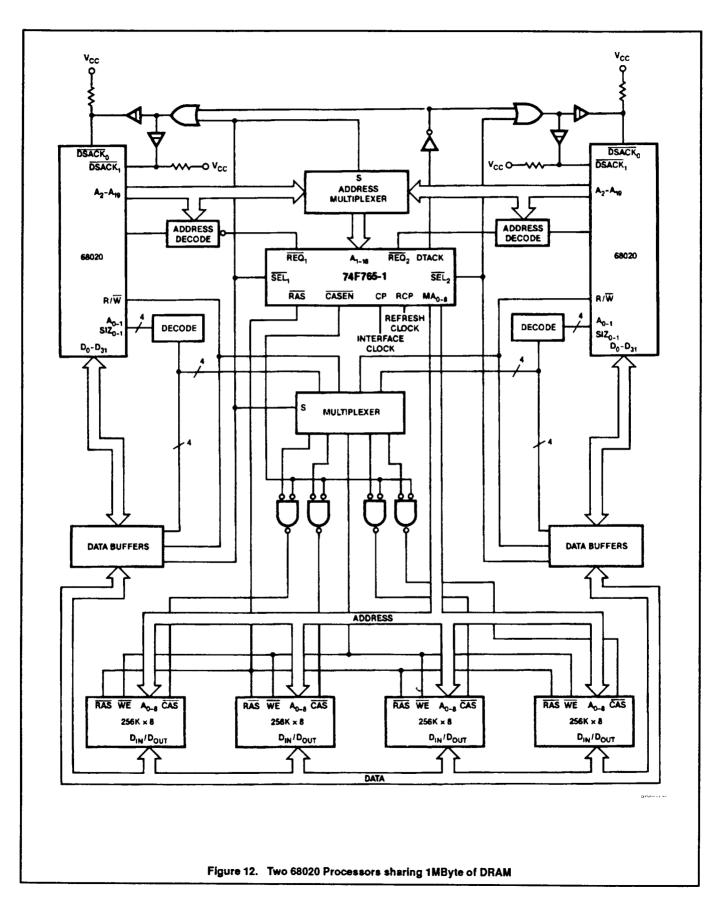

Similarly, Figure 12 shows two 68020 processors sharing the same amount of memory.

### 74F764-1/74F765-1

### 74F764-1/74F765-1

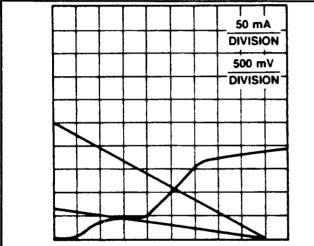

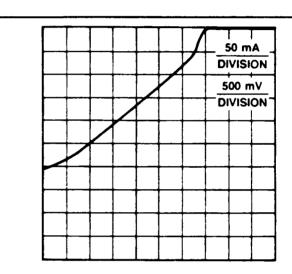

# 74F764-1 FAMILY LINE DRIVING CHARACTERISTICS

The 74F764-1/765-1 are designed to provide first reflected wave switching with as wide a range of characteristic impedances as possible.

The I<sub>OL2</sub>/V<sub>OL2</sub> and I<sub>OH2</sub>/V<sub>OH2</sub> parameters are included in the product specifications to assist engineers in designing systems which will switch memory array signal lines in the above mentioned manner. For example, the characteristic impedance of signal lines in DIP-housed memory arrays is usually around

70Ω. If a signal line has settled out in a High state at 4 volts and must be pulled down to 0.8 volts or less on the incident wave, the DRAM controller output must sink (4-0.8)/70A or 46mA at 0.8 volts. The l<sub>OL2</sub>/V<sub>OL2</sub> parameter indicates that the signal line in question will always be switched on the incident wave over the full commercial operating range.

It should be noted here that I<sub>OL2</sub>/V<sub>OL2</sub> and I<sub>OH2</sub>/V<sub>OH2</sub> are intended for transient use only and that steady state operation at I<sub>OH2</sub> or I<sub>OL2</sub> is not recommended (long term, steady state

operation at these currents may result in electromigration).

Figures 13 and 14 show the output I/V characteristics of the DRAM controller family of devices. These figures also demonstrate a graphical method for determining the first reflected wave characteristics of the devices.

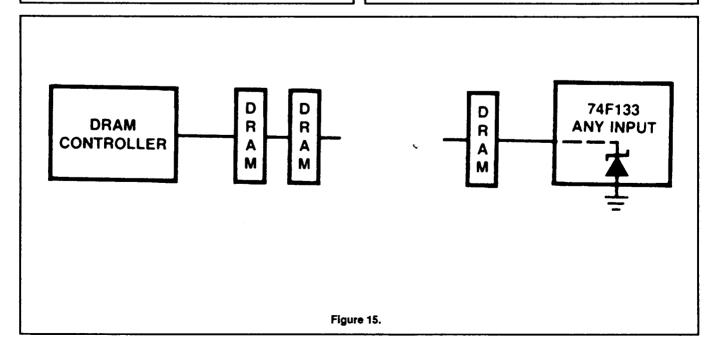

When driving any type of memory arrays with the 74F764-1/765-1, the schottky diode termination shown in Figure 15 can be used (most of these will need no termination at all).

Figure 13. I-V Output characteristics of the 74F764-1 and 765-1 in the Low State. Any unterminated line impedance between 18 $\Omega$  and 70 $\Omega$  (both shown) will typically switch on the first reflected wave without violating the -1V minimum input voltage specification typical of DRAMs.

Figure 14. I-V Output characteristics of the 74F764-1 and 765-1 while in the High state.