#### CMOS 4-BIT MICROCONTROLLER

## TMP47E885AF

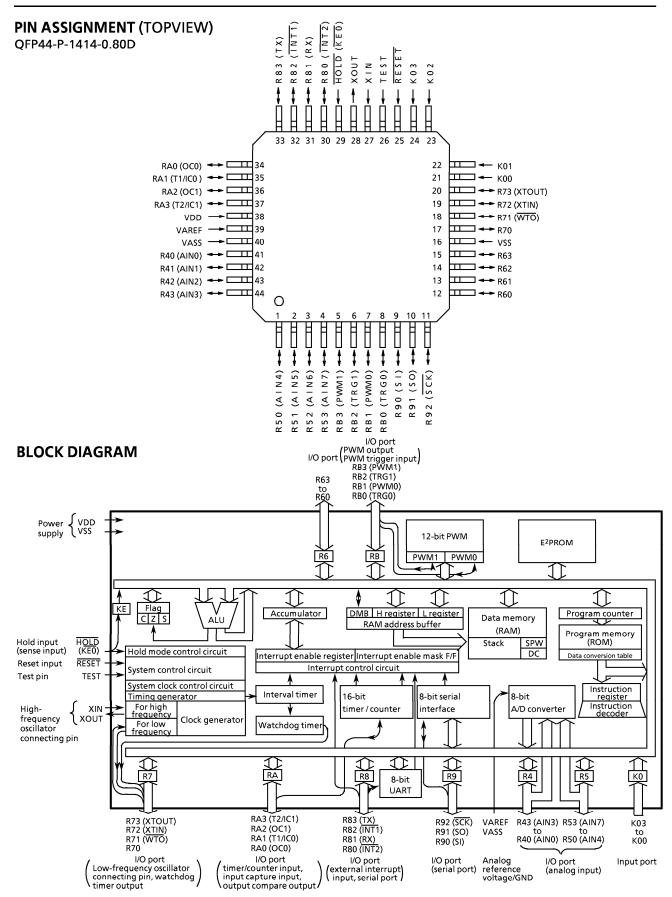

Based on the TLCS-470 series, TMP47E885AF is a high-speed, advanced, single-chip, 4-bit microcomputer with a built-in 64×8-bit E<sup>2</sup>PROM, enhanced timer/counter functions, an 8-bit A/D converter, 12-bit pulse width modulation (PWM) output, and an 8-bit asynchronous serial interface (UART).

| PART No.    | ROM          | E <sup>2</sup> PROM | RAM         | PACKAGE            | OTP        | PIGGYBACK |

|-------------|--------------|---------------------|-------------|--------------------|------------|-----------|

| TMP47E885AF | 8192 × 8-bit | 64 × 8-bit          | 512 × 4-bit | QFP44-P-1414-0.80D | TMP47P885F | -         |

#### **FEATURES**

◆4-bit single chip microcomputer

◆Minimum instruction execution time

: 1.3  $\mu$ s (at 6 MHz), 244  $\mu$ s (32.8 kHz)

◆Basic machine instructions: 92

Table look-up instructions

◆Subroutine nesting: 15 levels max.

◆6 interrupt sources (External: 2, Internal: 4) All sources have independent latches each. and multiple interrupt control is available.

◆I/O port (36 pins)

Input: 2 ports 5 pins I/O: 8 ports 31 pins

Interval timer

◆16-bit timer/counter: one channel

Free running timer, event counter, input capture, output compare

◆Watchdog timer

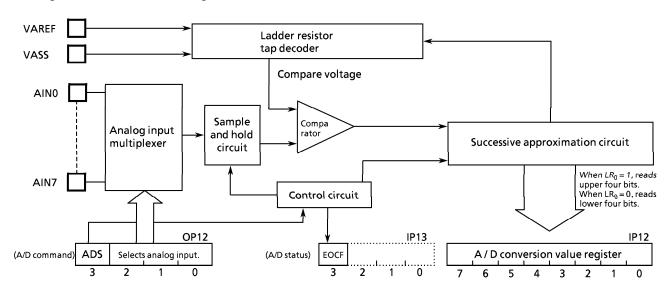

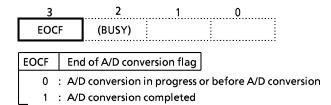

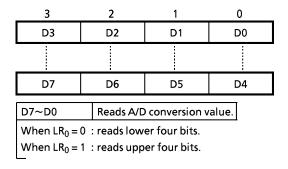

◆8-bit successive approximate type A/D converter

Analog input : 8 channels • Conversion time : 34.6  $\mu$ s (6 MHz)

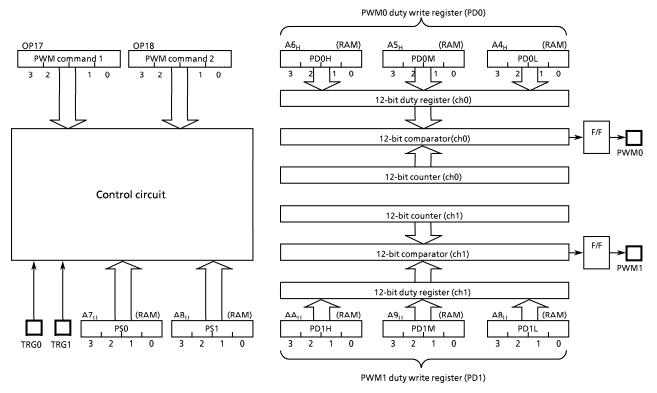

- ◆12-bit pulse width modulation (PWM) output: two channels

- ◆8-bit buffered synchronous serial interface (SIO)

- Simultaneous transmit/receive

- External/internal clock, leading/trailing edge shift, 4-bit/8-bit mode

#### Caution:

Because timer/counter functions have been enhanced, the description of the operation of TC1 and TC2 in the assembler, C-like compiler and software simulator manuals cannot be used.

980901EBP1

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to section its of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or decime. Please appure that TOSHIBA products are used within specified. damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

- ◆8-bit buffered asynchronous serial interface (UART)

- $64 \times 8$ -bit E<sup>2</sup>PROM

- Word-by-word rewrite

- Automatic rewrite time setting (timer built in)

- Ready/Busy status monitor

- ◆Dual-clock mode

High-speed mode /low power consumption operating mode

◆Hold function

battery/capacitor backup

◆Emulator : BM47E885AF0A

## **PIN FUNCTION**

| PIN NAME                    | Input/Output  | Function                                                                                                                                                                                    | (Function)                                            |

|-----------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

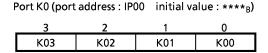

| K03 to K00                  | Input         | 4-bit latched I/O port.                                                                                                                                                                     |                                                       |

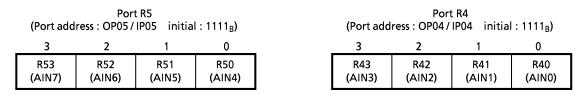

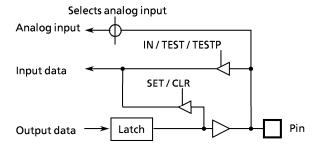

| R53 (AIN7)<br>to R40 (AIN0) | I/O (Input)   | When using as an input port or for analog input, set the latch to 1. Can be set, cleared, or tested in units of bits by bit manipulation instructions using L register indirect addressing. | A/D converter analog input                            |

| R63 to R60                  | I/O           | 4-bit latched I/O port.  When using as input port, set latch to 1.  Can be set, cleared, or tested in units of bits by bit manipulation instructions using                                  |                                                       |

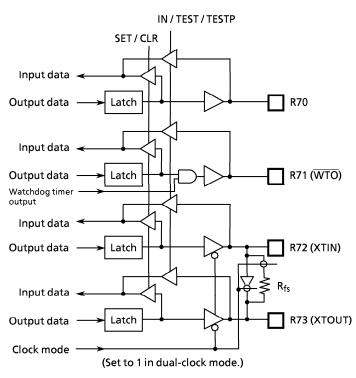

| R73 (XTOUT)                 | I/O (Output)  | 4-bit latched I/O port. When using R73 and R72 as oscillators, set to dual-clock mode.                                                                                                      | Oscillator connecting pin (low frequency).            |

| R72 (XTIN)                  | I/O (Input)   | When using as input port or for watchdog timer output, set latch to 1.  Can be set, cleared, or tested in units of                                                                          | Input an external clock to XIN. XOUT is open circuit. |

| R71 (WTO)                   | I/O (Output)  | bits by bit manipulation instructions using<br>L register indirect addressing.                                                                                                              | Watchdog timer output                                 |

| R70                         | I/O           |                                                                                                                                                                                             |                                                       |

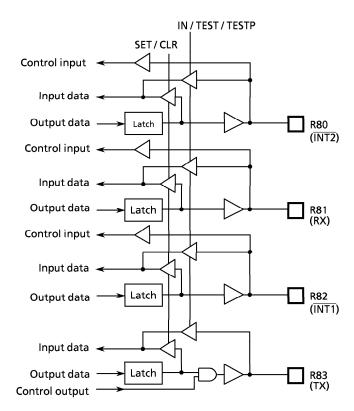

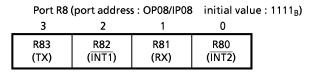

| R83 (TX)                    | I/O (Output)  | 4-bit latched I/O port. When using as input                                                                                                                                                 | Asynchronous serial data output                       |

| R82 (INT1)                  |               | port, as external interrupt input pin, or as asynchronous serial port (UART) pin, set                                                                                                       | External interrupt 1 input                            |

| R81 (RX)                    | I/O (Input)   | latch to 1.                                                                                                                                                                                 | Asynchronous serial data input                        |

| R80 (INT2)                  |               |                                                                                                                                                                                             | External interrupt 2 input                            |

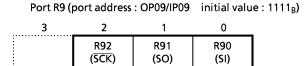

| R92 (SCK)                   | I/O (I/O)     | 3-bit latched input/output port. When using as input port or synchronous serial                                                                                                             | Synchronous serial clock input/output                 |

| R91 (SO)                    | I/O (Output)  | port, set latch to 1.                                                                                                                                                                       | Synchronous serial data output                        |

| R90 (SI)                    | I/O (Input)   |                                                                                                                                                                                             | Synchronous serial data input                         |

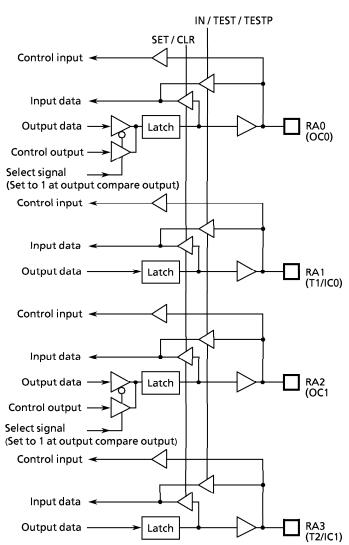

| RA3 (T2/IC1)                | I/O (Input)   | 4-bit latched input/output port. When using as input port or for timer/input                                                                                                                | Timer/input capture 1 input                           |

| RA2 (OC1)                   | I/O (Output)  | capture input, set latch to 1.                                                                                                                                                              | Output compare 1 output                               |

| RA1 (T1/IC0)                | I/O (Input)   |                                                                                                                                                                                             | Timer/input capture 0 input                           |

| RA0 (OC0)                   | I/O (Output)  |                                                                                                                                                                                             | Output compare 0 output                               |

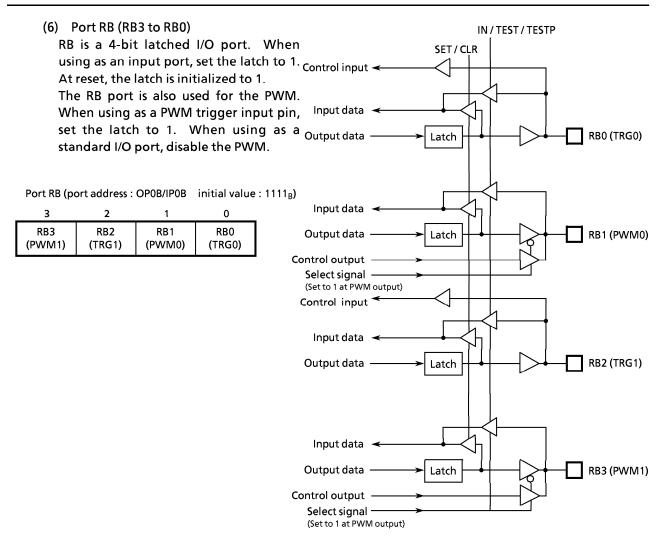

| RB3 (PWM1)                  | I/O (Output)  | 4-bit latched input/output port. When using as input port or for PWM trigger                                                                                                                | PWM 1 output                                          |

| RB2 (TRG1)                  | I/O (Input)   | input, set latch to 1.                                                                                                                                                                      | PWM trigger 1 input                                   |

| RB1 (PWM0)                  | I/O (Output)  |                                                                                                                                                                                             | PWM 0 output                                          |

| RB0 (TRG0)                  | I/O (Input)   |                                                                                                                                                                                             | PWM trigger 0 input                                   |

| XIN                         | Input         | Oscillator connecting pin (high frequency).                                                                                                                                                 |                                                       |

| XOUT                        | Output        | Input an external clock to XIN. XOUT is open                                                                                                                                                | circuit.                                              |

| RESET                       | Input         | Reset signal input                                                                                                                                                                          |                                                       |

| HOLD (KEO)                  | Input (Input) | Hold request/release signal input                                                                                                                                                           | Sense input                                           |

| TEST                        | Input         | Delivery test pin. Fix at low level.                                                                                                                                                        |                                                       |

| Pin Name | Input/Output       | Function                                    | (Function) |  |  |

|----------|--------------------|---------------------------------------------|------------|--|--|

| VDD      | Devices events     | + 5V                                        |            |  |  |

| VSS      | Power supply       | 0V (GND)                                    |            |  |  |

| VAREF    | Deverage annual co | Analog reference voltage for A/D conversion |            |  |  |

| VASS     | Power supply       | Analog reference GND for A/D conversion     |            |  |  |

#### **OPERATIONAL DESCRIPTION**

#### 1. SYSTEM CONFIGURATION

- ◆ CPU Core Functions

- 2.1 Program Counter (PC)

- 2.2 Program Memory (ROM)

- 2.3 H register, L register, DMB selector

- 2.4 Data Memory (RAM)

- Stack

- Stack pointer word (SPW)

- Data counter (DC)

- 2.5 ALU and Accumulator

- 2.6 Flags

- 2.7 System Control Circuit

- 2.8 Interrupt Control Circuit

- 2.9 Reset Circuit

- Hardware Functions

- 3.1 I/O Ports

- 3.2 Interval Timer

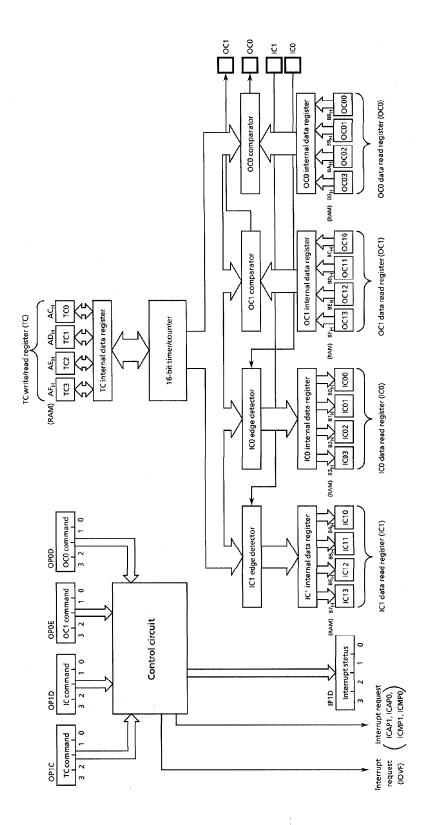

- 3.3 Timer/Counter

- 3.4 Watchdog Timer

- 3.5 A/D Converter

- 3.6 PWM

- 3.7 Serial Interface

- 3.8 E<sup>2</sup>PROM

The following sections describe the hardware configuration and operation for the above components.

## 2. CPU Core Functions

## 2.1 Program Counter (PC)

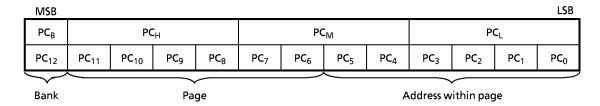

The program counter is a 13-bit register that indicates the address of the next program instruction to be executed. At each instruction fetch, the register is incremented by the number of bytes fetched.

Table 2.1 shows the operation of the program counter when a branch or subroutine instruction is executed, or an interrupt is received. At reset, the PC is initialized to 0.

Figure 2-1. Configuration of Program Counter

The program counter directly addresses 8192 bytes of memory. Note the following points concerning short and middle branch instructions and subroutine instructions.

## (1) Short branch instruction [BSS a]

If the branch condition is satisfied when the [BSS a] instruction is executed, the branch value specified by the instruction is set in the lower six bits of the PC. That is, the [BSS a] instruction is a inpage branch instruction.

If the [BSS a] instruction occurs at the final address in a page, the upper seven bits of the PC point to the next instruction, which is in the next page. Therefore, the instruction will branch to an address within the next page.

#### (2) Middle branch instruction [BS a]

If the branch condition is satisfied when the [BS a] instruction is executed, the branch value specified by the instruction is set in the lower twelve bits of the PC. That is, the [BS a] instruction is a in-bank branch instruction.

If the first byte or the second byte of the [BS a] instruction is stored at the final bank address, the MSB of the PC points to the next bank. Therefore, the instruction will branch to an address within the next bank.

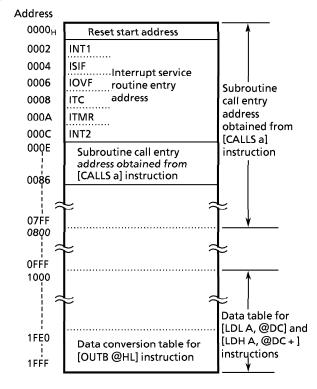

## (3) Subroutine call instruction [CALL a]

After the contents of the program counter are saved to the stack when the [CALL a] instruction is executed, the call value specified by the instruction is set in the PC. Addresses specifiable with this instruction are 11-bit addresses. The upper two bits of the PC are always set to 0. Therefore, the start address of the subroutine must be 0000 - 07FF<sub>H</sub>.

|          | struction<br>or<br>peration | Condition                                                                      | Program Counter (PC)  PC <sub>12</sub> PC <sub>11</sub> PC <sub>10</sub> PC <sub>9</sub> PC <sub>8</sub> PC <sub>7</sub> PC <sub>6</sub> PC <sub>5</sub> PC <sub>4</sub> PC <sub>3</sub> PC <sub>2</sub> PC <sub>1</sub> PC <sub>0</sub> |  |  |

|----------|-----------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|          | BSL a                       | SF = 1<br>(branch condition satisfied)                                         | Immediate data specified by instruction                                                                                                                                                                                                  |  |  |

|          |                             | SF = 0 (branch condition not satisfied)                                        | + 3                                                                                                                                                                                                                                      |  |  |

| ے        |                             | Lower 12 bits of address<br># FFE, FFF <sub>H</sub>                            | No Immediate data specified by instruction                                                                                                                                                                                               |  |  |

| c t i o  | BS a                        | Lower 12 bits of address<br>= FFE, FFF <sub>H</sub><br>(final address in bank) | + 1 Immediate data specified by instruction                                                                                                                                                                                              |  |  |

| ے<br>ت   |                             | SF = 0                                                                         | + 2                                                                                                                                                                                                                                      |  |  |

| n s t    |                             | Lower six bits of address $\neq 3F_H$                                          | No change Immediate data specified by instruction                                                                                                                                                                                        |  |  |

| <u> </u> | BSS a                       | Lower six bits of address<br>= 3F <sub>H</sub><br>(final address in page)      | + 1 Immediate data specified by instruction                                                                                                                                                                                              |  |  |

| ٥        |                             | SF = 0                                                                         | + 1                                                                                                                                                                                                                                      |  |  |

| 0        | CALL a                      |                                                                                | 0 0 Immediate data specified by instruction                                                                                                                                                                                              |  |  |

| xecut    | CALLS a                     |                                                                                | Value generated from immediate data specified 0 0 0 0 0 by instruction 1 1 0                                                                                                                                                             |  |  |

| l iii    | RET                         |                                                                                | Return address restored from the stack                                                                                                                                                                                                   |  |  |

|          | RETI                        |                                                                                | Return address restored from the stack                                                                                                                                                                                                   |  |  |

|          | Other instruction           |                                                                                | Incremented by the number of bytes of instruction                                                                                                                                                                                        |  |  |

| At i     | interrupt<br>eption         |                                                                                | 0 0 0 0 0 0 0 0 0 Interrupt vector 0                                                                                                                                                                                                     |  |  |

|          | At reset                    |                                                                                | 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                  |  |  |

Table 2-1. Status Change of Program Counter

## 2.2 Program Memory (ROM)

Programs and fixed data are stored in program memory. The program counter indicates the address of the next instruction to be executed.

(1) Table look-up instructions [LDL A, @DC], [LDH A, @DC+]

The table look-up instructions read the upper or lower four bits of data stored at the ROM address specified by the data counter (DC) and load the bits to the accumulator. (The instruction [LDL A, @DC] reads the lower four bits. The instruction [LDH A, @DC+] reads the upper four bits.) The DC is 12 bits in length and can specify addresses 1000 - 1FFF<sub>H</sub> in program memory.

(2) 5 - to 8-bit data conversion instruction [OUTB @HL]

The 5 - to 8-bit data conversion instruction reads the fixed (8-bit) data stored in the data conversion table in program memory (1FE0 - 1FFF<sub>H</sub>). The instruction specifies the upper four bits to be output to port 2 and the lower four bits to be output to port 1. However, do not use this instruction because the operation is invalid as there is no port 1 or port 2.

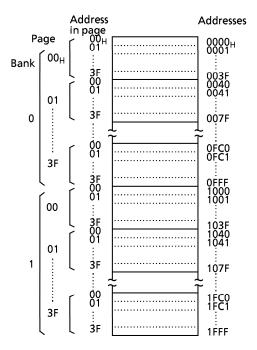

## 2.2.1 Program Memory Map

Figure 2-3 shows the program memory map. Program memory addresses 0000 - 0086<sub>H</sub> and the final 32-byte space can also be used for special applications.

#### 2.2.2 Program Memory Capacity

The processor incorporates 8192 x 8 bits (0000 -  $1FFF_H$ ) of program memory (mask ROM).

Figure 2-2. Configuration of Program Memory

Figure 2-3. Program Memory Map

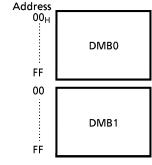

## 2.3 H Register, L Register, and Data Memory Bank Selector (DMB)

The H and L registers are 4-bit general-purpose registers. The two registers can be used as a pair, called the HL register, which can be used as a pointer to indicate a RAM data memory address. The data memory has a page structure with 16 words per page. The H register indicates the page and the L register indicates the address within the page. The data memory consists of two banks (bank 0 and bank 1). The data memory bank selector (DMB) is a 1-bit register. It specifies the data memory bank. Set the DMB using the [CLR DMB] and [SET DMB] instructions. The [TEST DMB] and [TESTP DMB] instructions can be used to ascertain which bank is currently selected. At reset, DMB is initialized to 0.

The L register has an auto post-increment or decrement feature, which permits compound instructions. For example, the [ST A,@HL+] instruction automatically increments the contents of the L register after data transfer.

Similarly, the L register is used to specify the bit corresponding to the I/O port (pins R73 - R40) when the [SET @L], [CLR @L], or [TEST @L] instructions are executed (indirect addressing of the port bits using the L register).

Specifies bank

Example 1: Write immediate values 5 and F<sub>H</sub> to data memory addresses 10<sub>H</sub> and 11<sub>H</sub> respectively.

CLR DMB LD HL, #10H ST #5, @HL + ST #0FH, @HL +

Example 2: Use a bit manipulation instruction to set the pin R71 output latch to 1 with L register indirect addressing.

LD L, #1101B SET @L

DMB

H register

L register

HR3

HR2

HR1

HR0

LR3

LR2

LR1

LR0

Specifies address within page

Figure 2-4. configuration of H Register, L Register, and DMB

Specifies page

## 2.4 Data Memory (RAM)

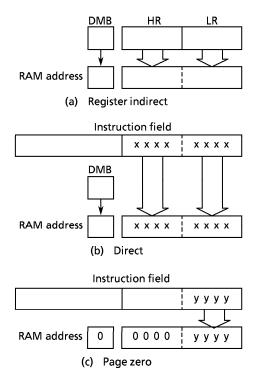

Data memory is used to save user data. Data memory consists of eight pages each consisting of 16 words (4-bit words). Data memory addresses can be specified by the following methods:

#### (1) Register indirect addressing mode

The DMB specifies the bank. The H register specifies the page. The L register specifies the RAM address within the page.

Example: LD A, @HL ; Acc ← RAM [HL]

## (2) Direct addressing mode

The second byte of the instruction field (operand) specifies an address in the bank. The DMB specifies the bank.

Example: LD A, 2CH;  $Acc \leftarrow RAM[2C_H]$

#### (3) Page zero addressing mode

The lower four bits in the second byte of the instruction field (operand) specify an address in page zero (00 -  $0F_H$ ) of bank 0.

Example: ST #3, 05H; RAM  $[05_H] \leftarrow 3$

Figure 2-5. Addressing Modes

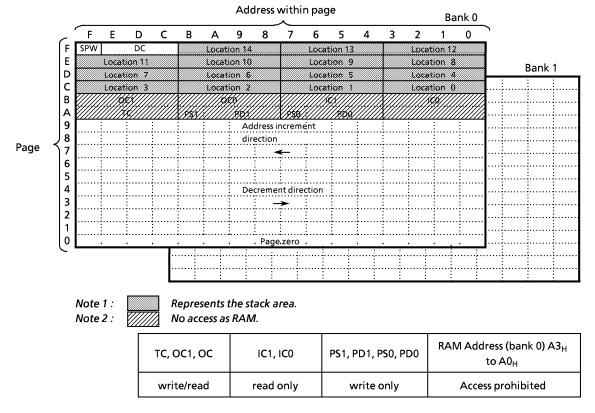

## 2.4.1 Data Memory Map

Figure 2-6 shows the data memory map. Data memory is also used for the following purposes, but only in bank 0.

- ① Stack

- ② Stack pointer word (SPW)

- 3 Data counter (DC)

- Timer/counter register (TC, IC1, IC0, OC1, OC0)

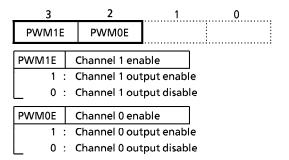

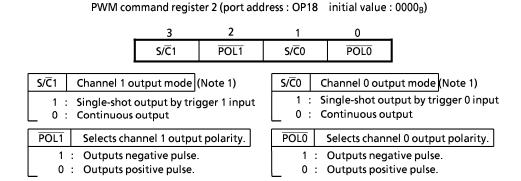

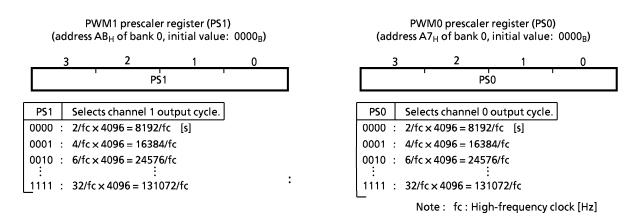

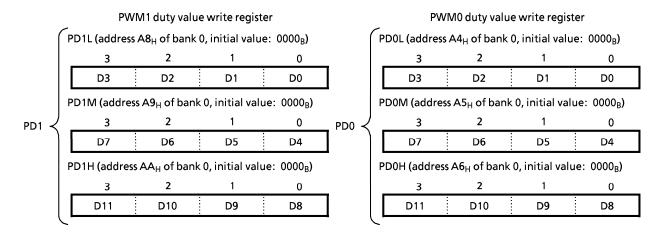

- 5 PWM output register (PD1, PD0, PS1, PS0)

- 6 Page zero

Figure 2-6. Data Memory Map

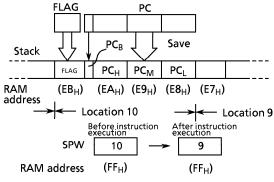

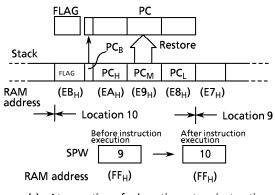

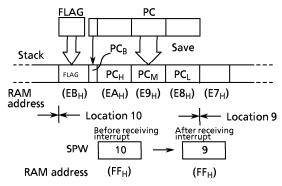

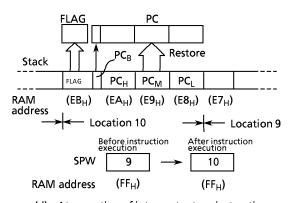

## (1) Stack

The stack area is used to save the contents of the program counter (return address) and flags when a subroutine call instruction is executed or an interrupt received. The processor saves the data to the stack before jumping to the processing routine.

When returning from the processing routine, the subroutine return instruction [RET] restores the contents of the program counter from the stack. The interrupt return instruction [RETI] restores the contents of the program counter and flags from the stack.

The stack is allocated to data memory addresses  $C0 - FB_H$  in bank 0, providing a maximum of 15 levels (locations 14 to 0). Each stack level consists of four words of data memory.

The save/restore stack location is determined by the stack pointer word. The stack pointer word is automatically decremented after saving, and automatically incremented prior to restoring. That is, the stack pointer word holds the next free location on the stack.

### (2) Stack pointer word (SPW)

Data memory address FF<sub>H</sub> (in bank 0) is known as the stack pointer word. The SPW determines the location when the stack is accessed (saving or restoring).

The stack pointer word is normally in the range 0 to 14, allowing up to 15 levels of nesting. Because the stack pointer word is allocated to address FF<sub>H</sub>, the contents of the stack pointer word may never be 15.

The stack pointer word is automatically rewritten at subroutine calls and on receipt of interrupts. Note that if the stack exceeds the area allocated to the stack in data memory, user data are corrupted. (For example, if the user data area is allocated to address range 00 - CF<sub>H</sub>, the stack area is available up to location 4. If an interrupt is received while location 4 is in use, the user data at addresses CC - CF<sub>H</sub> corresponding to location 3 are corrupted.)

The stack pointer word is not initialized by hardware. Use a software initialization routine to write initial value 14 (the number of the first stack location to use).

Example: Stack pointer word initial setting LD A, #14 CLR DMB ST A, 0FFH

(a) At execution of subroutine call instruction

(c) At execution of subroutine return instruction

(b) At interrupt reception

(d) At execution of interrupt return instruction

Figure 2-7. Stack Access (Save/Restore)

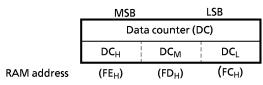

## (3) Data Counter (DC)

The data counter is a 12-bit counter used to specify the address of the data table in program memory (ROM). The data table is referenced by the table look-up instructions [LDL A, @DC] and [LDH A, @DC+]. Data tables can be allocated from address 1000<sub>H</sub> in the program memory area (the MSB of the PC is fixed to 1).

The data counter is allocated to RAM addresses in units of 4 bits. Use the RAM manipulation instructions to set initial values or read the contents of the data counter.

Figure 2-8. Data Counter

Example: Set the data counter to 780H

| CLR | DMB       |

|-----|-----------|

| LD  | HL, #0FCH |

| ST  | #0H, @HL+ |

| ST  | #8H, @HL+ |

| ST  | #7H, @HL+ |

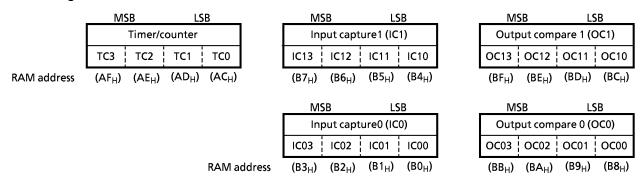

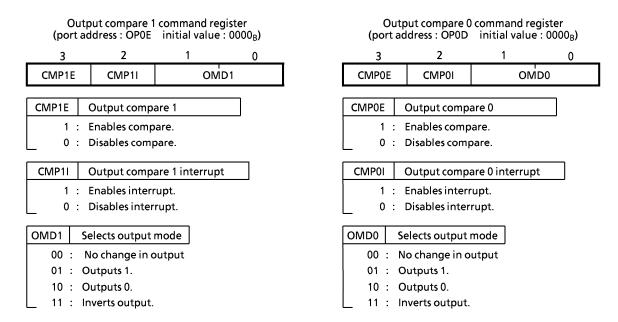

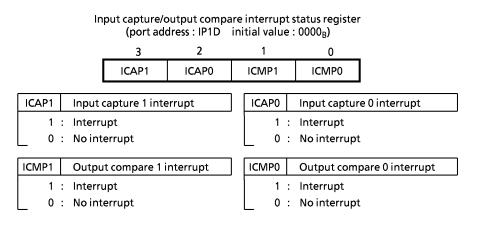

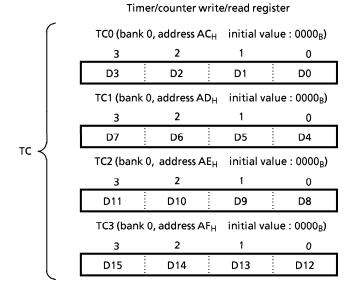

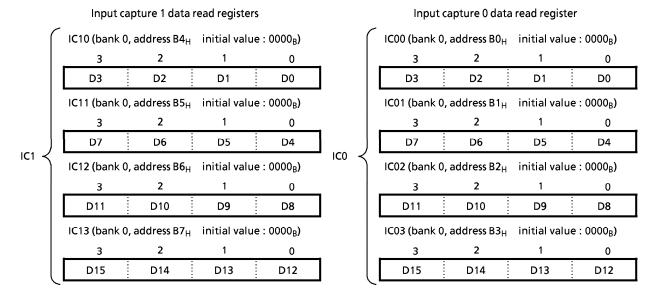

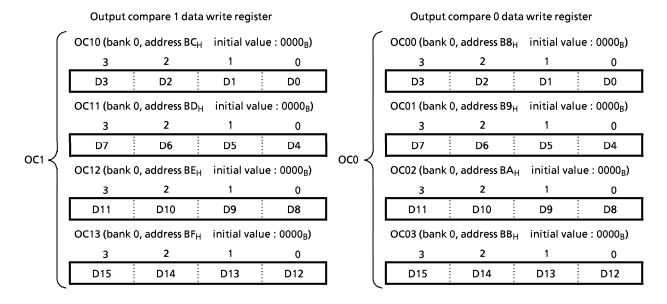

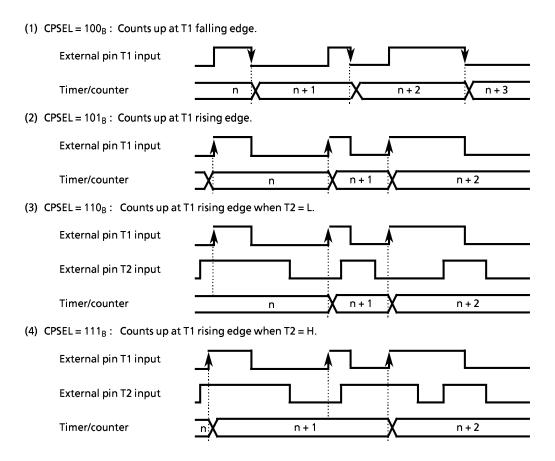

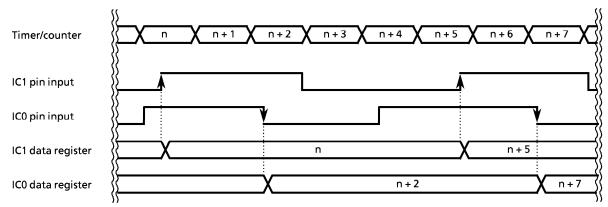

## (4) Timer/Counter Registers (TC, IC1, IC0, OC1, OC0)

The timer/count registers are allocated to RAM in units of 4 bits. Use the RAM manipulation instructions to set initial values or read the contents of the count registers.

However, because the data memory at addresses corresponding to the registers cannot be accessed as RAM, the data memory cannot be used to store user data. Registers IC1 and IC0 are read only. Registers TC, OC1, and OC0 can be read or written.

Figure 2-9. Timer/Counter Registers

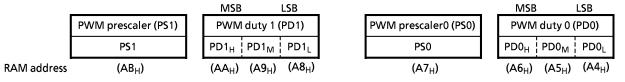

#### (5) PWM output registers (PD1, PD0, PS1, PS0)

The PWM output registers are allocated to RAM in units of 4 bits. Use the RAM manipulation instructions to set initial values.

However, because the data memory at addresses corresponding to the registers cannot be accessed as RAM, the data memory cannot be used to store user data. Registers PD1, PD0, PS1, and PS0 are write only.

Figure 2-10. PWM Output Register

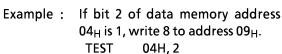

#### (6) Page Zero

The sixteen words of (bank 0) page zero (addresses 00 - 0F<sub>H</sub>) data memory can be used for user flags and pointers by utilizing the page zero addressing mode instructions (compare, add, transfer, and bit manipulation). This enables a highly efficient program.

B SKIP ST #8,09H

SKIP:

## 2.4.2 Data Memory Capacity

47E885AF provides 256 x 4 bits of two internal data memory (RAM) banks (bank 0 and bank 1). Because the contents of the data memory are undefined when the power supply is switched on, set initial values using the initializing routine.

Example: Clear RAM. HL, #00H LD SCLR1:CLR **DMB** #0, @HL+ SCLR2:ST SCLR2 R **SET DMB** SCLR3:ST #0, @HL+ В SCLR3 ADD H, #1

В

SCLR1

Figure 2-11. Data Memory

## 2.5 ALU and Accumulator

#### 2.5.1 ALU

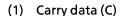

The ALU (arithmetic logic unit) performs operations on 4-bit binary data. The ALU Note: Cin indicates the carry executes an instruction and outputs the (4-bit) input specified by the operation result, carry data (C), and zero detect data (Z).

In additions, the carry data represent the carry from the uppermost bit. As subtraction is processed as a two's complement addition, carry data indicate no borrow from the lowest bit. For rotation instructions, carry data indicate that data shifted out of the accumulator.

#### (2) Zero detect data (Z)

The processor sets zero detect to 1 when an operation result or data transfer to the accumulator or data memory is 0000<sub>B</sub>.

#### 2.5.2 Accumulator (Acc)

The accumulator is a 4-bit register used to store the source and result data for operations.

Figure 2-12. ALU

Example: Carry data (C) and zero detect data (Z) resulting from 4-bit addition and subtraction.

|   | Operation |   | ration result            | C | Z |

|---|-----------|---|--------------------------|---|---|

|   | 4 + 2     | = | 6                        | 0 | 0 |

|   | 7 + 9     | = | 0                        | 1 | 1 |

|   | 8 – 1     | = | 7                        | 1 | 0 |

|   | 2 – 2     | = | 0                        | 1 | 1 |

|   | 5 – 8     | = | – 3 (1101 <sub>B</sub> ) | 0 | 0 |

|   | MSB       |   | LSB                      |   |   |

| 3 | 2         |   | 1                        | 0 |   |

|   |           |   |                          |   |   |

Figure 2-13. Accumulator

## 2.6 Flags (FLAG)

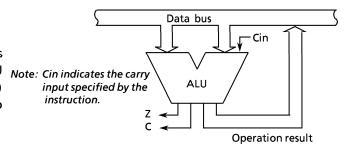

47E885AF has a carry flag (CF), zero flag (ZF), and status flag (SF). The flags are set or cleared depending on conditions specified by the instruction.

When an interrupt is received, the flags are saved to the stack together with the program counter. Executing the interrupt return instruction [RETI] restores the flags from the stack. This restores the state immediately prior to receiving the interrupt.

Figure 2-14. Flag

### (1) Carry flag (CF)

The carry flag stores the carry data from the ALU at execution of an addition or subtraction instruction with carry, execution of a compare instruction, or execution of a rotate instruction. When a carry flag test instruction is executed, the value specified by instruction is set in the carry flag.

- 1. Addition or subtraction instruction with carry [ADDC A,@HL] [SUBRC A,@HL]

The carry flag is used as an ALU input (Cin) and to store the carry data (carry/non-borrow).

- 2. Compare instructions [CMPR A,@HL] [CMPR A,#k]

The carry flag is shifted into the accumulator and stores the carry data (data shifted out of

- the accumulator).

- 3. Rotate instructions [ROLC A], [RORC A]

The carry flag is shifted into the accumulator and stores the carry data (data shifted out of the accumulator).

- 4. Carry flag test instructions [TESTP CF], [TEST CF]

- The [TESTP CF] instruction transfers the contents of the carry flag to the status flag. After the transfer, the carry flag is set to 1.

- The [TEST CF] instruction transfers an inverted carry to the status flag. After the transfer, the carry flag is cleared to 0.

#### (2) Zero flag (ZF)

The zero flag stores the zero detect data (Z) from the ALU at the execution of an arithmetic instruction, a rotate instruction, an input instruction, or an instruction to transfer to the accumulator. The [TESTP ZF] instruction transfers the contents of the zero flag to the status flag.

#### (3) Status flag (SF)

The status flag contains the branch conditions for branch instructions. A branch occurs if the status flag is 1. The status flag is normally set to 1; branch with the status flag set to 1 is regarded as an unconditional branch instruction. A branch made immediately after the status flag is set/cleared according to the condition satisfied by the instruction is regarded as a conditional branch instruction. The status flag is initialized to 1 at reset. (Other flags are not initialized.)

Example: The table below lists the values of the accumulator and the flags after execution of the instructions in the table. Prior to the execution, the values are as follows: accumulator: CH H register: 0 L register: 7 Address 07<sub>H</sub> in data memory: 5 carry flag: 1

| Instruction |        | Acc after       | Flag af | ter exe | cution |

|-------------|--------|-----------------|---------|---------|--------|

|             |        | execution       | CF      | ZF      | SF     |

| ADDC        | A, @HL | 2 <sub>H</sub>  | 1       | 0       | 0      |

| SUBRC       | A, @HL | 9 <sub>H</sub>  | 0       | 0       | 0      |

| CMPR        | A, @HL | C0 <sub>H</sub> | 0       | 0       | 1      |

| AND         | A, @HL | 4 <sub>H</sub>  | 1       | 0       | 1      |

| LD          | A, @HL | 5 <sub>H</sub>  | 1       | 0       | 1      |

| Instruction |       | Acc after      | Flag at | ter exe | cution |

|-------------|-------|----------------|---------|---------|--------|

|             |       | execution      | CF      | ZF      | SF     |

| LD          | A, #0 | 0 <sub>H</sub> | 1       | 1       | 1      |

| ADD         | A, #4 | 0 <sub>H</sub> | 1       | 1       | 0      |

| DEC         | Α     | B <sub>H</sub> | 1       | 0       | 1      |

| ROLC        | Α     | 9 <sub>H</sub> | 1       | 0       | 0      |

| RORC        | Α     | E <sub>H</sub> | 0       | 0       | 1      |

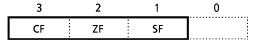

## 2.7 System Control Circuit

Figure 2-15 shows the configuration of the system control circuit.

Figure 2-15. System Control Circuit Configuration

## 2.7.1 Clock Generator (CG)

The clock generator is a circuit to generate the fundamental clock, which is the reference for the system clock supplied to the CPU and peripheral hardware. The processor incorporates two types of oscillator circuits: one for the high-frequency clock and one for the low-frequency clock. To reduce power dissipation, switch to low-speed operation using the low-frequency clock in the system clock control circuit or completely stop the CPU.

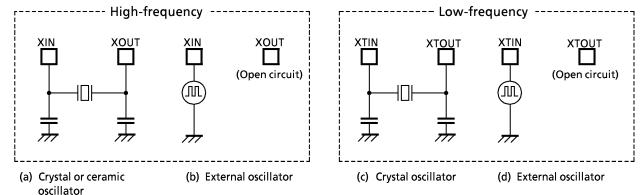

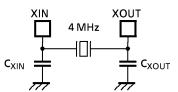

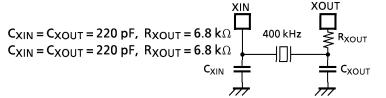

A high-frequency clock and low-frequency clock can be easily obtained by connecting an oscillator respectively to the XIN and XOUT pins, or the XTIN and XTOUT pins. A clock can also be input from an external oscillator.

Figure 2-16. Oscillator Connection Examples

\* Precise adjustment of oscillation frequency

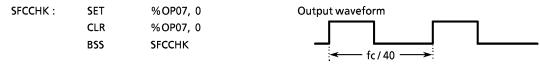

The hardware does not provide the capability to directly monitor the fundamental clock externally. However, if interrupts are inhibited and the watchdog timer is halted, output pulses can be programmed to a port with a fixed frequency. The pulse can be monitored and the frequency adjusted. Create such a program for use in adjusting the oscillator frequency in systems that require such adjustment.

Example: Output a pulse (fc: 40Hz) to R70 for monitoring and adjustment of high-frequency oscillation.

## 2.7.2 Timing Generator (TG)

## (1) Timing generator configuration

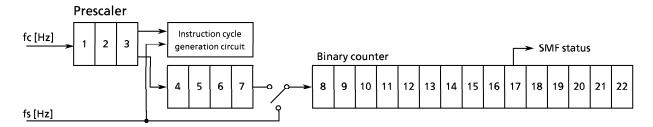

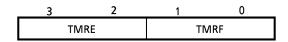

The timing generator consists of a 3-step prescaler, a 19-step binary counter, and an instruction cycle generator circuit. The input step and the clock input to the timing generator are set as follows according to the operating mode selected by the system clock control command register (OP16). The binary counter is cleared to 0 at reset. However, the prescaler is not cleared.

- 1. In single-clock mode

The high-frequency clock (fc) is input to the timing generator first step. In this mode, SLCK (bit 2 of command register OP16) must be cleared to 0.

- 2. In dual-clock mode

In this mode, the fc is input at the first step. The seventh and eighth steps are separated. The clock input to the eighth step can be selected by SLCK (bit 2 of command register OP16). Setting SLCK inputs fs, while clearing SLCK inputs fc/27. In slow mode, the oscillation of the high-frequency clock stops and fs is automatically input to the eighth step. The divider output from step 1 to step 7 is halted. Figure 2-17 shows the timing generator configuration.

Figure 2-17. Timing Generator Configuration

## (2) Timing generator functions

The timing generator functions are:

- 1. Generate instruction cycles

- 2. Generate internal pulses for the interval time

- 3. Generate internal serial clocks for serial interface

- 4. Warming-up counter when a hold is released

- 5. Generate clock source for watchdog timer

## 2.7.3 System Clock Control Circuit

The system clock control circuit controls the timing generators. It also operates or halts the oscillator circuits for the high-frequency clock and low-frequency clock.

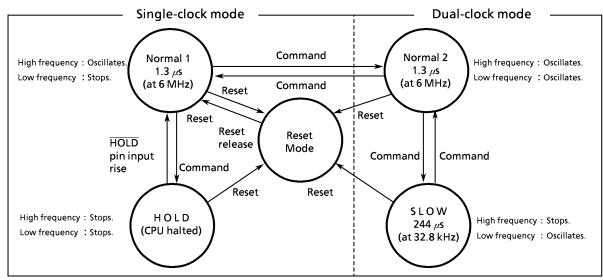

The CPU can operate in single-clock or dual-clock mode depending on the command.

Note: Normal 1 and 2 operating modes are known collectively as normal operating mode.

Figure 2-18. Operating Mode Transition Dialgram

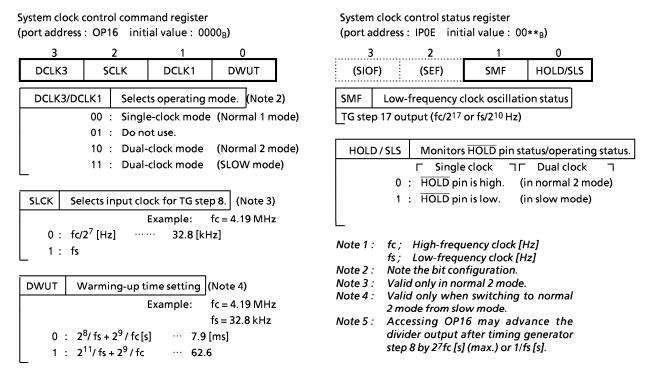

#### (1) System clock control

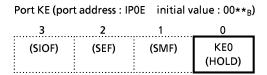

The command register (OP16) controls system clock. At reset, the register is set to 0, selecting single-clock mode. When operating modes are switched, all states can be read from the status register (IP0E).

Figure 2-19. System Clock Control Command Register/Status Register

#### (2) Instruction Cycle

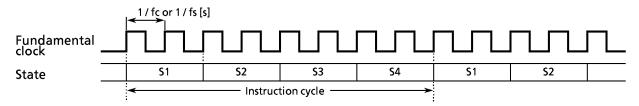

Instruction execution and internal hardware operation are synchronized with the fundamental clock.

The minimum unit of instruction execution is called an instruction cycle. Single-cycle instructions require one instruction cycle to execute; two-cycle instructions require two instruction cycles to execute. While three-cycle instructions require three instruction cycles to execute.

Instruction cycles consist of four states (S1 to S4). Each state consists of two fundamental clocks.

Figure 2-20. Instuction Cycle

## 2.7.4 Operation Mode

Operating mode consists of single-clock mode, which uses only the oscillator circuit for the high-frequency clock, and dual-clock mode, which uses the two types of oscillator circuits.

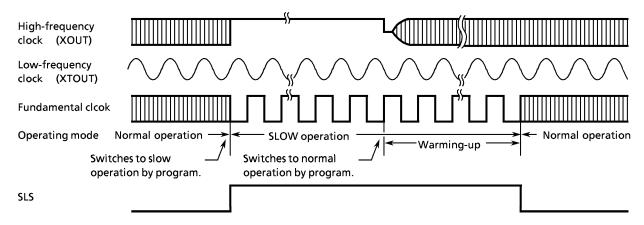

#### (1) Dual-clock mode

Dual-clock mode usually performs normal 2 operation, which generates instruction cycles from the high-frequency clock (fc). If necessary, slow operation can be performed by generating instruction cycles from the low-frequency clock (fs). The following describes switching between normal 2 and slow operation in dual-clock mode. At reset, the command register is initialized to single-clock mode and the low-frequency clock is stopped, so set to normal 2 operation in dual-clock mode. Switching to normal 2 mode starts the low-frequency clock.

## a. Switching from normal 2 to slow operation

Setting DCLK1 (OP16 bit 1) to 1 switches to slow operation. However, several seconds are required for the low-frequency clock oscillation to stabilize. Therefore, if switching to slow operation immediately after switching to normal 2 operation, wait until the low-frequency clock oscillation has stabilized or check the oscillation by program. Use the SMF status register (IP0E bit 1) for this check.

If the high-frequency clock (fc/27) is input to TG step 8, first set SLCK (OP16 bit 2) to 1 and input the low-frequency clock (fs). Then, monitor SMF by program. After confirming the SMF has switched from 1 to 0 to 1, or from 0 to 1 to 0, set DCLK to 1. The high-frequency clock oscillation then stops.

#### b. Returning to normal 2 operation from slow operation

When clearing DCLK1 to 0, simultaneously set the warming-up time in DWUT (bit 0 of OP16) to return to normal mode. After the set warming-up time has elapsed, normal 2 operation starts. The current operating mode can be confirmed by monitoring SLS (bit 0 of IP0E).

Figure 2-21. System Clock Switching Timing

Note: Slow mode automatically halts the high-frequency clock oscillation, enabling low-power dissipation and low-voltage operation. Power dissipation is reduced in the oscillator circuit and internal hardware; however, pin interface-related power dissipation (dependent on external circuits and the program) is not directly related to low-power dissipation operation. Therefore, consider power dissipation at the system and interface circuit design stage.

Although instruction execution is not cancelled by switching to slow operation, some peripheral hardware functions may be affected. See operational descriptions on this point.

## (2) Single-clock mode

This mode uses only the oscillator circuit for the high-frequency clock. R72 (XTIN) and R73 (XTOUT) are set to an I/O port. After reset is released, enters single-clock mode (normal 1 mode). The system clock control command register (OP16) is not required in single-clock mode. Hold mode provides low-power dissipation.

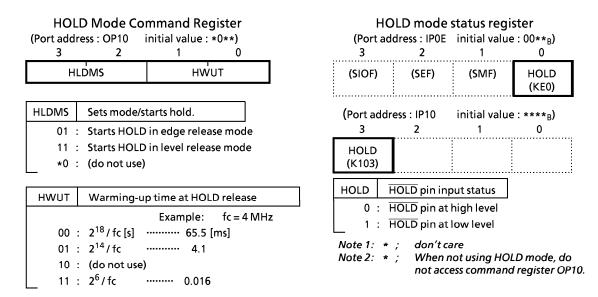

## 2.7.5 HOLD Operation

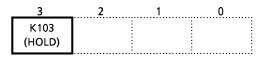

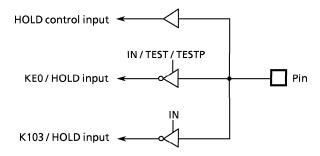

The HOLD function halts the operation of the system and preserves the internal status immediately prior to the halt. Processor power dissipation is low during a HOLD. The HOLD function is controlled through the command register (OP10) and the HOLD pin input. The input status of the HOLD pin can be monitored by the status register. In single-clock mode, bit 0 of IP0E can be used. In dual-clock mode, this bit is used for monitoring operating status (SLS) and is therefore not available. Instead, use bit 3 of IP10. This bit can be used in single-clock mode.

#### (1) Starting HOLD mode

Setting a command in the command register in single-clock mode starts HOLD mode. The states during a hold are as follows:

- 1. Oscillation is disabled and all internal operation halted.

- 2. The timing generator binary counter is cleared to 0.

- 3. Data memory, registers, and port latches maintain their states immediately prior to the hold.

- 4. The program counter stores the address of the instruction following the instruction used to trigger the hold ([OUT A, %OP10] or [OUT @HL, %OP10]).

Figure 2-22. HOLD Mode Command Register and Status Register

HOLD mode includes level release mode and edge release mode.

#### a. Level release mode

Setting the HOLD pin to high releases HOLD mode. This mode is used for capacitor backup or long-duration battery backup when an outage occurs in the main power supply.

The processor does not enter HOLD mode if the HOLD pin input is high when the instruction for starting HOLD mode is executed. Instead, the CPU immediately switches to the release sequence (warming up). Accordingly, when starting a HOLD in level release mode, the program should first check that the HOLD pin input is low (HOLD requested). There are the following two methods to check the HOLD pin input state:

- 1. Test HOLD (bit 0 of IP0E or bit 3 of IP10).

- 2. Input HOLD pin input to INT1 pin as well and generate an external interrupt 1 request.

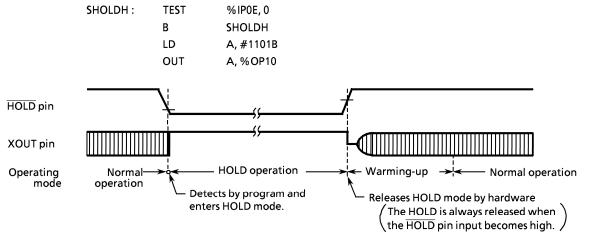

Example: Test HOLD, then start a HOLD in level release mode (warming-up time is 214 / fc [s]).

Figure 2-23 (a). Level Release Mode

## b. Edge release mode

This mode releases the HOLD at a rising edge of input to the HOLD pin. Edge release mode is used for repeating a relatively short programs at a fixed interval. Input a signal at a fixed interval (for example, a clock from a low power dissipation oscillator) to the HOLD pin.

In edge release mode, the processor enters HOLD mode even if the HOLD pin input is high.

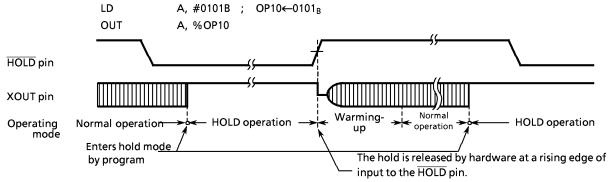

Example: Start HOLD in edge release mode (warming-up time set to 214/fc [s]).

Figure 2-23 (b). Edge Release Mode

Note: HOLD mode reduces power dissipation in the oscillator circuit and internal hardware. However, pin interface-related power dissipation (dependent on external circuits and the program) is not directly related to the hardware operation of the HOLD function. Therefore, consider power dissipation at the system and interface circuit design stage. Current is minimal when the input level of the CMOS circuit is stable at the power supply voltage level (V<sub>DD</sub>/V<sub>SS</sub>). However, current flows if the input level fluctuates beyond the power supply voltage level (about 0.3 to 0.5V). Therefore, when a pin signal is at high impedance because the output transistor at an input/output port (pins with open-drain outputs and input transistors) is disconnected, current may flow through the input transistor. Fix the input level using pull-up resistors.

#### (2) HOLD mode release

HOLD mode is released in the following sequence:

- 1. Oscillation begins.

- 2. Warms up for a sufficient time to stabilize the oscillation. During the warming-up time, internal operations remain halted. The program can select one of three warming-up times to suit the characteristics of the oscillator.

- 3. When the required warming-up time has elapsed, operation resumes from the instruction following the instruction that started HOLD mode.

- \* The warming-up time is obtained by dividing the frequency of the high-frequency clock using the timing generator. Therefore, if fluctuations occur in the oscillation at the release of HOLD mode, the warming-up time will vary from that shown in Figure 2-23 Treat the warming-up time as an approximate value only.

HOLD mode can also be released by setting the RESET pin to low. In this case a normal reset occurs immediately.

Note: Note the following when releasing a HOLD at low voltage.

Before releasing the hold, raise the power supply voltage to the operation. At this time, the RESET pin input becomes high together with the power supply voltage. If a time constant circuit, for example, is connected to the RESET pin, the rise in voltage at the RESET pin is slower than the rise in power supply voltage. If at this time, the RESET pin input voltage exceeds the non-inverted high level, an unintended reset may be automatically generated.

## 2.8. Interrupt Functions

## (1) Interrupt control circuit

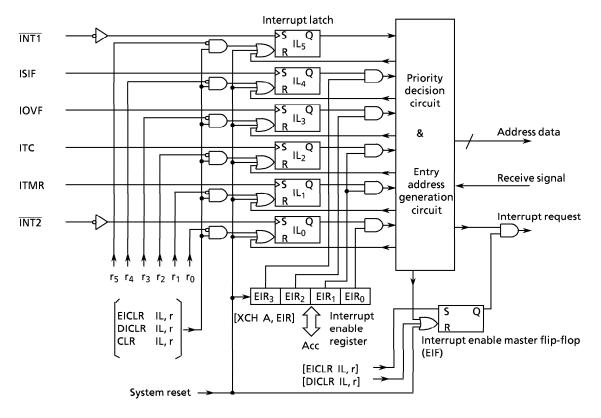

Six interrupt sources, two external and four internal, are supported. Prioritized multiple interrupts are also possible.

Interrupt latches ( $IL_5$  to  $IL_0$ ) are provided to store the requests that accompany the interrupts. The generation of an interrupt request sets the interrupt latch to 1. The interrupt latch requests the CPU to receive the interrupt. The program can selectively enable or disable interrupts using the interrupt enable master flip-flop (EIF) and the interrupt enable register (EIR). If multiple interrupt requests are generated simultaneously, the CPU receives the requests according to the priority defined in the hardware (the highest priority interrupt is received first).

|          | Interrupt source                     |        | Hardw<br>priori |   | Interrupt<br>latch | Interrupt<br>enable/disable<br>condition set by<br>program | Entry<br>Address  |

|----------|--------------------------------------|--------|-----------------|---|--------------------|------------------------------------------------------------|-------------------|

| External | External interrupt 1                 | (INT1) | (high)          | 1 | IL <sub>5</sub>    | EIF = 1                                                    | 0002 <sub>H</sub> |

|          | Serial interface interrupt           | (ISIF) |                 | 2 | IL <sub>4</sub>    | EIF = 1, EIR <sub>3</sub> = 1                              | 0004 <sub>H</sub> |

| Internal | Timer/counter overflow interrupt (10 |        |                 | 3 | IL <sub>3</sub>    | EIF = 1, EIR <sub>2</sub> = 1                              | 0006 <sub>H</sub> |

| Internal | Timer/counter interrupt              | (ITC)  |                 | 4 | IL <sub>2</sub>    | EIF = 1, EIR <sub>1</sub> = 1                              | 0008 <sub>H</sub> |

|          | Interval timer interrupt             | (ITMR) |                 | 5 | IL <sub>1</sub>    | EIF = 1, EIK1 = 1                                          | 000A <sub>H</sub> |

| External | External interrupt 2                 | (INT2) | (low)           | 6 | IL <sub>0</sub>    | EIF = 1, EIR <sub>0</sub> = 1                              | 000C <sub>H</sub> |

Table 2-2. Interrupt Sources

Figure 2-24. Interrupt Control Circuit Block Diagram

### a. Interrupt enable master flip-flop (EIF)

This flip-flop enables or disables all interrupts. Clearing the flip-flop to 0 disables reception of all interrupts. Setting the flip-flop to 1 enables reception of all interrupts.

When an interrupt is received, the flip-flop is cleared to 0, temporarily disabling reception of subsequent interrupts. After the interrupt service program is executed, the flip-flop is reset to 1 by the execution of the interrupt return instruction, again enabling interrupts.

Use the [EICLR IL, r] or [DICLR IL, r] instruction to set or clear the EIT. At reset, the flip-flop is initialized to 0.

#### b. Interrupt enable register (EIR)

The EIR is a 4-bit register that enables or disables reception of the ISIF, IOVF, ITC, ITMR, and INT2 interrupts. If the applicable bit of this register is 1, the interrupt is enabled. If the applicable bit is 0, the interrupt is disabled. The ITC and ITMR interrupt sources share bit 1 of the EIR (EIR<sub>1</sub>). Use the [XCH A,EIR] instruction to read or write the EIR. At reset, the EIR is initialized to 0.

#### c. Interrupt latch (IL)

An interrupt latch is provided for each interrupt. The IL is set to 1 by the generation of an interrupt request, whereupon the IL requests that the CPU receive the interrupt. Immediately the interrupt is accepted, the latch is cleared to 0. At reset, all interrupt latches are initialized to 0.

The interrupt latches can be individually cleared by the interrupt latch instructions [EICLR IL, r], [DICLR IL, r], and [CLR IL, r]. Interrupt requests can be cancelled or initialized within the program. When the value of the instruction field, r, is 0, the interrupt latch is cleared. When the value is 1, the interrupt latch value is maintained. The interrupt latch cannot be set by an instruction.

Example 1: IOVF, INT1, INT2 interrupts. Example 2: Clear interrupt latches other than ISIF and set EIF to 1.

LD A, #0101B EICLR IL, 010000B

XCH A, EIR

EICLR IL, 111111B

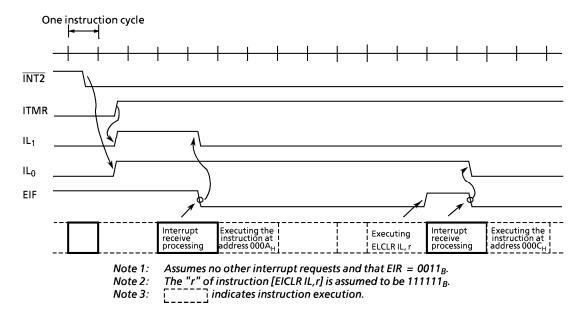

#### (2) Interrupt processing

Interrupt requests are saved until the interrupt is received, or until the interrupt latch is cleared by a reset or an interrupt latch manipulation instruction. Interrupt receive processing is executed in two instruction cycles after the instruction currently under execution is completed. The interrupt processing program terminates on execution of the interrupt return instruction [RETI].

The processor performs the following operations to receive an interrupt:

- 1. Saves the contents of the program counter and flags to the stack.

- 2. Sets the interrupt entry address for the interrupt in the program counter.

- 3. Sets the status flag to 1.

- 4. Clears the interrupt enable master flip-flop (EIF) to 0 to temporarily disable further interrupts.

- 5. Clears the interrupt latch for the received interrupt to 0.

- 6. Branches to the instruction stored at the interrupt entry address. (The program memory at the interrupt entry address usually contains a branch instruction to the service program for the interrupt. As the interrupt entry addresses are allocated every 2 bytes, the addresses typically cannot contain a long branch instruction. Accordingly, the interrupt service program is allocated to program memory addresses 0000 0FFF<sub>H</sub>.)

To handle multiple interrupts, set the EIF to 1 in the interrupt service program. The EIR determines which interrupts can be received at this time. However, as the INT1 interrupt cannot be disabled by the EIR, disable processing of INT1 by software.

Example: Disable the interrupt processing for INT1 by software (use bit 0 of RAM [05H], the interrupt

processing disable switch).

If RAM  $[05H]_0 = 1$ , processing returns without

processing the interrupt.

PINT1: TEST 05H, 0

SINT1

RETI

SINT1:

The interrupt return instruction performs the following operations:

1. Restores the contents of the program counter and flags from the stack.

2. Sets the interrupt enable master flip-flop (EIF) to 1 to re-enable interrupts. This means that the next interrupt can be received immediately after execution of the interrupt return instruction.

Note: If the interrupt processing time is longer than the interval between interrupt requests, only the interrupt service program is executed (the main program is not executed).

In interrupt processing, the program counter and flags are automatically saved or restored. However, the accumulator and other registers (for example, the HL register pair, DMB, and DC) are not automatically saved or restored. If the accumulator and other registers are used in the interrupt handler, their contents should be saved on entry and restored on exit. When multiple interrupts are generated, be careful that the save areas in RAM do not overlap.

```

Example 1: Save and restore the accumulator and HL register pair.

```

XCH HL, GSAV1 ; RAM [GSAV1] ↔ HL

XCH A, GSAV1 + 2 ; RAM [GSAV1 + 2]  $\leftrightarrow$  Acc

Note: The lower two bits of GSAV1 must be set to 0.

Example 2: Save the DMB to bit 0 at address GSAV3 in data memory (page zero).

CLR GSAV3, 0 ; RAM [GSAV3]  $_0 \leftarrow 0$ TEST DMB ; If DMB = 0, skips.

TEST DMB ; If DMB = 0, skips.

B SKIPS

SET GSAV3, 0 ; RAM [GSAV3]  $_0 \leftarrow 1$

SKIPS:

Example 3: Restore the DMB from bit 0 at address GSAV3 in data memory (page zero).

CLR DMB ; DMB  $\leftarrow$  0

TEST GSAV3, 0 ;  $fRAM [GSAV3]_0 = 0$ , skips.

B SKIPR

SET DMB ; DMB ← 1

SKIPR:

Figure 2-25. Interrupt Timing Chart (Example)

#### (3) External interrupt

The interrupt latches for external interrupts INT1 and INT2 are set at falling edges of the corresponding pin inputs (INT1 and INT2).

As the INT1 interrupt cannot be disabled by the EIR, this interrupt is always received as long as interrupts are enabled (EIF = 1). Consequently, use this interrupt for high priority interrupts, for example, emergency interrupts. Interrupt INT1 is generated at the falling edge of R82 (INT1) pin input. Thus, when using the pin as an I/O port, write an interrupt return instruction [RETI] at the interrupt entry address to perform dummy interrupt processing.

Interrupt INT2 can be enabled or disabled by the EIR. When using the R80 (INT2) pin as an I/O port, interrupt INT2 is generated at the falling edge of the pin input. However, simply clearing EIR bit 0 to 0 disables interrupt INT2.

The external interrupt inputs are hysteresis inputs. Both high and low levels must be maintained for at least two instruction cycles for the interrupt to be detected correctly.

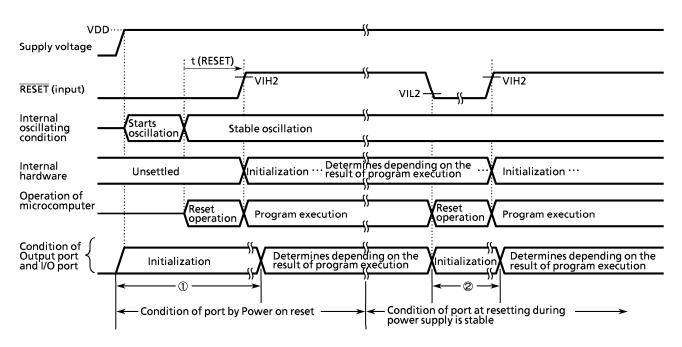

#### 2.9 **Reset Function**

If the RESET pin is maintained at a low level for a minimum of three instruction cycles with stable oscillation and the power supply voltage within the operating voltage range, a reset occurs and the internal state is initialized.

The reset is released when the RESET pin returns to high level. This restarts execution from address 0000H.

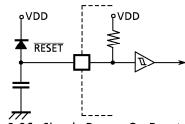

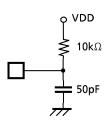

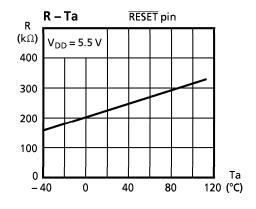

The RESET pin is a hysteresis input with a pull-up resistor (typ. 220k $\Omega$ ). Connecting a capacitor and a diode externally Figure 2-26. Simple Power-On Reset provides a simple power-on reset.

| Internal hardware                 |       | Initial value     | Internal hardware             | Initial value    |

|-----------------------------------|-------|-------------------|-------------------------------|------------------|

| Program counter                   | (PC)  | 0000 <sub>H</sub> | TG binary counter             | "0"              |

| Status flag                       | (SF)  | 1                 | Output latch                  | See the I/O      |

| Data memory bank selector         | (DMB) | 0                 | (Input/output or output port) | circuit section. |

| Interrupt enable master flip-flop | (EIF) | 0                 |                               | See the          |

| Interrupt enable register         | (EIR) | 0 <sub>H</sub>    | Command registers             | description of   |

| Interrupt latch                   | (IL)  | "0"               |                               | each command     |

Table 2-3. Internal Hardware Initialization by Reset

## 2.9.1 Warm Start

Warm start - reset while saving contents of data memory after HOLD is released - is not supported by hardware. However, warm start can be performed in the following way.

- 1. Backs up the voltage supplied to the VDD pin.

- 2. Also applies to the HOLD pin a waveform in sync with the change in power supply voltage.

- 3. Detects a power drop and sets to HOLD mode during power cut.

- 4. After release from HOLD, resets by program using sink open-drain (initial: Hi-Z) output port.

- 5. Applies the POWER ON detect signal to the input port and skips the RAM initialize routine.

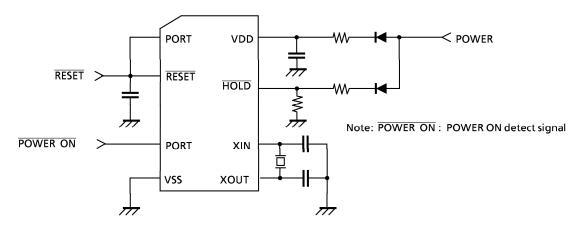

Figure 2-27 is an example of a warm start circuit.

Figure 2-27. Warm Start Circuit Example

## 3. Peripheral Hardware Functions

#### 3.1 Ports

The 13 input/output instructions transfer data with external circuits. The instructions also transfer commands, read states, and data with internal circuits.

The four types of ports are: 1. Input/output ports ; Transfer data with external circuits.

2. Command registers ; Control internal circuits.

3. Status registers ; Read status signals from internal circuits.

4. Data registers ; Transfer data with internal circuits.

Ports are assigned a port address (00 -  $1F_H$ ). Individual ports are selected by specifying the port address in the input/output instruction. Table 3-1 shows the port address allocation and the input/output instructions that access the ports.

## 3.1.1 Input/Output Timing

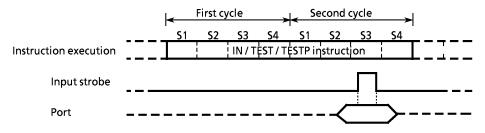

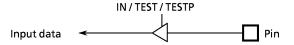

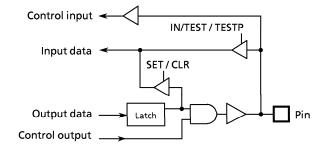

## (1) Input timing

The processor reads external data from input ports or input/output ports at the S3 state of the second cycle of the input instruction (a 2-cycle instruction). As this timing cannot be identified externally, the program must deal with transient input data such as chatter.

Figure 3-1. Input Timing

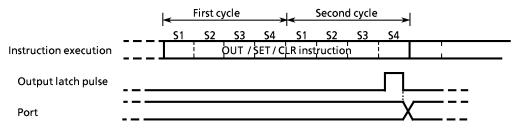

#### (2) Output timing

The processor outputs data to output ports or input/output ports at the S4 state of the second cycle of the output instruction (a 2-cycle instruction).

Figure 3-2. Output Timing

| TaCa            | TACA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RT                                     |                        |                         | INPUT/O    | INPUT/OUTPUT INSTRUCTION | CTION                  |                           |                            |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------|-------------------------|------------|--------------------------|------------------------|---------------------------|----------------------------|

| ADDRESS<br>(**) | INPUT (IP**)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OUTPUT (OP**)                          | IN %p, A<br>IN %p, @HL | OUT A, %p<br>OUT @HL,%p | OUT #k, %p | OUTB @HL                 | SET %p, b<br>CLR %p, b | TEST %p, b<br>TESTP %p, b | SET @L<br>CLR @L<br>TEST@L |

| 00<br>H 0 0     | K0 input port<br>E2PROM read data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | E2PROM command<br>E2PROM write data    | 000                    | 000                     | 000        | . 1 1                    | ł t                    | 000                       | 1 I                        |

| 03              | E∠PROM read data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | E-PROIN write data                     | ) ı                    | )                       | ) ı        | 1 1                      | 1 1                    | ) <b>'</b>                | 1 1                        |

| 04              | R4 input port (analog input)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R4 output port                         | 0                      | 0                       | 0          | ı                        | 0                      | 0                         | 0                          |

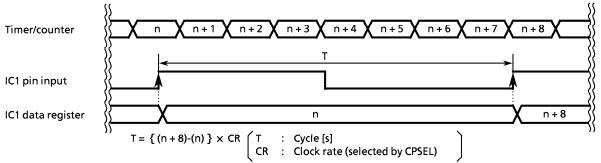

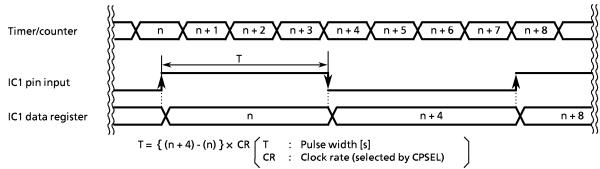

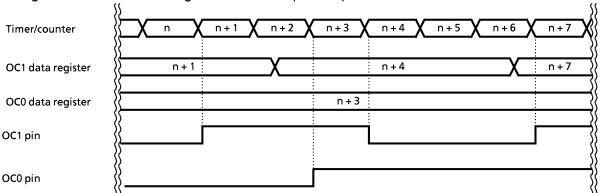

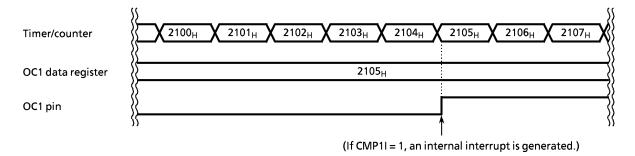

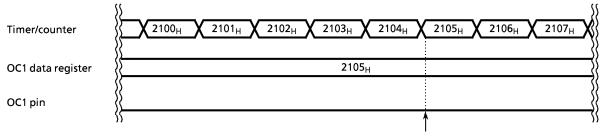

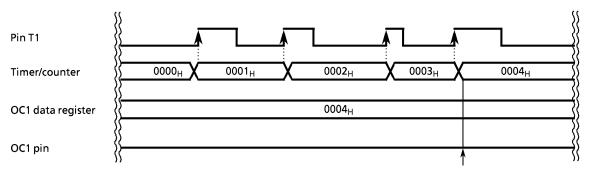

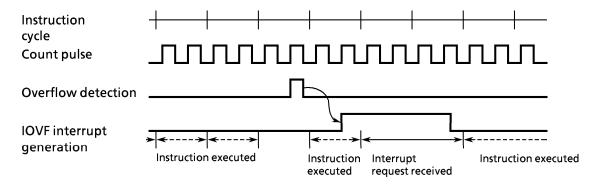

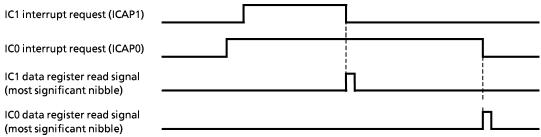

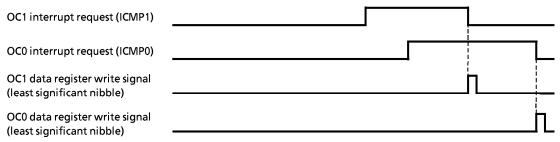

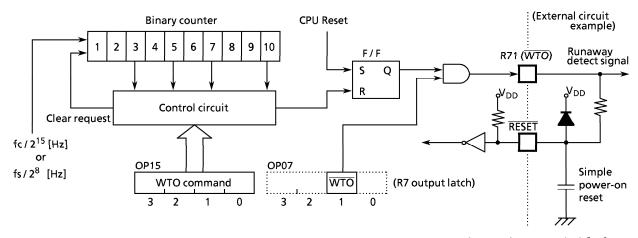

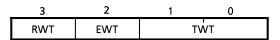

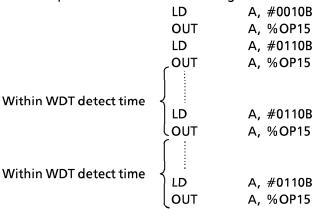

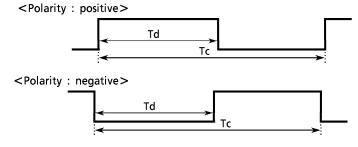

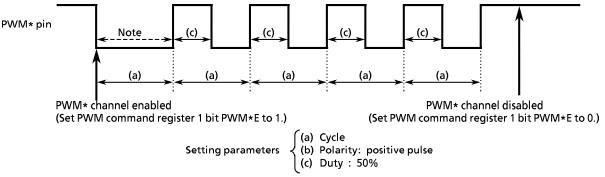

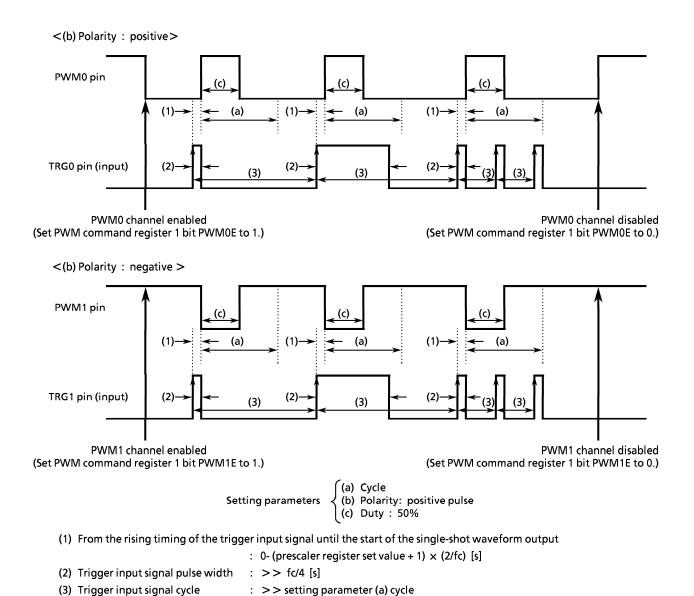

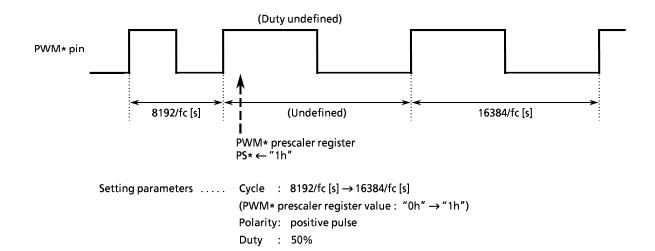

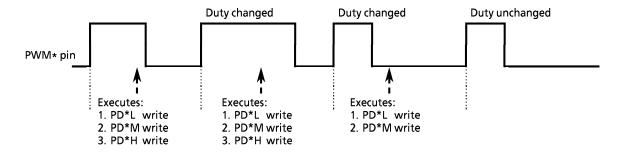

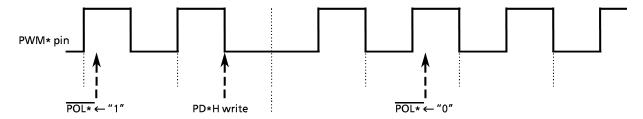

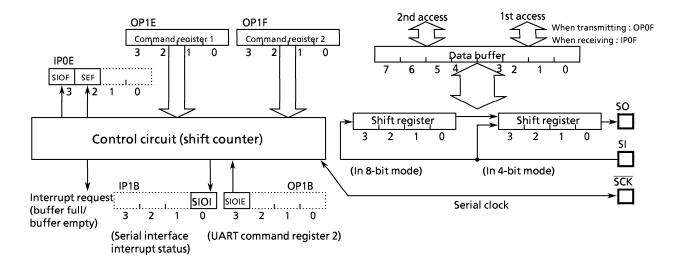

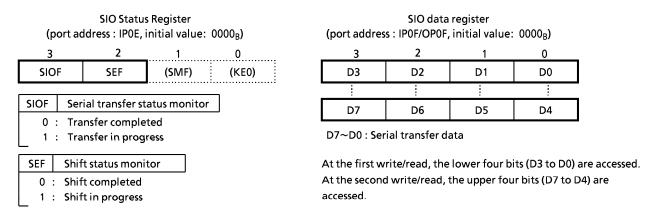

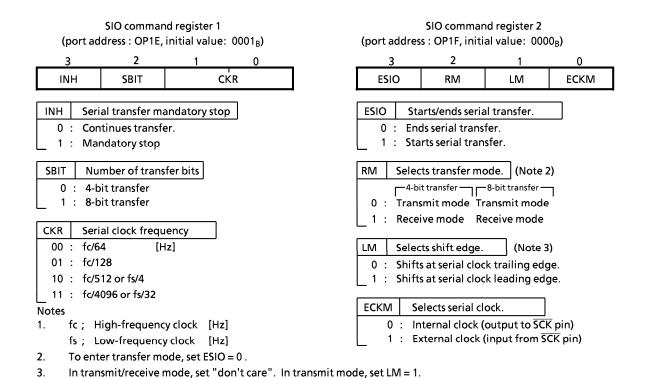

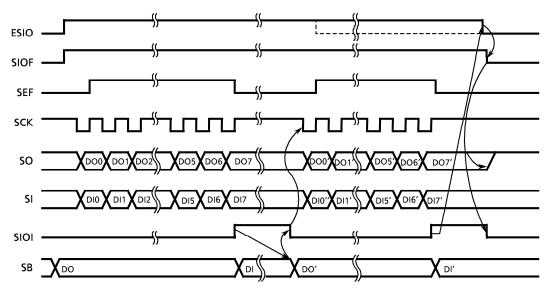

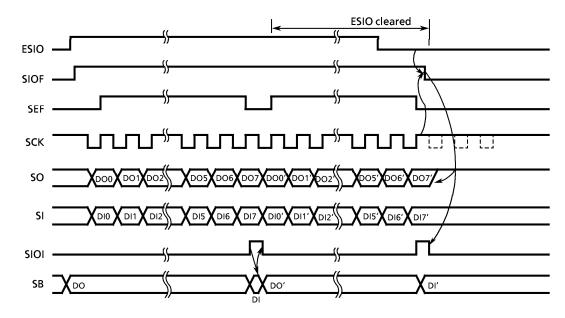

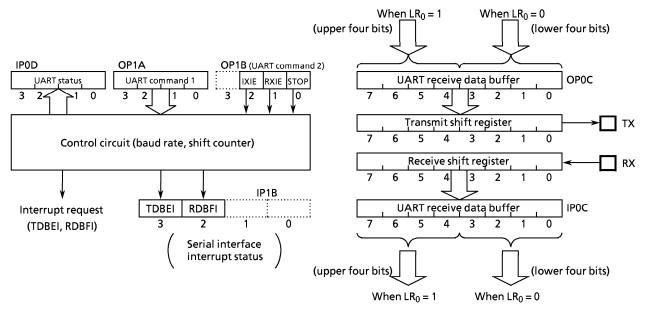

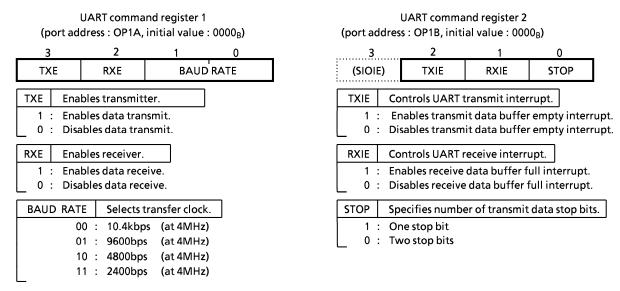

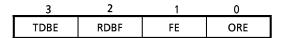

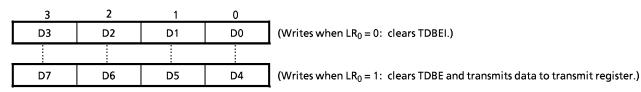

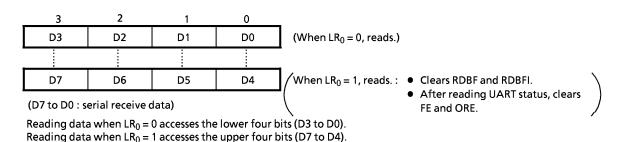

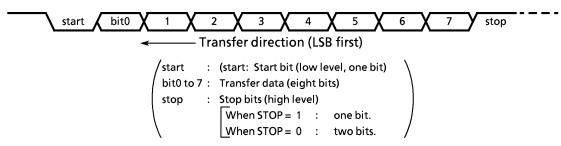

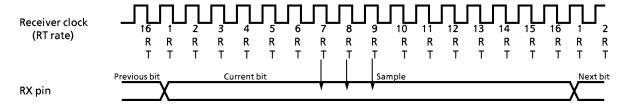

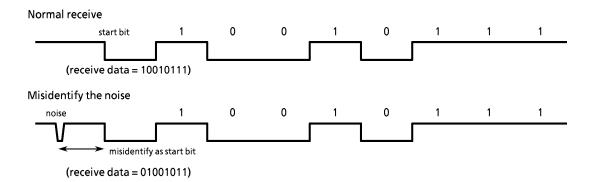

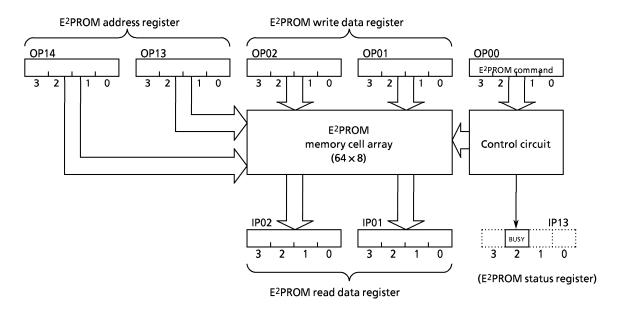

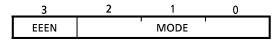

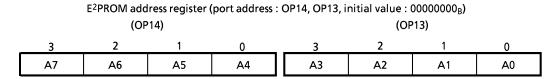

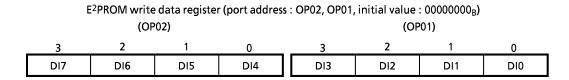

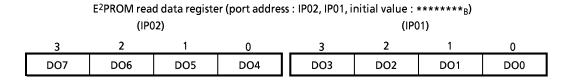

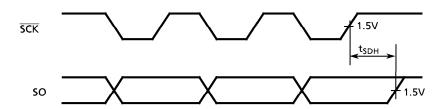

| 02              | R5 input port (analog input)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R5 output port                         | 00                     | 00                      | 00         | 1 1                      | o c                    | ) C                       | 00                         |