T-46-23-37

DS1234

Conditional Nonvolatile Controller Chip

### **FEATURES**

- Converts CMOS static RAMs into nonvolatile memories

- Software controlled write inhibit

- Software controlled battery disconnect extends battery life

- $\bullet$  Unconditionally write protects when  $\mathbf{V}_{\mathbf{cc}}$  is out of tolerance

- Consumes less than 100 nA of battery current

- Power fail signal can be used to interrupt processor on power failure

- $\bullet$  Low forward voltage drop on the  $V_{cc}$  switch

- Optional 16-pin SOIC surface mount package

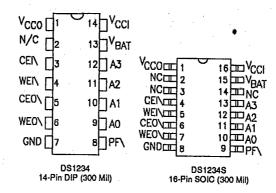

### PIN DESCRIPTION

# PIN NAMES (\ Denotes Condition Low)

|      | Pin Name         | Description         |

|------|------------------|---------------------|

| .1   | V <sub>cco</sub> | RAM Supply          |

| 2    | N/C              | No Connection       |

| 3    | CEI/             | Chip Enable Input   |

| 4    | WEI\             | Write Enable Input  |

| 5    | CE0/             | Chip Enable to RAM  |

| 6    | WE0\             | Write Enable to RAM |

| 7    | GND              | Ground              |

| 8    | PF\              | Power Fail Output   |

| 9-12 | A0-A3            | Address Inputs      |

| 13   | V <sub>BAT</sub> | Battery Input       |

| 14   | Voci             | +5V Supply          |

## **DESCRIPTION**

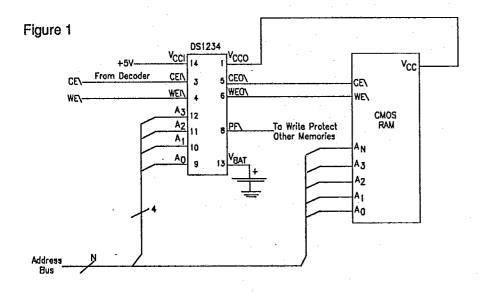

The DS1234 is a CMOS circuit that converts CMOS RAM into nonvolatile memory and adds two software selectable switches. Incoming power is monitored for an out-of-tolerance condition. When such a conditions is detected, chip enable and write enable to the RAM are inhibited to accomplish write protection, and the battery is switched on to supply the memory with uninterrupted power. The two software selectable switches provided by the DS1234 are capable of

inhibiting both the write enable to the RAM and the battery backup circuitry by a pattern recognition sequence across four address lines. Inhibiting the write enable to the nonvolatile RAM provides data integrity by isolating the memory contents from external change. The second switch provides added flexibility and increases battery life to the system by enabling/disabling the battery for shipment or storage, or when battery backup is not needed.

39E D

16-23-37

### **OPERATION**

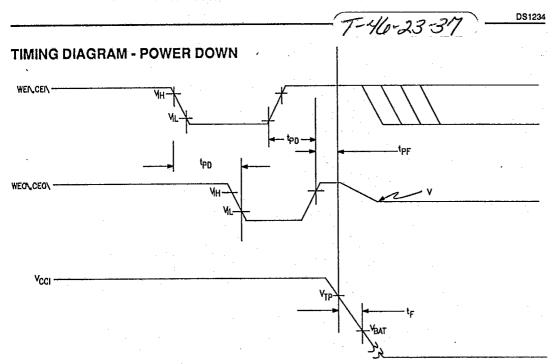

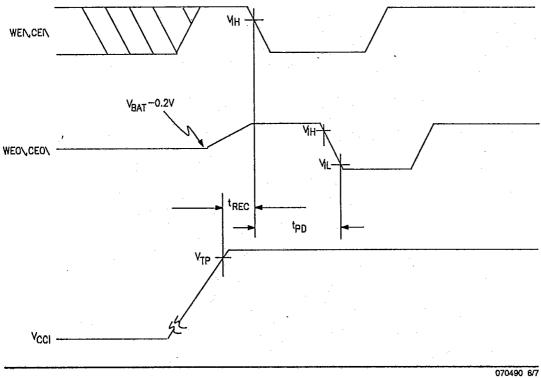

The DS1234 Conditional Nonvolatile Controller performs three circuit functions required to battery backup a RAM. First, a switch is provided to direct power from the battery or the incoming supply (V<sub>cci</sub>), depending on which is greater. This switch has a voltage drop of less than 0.2V. The second function is power fail detection. The DS1234 constantly monitors the incoming supply. When the supply goes out-of-tolerance, a comparator detects power fall and inhibits chip enable and write enable. The threshold voltage,  $V_{TP}$ , at which power fail is detected is defined as 1.26 times  $V_{\rm BAT}$ . The third function of write protection is accomplished by holding the CEO\ and WEO\ output signals to within 0.2 volts of the V<sub>cci</sub> or battery supply.

In addition to the nonvolatile controller functions, the DS1234 supplies two software selectable switches for master control of the write enable and the nonvolatile controller itself. switches are controlled by a 16-cycle pattern recognition sequence across four address lines (see Tables 1 and 2). Prior to entering the pattern recognition sequence that will define the two switch settings, a read cycle of 1111 on address inputs A0 through A3 should be executed to initialize the compare pointer of clock zero. Each four-bit compare word is clocked into the DS1234 on the negative edge of CEN. A0. A1 and A2 must match the compare pattern on all 16 consecutive cycles while A3 must match only the first eleven; the last five are used to define the switch settings. The eleventh address cycle, starting at zero, defines the switch that inhibits the write enable to the RAM (WEO\). A logic one in this location allows read/write operations so that WEO\ will follow WEI\ and data can be updated. A zero on cycle eleven turns the RAM into a read-only memory (ROM). The next four address cycles, 12 thorough 15, define whether the nonvolatile controller operation is enabled or disabled. A bit pattern of 1010 activates the nonvolatile controller; data in the RAM is maintained on power loss. Any pattern other than 1010 will disable the nonvolatile controller operation.

At the completion of the 16th cycle, if the pattern recognition sequence is correct, the switch settings defined in cycles 11 though 15 are transferred and are active for the next memory cycle. When external battery power is applied for the first time, the DS1234 will come up with the nonvolatile controller off. Upon initial V<sub>cc</sub> power, the write enable will be set in read/write operation (WEI\=WEO\).

# **ADDRESS INPUT PATTERN Table 1**

T-46-23-37

| CYCLE NUMBER   |   |   |   |   |   |   |   |   |    |   |    |    |    |    |    |    |

|----------------|---|---|---|---|---|---|---|---|----|---|----|----|----|----|----|----|

| Address Inputs | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8. | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| А3             | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0  | 1 | 0  | •  | •  | •  | •  | •  |

| A2             | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 1  | 0 | 1  | 0  | 0  | 0  | 1  | 1  |

| A1             | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0  | 1 | 0  | 1  | 1. | 1  | 0  | 0  |

| A0             | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 1  | 0 | 1  | 0  | 0  | 0  | 1  | 1  |

<sup>\*</sup> See Table 2

# **CONTROL SELECT** Table 2

| WEI | \ Batte | ry Cor | ntrol |    | Operation                       |

|-----|---------|--------|-------|----|---------------------------------|

| 11  | 12      | 13     | 14    | 15 |                                 |

| 0   | х       | X      | X     | Х  | Read Only Operation             |

| 1   | Х       | х      | Х     | Х  | Read/Write Operation            |

| Х   | 1       | 0      | 1     | 0  | Enables Nonvolatile Controller* |

X = Don't Care

<sup>\*</sup>Any other combination turns controller off

**ABSOLUTE MAXIMUM RATINGS\***

Voltage on any Pin Relative to Ground

**Operating Temperature**

Soldering Temperature

Storage Temperature

-0.3V to +7.0V 0°C to 70°C -55°C to +125°C

260°C for 10 seconds

\* This is a stress rating only and functional operation of the device at these or any other conditions outside those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

# RECOMMENDED DC OPERATING CONDITIONS

(0°C to 70°C)

| PARAMETER            | SYMBOL           | MIN  | TYP | MAX                  | UNITS | NOTES |

|----------------------|------------------|------|-----|----------------------|-------|-------|

| Power Supply Voltage | V <sub>cci</sub> | 4.5  | 5.0 | 5.5                  | ٧     | 1     |

| Input High Voltage   | V <sub>IH</sub>  | 2.2  |     | V <sub>cc</sub> +0.3 | V     | 1     |

| Input Low Voltage    | V <sub>II</sub>  | -0.3 |     | +0.8                 | V     | 1     |

| Battery Voltage      | V <sub>BAT</sub> | 2.5  |     | 3.7                  | ٧     |       |

### DC ELECTRICAL CHARACTERISTICS

$(0^{\circ}\text{C to }70^{\circ}\text{C}; V_{cc}=5\text{V +/- }10\%)$

| PARAMETER                 | SYMBOL           | MIN  | TYP | MAX  | UNITS | NOTES |

|---------------------------|------------------|------|-----|------|-------|-------|

| Supply Current            | I <sub>cci</sub> |      |     | 5    | mA    | 2     |

| Supply Current @          | Icco             |      |     | 80   | mA    | 3     |

| $V_{cco} = V_{cci} - 0.2$ |                  |      |     |      | /     |       |

| Input Leakage             | I <sub>IL</sub>  | -1.0 |     | +1.0 | uA    |       |

| Output Leakage            | I <sub>LO</sub>  | -1.0 |     | +1.0 | uA    |       |

| Output Current @ 2.4V     | I <sub>OH</sub>  | -1.0 |     |      | mA    | 4     |

| Output Current @ 0.4V     | loL              | 4.0  |     |      | mA    | 4     |

(0°C to 70°C,  $V_{CCI} < V_{BAT}$ )

| CE0 WE0\ Output             | V <sub>OHE</sub> | V <sub>BAT</sub> -0.2 |     | ٧  | 6 |

|-----------------------------|------------------|-----------------------|-----|----|---|

| Battery Current             | I <sub>BAT</sub> |                       | 0.1 | uA | 7 |

| Battery Backup Current      | Iccoi            |                       | 100 | uA | 5 |

| $@V_{CCO} = V_{BAT} - 0.3V$ |                  |                       |     |    |   |

### CAPACITANCE

(t.=25°C)

| Q711 71Q117111Q    |                 |     |     |     |       | V.A   |

|--------------------|-----------------|-----|-----|-----|-------|-------|

| PARAMETER          | SYMBOL          | MIN | TYP | MAX | UNITS | NOTES |

| Input Capacitance  | C <sub>IN</sub> |     |     | 5   | ρF    |       |

| Output Capacitance | Cour            |     |     | 7   | pF    |       |

|         |          | -          |      |

|---------|----------|------------|------|

| (0°C to | 70°C, V. | = 5V + / - | 10%) |

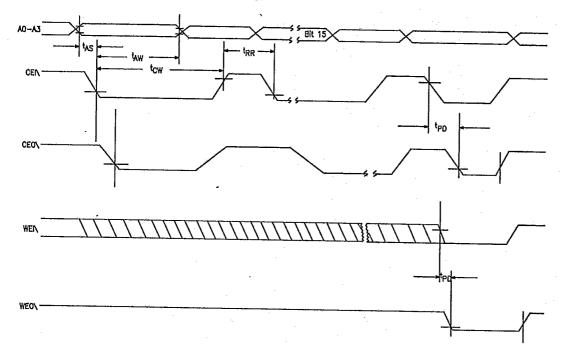

| AC ELECTRICAL CH  | ARACTERIST      | IC  | $(0^{\circ}\text{C to }70^{\circ}\text{C}, \text{ V}_{co} = 5\text{V} + / -10^{\circ}\text{C})$ |                                                  |       |               |  |  |

|-------------------|-----------------|-----|-------------------------------------------------------------------------------------------------|--------------------------------------------------|-------|---------------|--|--|

| PARAMETER         | SYMBOL          | MIN | TYP                                                                                             | MAX                                              | UNITS | NOTES         |  |  |

| Address Setup     | t <sub>AS</sub> | 0   |                                                                                                 | -                                                | ns    | 110.00        |  |  |

| Address Hold      | t <sub>AH</sub> | 50  |                                                                                                 | <del>-  </del>                                   | ns    | <del> </del>  |  |  |

| Read Recovery     | t <sub>BB</sub> | 40  | <del> </del>                                                                                    | <del>                                     </del> | ns    |               |  |  |

| CEI\ Pulse Width  | t <sub>cw</sub> | 110 |                                                                                                 |                                                  | ns    |               |  |  |

| Propagation Delay | t <sub>PD</sub> |     |                                                                                                 | 20                                               | ns    | <del></del> - |  |  |

| $(0^{\circ}\text{C to } 70^{\circ}\text{C}, V_{col} < V_{TB})$ | (0°C | to | 70°C, | V. | < 1 | ٧., | ٠, |

|----------------------------------------------------------------|------|----|-------|----|-----|-----|----|

|----------------------------------------------------------------|------|----|-------|----|-----|-----|----|

|                    |                                  | (0                                  | 0 10 70 0,                          | v <sub>cci</sub> < v <sub>TP</sub> )    |

|--------------------|----------------------------------|-------------------------------------|-------------------------------------|-----------------------------------------|

| t <sub>rec</sub> . | ļ                                | 2                                   | ms                                  |                                         |

| t <sub>F</sub>     | 0                                |                                     | us                                  |                                         |

| t <sub>R</sub>     | 0                                |                                     | us                                  |                                         |

| t <sub>PF</sub>    | 0                                |                                     | ns                                  |                                         |

|                    | t <sub>F</sub><br>t <sub>R</sub> | t <sub>F</sub> 0 0 t <sub>R</sub> 0 | t <sub>REC</sub> 2 t <sub>F</sub> 0 | t <sub>F</sub> 0 us t <sub>R</sub> 0 us |

# **TIMING DIAGRAM - SWITCH SETTING**

# TIMING DIAGRAM - POWER UP

640

### NOTES:

1. All voltages are referenced to ground.

2. Measured with  $V_{cco}$  CE0\ and WE0\ open. 3.  $I_{cco}$  is the maximum average load which the DS1234 can supply to the memories.

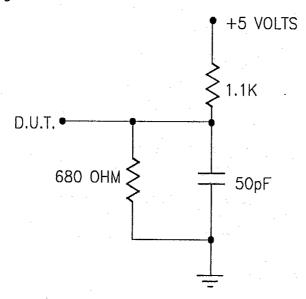

4. Measured with a load as shown in Figure 2.

- 5. I<sub>cco1</sub> is the maximum average load current which the DS1234 can supply to the memories In the battery backup mode.

- 6. Chip Enable, CEO\, and Write Enable, WEO\, outputs can only sustain leakage current in the battery backup mode.

- 7.  $I_{\rm BAT}$  is the total load current which the DS1234 uses from the battery input pin with  $V_{\rm cco.}$  CE0\, and WEO\ open.

## **OUTPUT LOAD Figure 2**