#### Features

- High speed: 125-MHz state machine output generation

- Token passing

- Multiple, concurrent processes

- Multiway branch or join

- One clock with programmable clock doubler

- Programmable miser bits for power savings

- 8 to 12 inputs with input macrocells

Metastability hardened: 10-year

- 0, 1, or 2 input registers

- -3 programmable clock enables

- 32 synchronous state macrocells

- 10 to 14 outputs

- Skew-controlled OR output array

- Outputs are sum of states like PLA

- · Security fuse

- Available in 28-pin slimline DIP and 28-pin HLCC

- UV-erasable and reprogrammable

- Programming and operation 100% testable

#### **Product Characteristics**

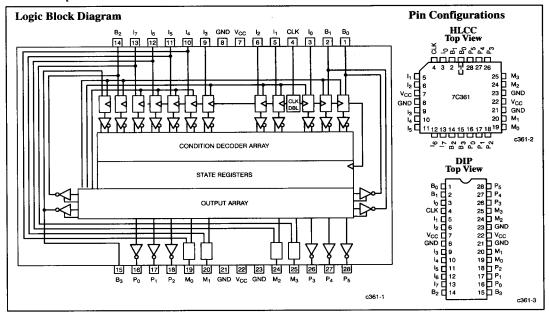

The CY7C361 is a CMOS erasable, programmable logic device (EPLD) with very high speed sequencing capabilities.

Applications include high-speed cache and I/O subsystems control, control of high-speed numeric processors, and high-speed arbitration between synchronous or asynchronous systems.

# Ultra High Speed State Machine EPLD

A programmable on-board clock doubler allows the device to operate at 125 MHz internally based on a 62.5-MHz input clock reference. The clock doubler is not a phase-locked loop. It produces an internal pulse on each edge of the external clock. The length of each internal pulse is determined by the intrinsic delays within the CY7C361. When the doubler is enabled, all macrocells in the CY7C361 are referenced to the doubled clock. If the clock doubler is disabled, a 125-MHz input clock can be connected to pin 4, and it will be used as a clock to all macrocells.

The CY7C361 has two arrays, similar to those in a PLA except that the registers are placed between the two arrays so that the long feedback path of the PLA is eliminated.

#### **Selection Guide**

|                     | I <sub>CC</sub> mA at f <sub>MAX</sub> |     | f <sub>MAX</sub> MHz |       | t <sub>IS</sub> ns |     | t <sub>CO</sub> ns |     |

|---------------------|----------------------------------------|-----|----------------------|-------|--------------------|-----|--------------------|-----|

| Generic Part Number | Com                                    | Mil | Com                  | Mil   | Com                | Mil | Com                | Mil |

| CY7C361-125         | 200                                    |     | 125.0                |       | 2                  |     | 15                 |     |

| CY7C361-100         | 200                                    | 200 | 100.0                | 100.0 | 3                  | 3   | 19                 | 19  |

| CY7C361-83          |                                        |     | 83.3                 | 83.3  | 5                  | 5   | 23                 | 23  |

## Product Characteristics (continued)

In the CY7C361, the state information is contained in 32 state macrocells sandwiched between the input and output arrays. The current state information is fed back fast enough to achieve the 125-MHz operating frequency. These state macrocells also have serial connections that allow state machines to be built using a token-passing methodology similar to one hot encoding, but with the ability to support multiple active states at any given time.

The output array performs an OR function over the state macrocell outputs, allowing the control signals of the state machine to be produced directly. The signals from the output array are connected to the 14 device outputs (4 of which are bidirectional). In addition there are 3 sum terms that act as clock enables to the 3 groups of input macrocells. There are also 4 sum term output enables for the 4 bidirectional pins.

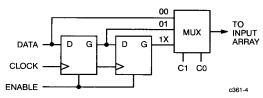

#### Input Macrocells

The CY7C361 has 12 input macrocells, shown in Figure 1. Each macrocell can be configured to have 0, 1, or 2 registers in the path of the input data. In the configuration where there is no input register, the set-up time required is the longest, because it includes the propagation delay through the input array plus the state register set-up time. In the single-registered configuration the set-up time is less than half of the unregistered case. The double-registered configuration is used to synchronize asynchronous inputs without causing metastable events.

Figure 1. Input Macrocell

## Input Register Enables

The input macrocells are divided into 3 groups of 4 macrocells each. Each of these groups has a register clock enable coming from the output array. The assignment of enable signal node numbers to input macrocells is as follows:

| Input Nodes    | Enable Node |

|----------------|-------------|

| 3, 5, 6, 9     | 29          |

| 10, 11, 12, 13 | 30          |

| 1, 2, 14, 15   | 31          |

When the enable node is true, data is clocked into the registers of the input macrocells on the rising edge of the internal global clock.

#### Metastability Immunity

A high level of metastable immunity is afforded in the double-registered configuration. The CY7C361 registers are done in fast CMOS and they resolve inputs in a minimal amount of time. With all inputs switching at maximum frequency, one metastable event capable of violating the set-up time of a subsequent register occurs every 10 years. The probability of failure in a configured state machine is much lower than this calculation suggests, because there are more registers in the device and thus more decision time is allowed. No state machine failures due to metastable phenomena will be observed if the maximum frequency and double-registered operation frequency are used. This makes the CY7C361 ideally suited for constructing state machines requiring arbitration. For

more information on metastability, refer to the "Are Your PLDs Metastable?" application note in the *Cypress Applications Handbook*.

#### Input Array

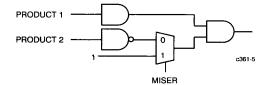

The input array is based on the condition decoder, shown in Figure 2. In a conventional PLA or PLD device, only PRODUCT1 would be present in the first array and the output and the feedback would be encoded by a second programmable or fixed or array. The speed of state machines is limited mainly by the feedback path.

Figure 2. Condition Decoder

The condition decoder of the CY7C361 forms a product of a product and a sum over the input field. (The sum term is obtained by inverting the inputs to PRODUCT2.) Since there is immediate feedback information in the input field, multiway fork and join operations can be performed using this type of condition decoder. In other words, the condition decoder is used to control or gate the token being passed from macrocell to macrocell. In contrast, a traditional PLD or PLA requires more logic because the array is used to encode the states. In the CY7C361, state transitions can be made in half the time because there is no "state encoding" delay.

Each condition decoder has a miser bit in its sum term path. If the term is not used, the miser bit is automatically programmed. The miser bit completely disconnects the product term and replaces it with a logic HIGH. This results in a power savings.

The input array has 41 condition decoders: one global reset decoder, 8 local reset decoders, and 32 macrocell decoders. The array has 44 true/complement input pairs, 88 inputs total.

For speed reasons, the feedback signals are segmented. This means that for each group of 8 macrocells, 2 have global feedback, 2 have intermediate feedback to 16 of the 32 macrocells, and 4 have local feedback within their group of 8 macrocells only. Segmenting the feedback reduces the number of inputs per decoder to 56. Because the CY7C361 utilizes token passing, a large state machine will be effectively broken down into several smaller machines using 4 or less macrocells. The global and intermediate feedback is used to communicate between these smaller machines, and the local feedback is used within the smaller machines. For more information on the hot state encoding or token-passing design methodology, refer to the application notes titled "State Machine Design Considerations and Methodologies" and "Understanding the CY7C361" in the Cypress Applications Handbook.

#### State Machine Macrocells

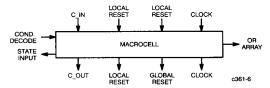

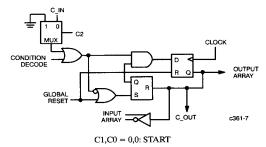

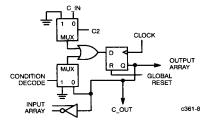

The CY7C361 has 32 state macrocells. The state macrocells each have a single condition decode and share a common clock and global reset condition. The global reset is synchronous, and it lasts for two internal clock cycles. For each group of four state macrocells, there is a synchronous local reset condition.

All 32 of the macrocells are "daisy-chained." Each has a C\_IN input that is connected to the C\_OUT output of the previous macro-

cell, as shown in *Figure 3*. Configuration bit C2 is used in all state macrocells to select C IN to be active (C2=0) or inactive (C2=1).

Figure 3. CY7C361 Macrocell

For the topmost macrocell (node 32), the C2 bit is used to specify a reset option. If the bit is 0, then the C\_IN for this macrocell will be true (1). If the C2 bit is 1, then the C\_IN for the macrocell will be false (0).

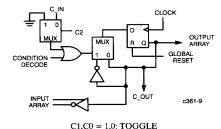

There are three state macrocell configurations: START, TOGGLE, and TERMINATE. The purpose of the START configuration is to create a "token" based on the condition decode. The TOGGLE configuration is used for building counters. The TERMINATE configuration is used to insert wait states in a process. It captures a token and holds it until a condition tells it to terminate the token.

Figure 4 shows a state macrocell in the START configuration. This configuration synchronously creates a token if C\_IN or the condition decode is a logic HIGH. The token is represented by a true output on the macrocell register going to the output array and back as feedback to the input array. A machine implemented in the CY7C361 will consist of multiple machines or processes running concurrently, each with zero, one or more tokens active at any given time. Put another way, each state macrocell in the CY7C361 can be thought of as a line of microcode that can execute concurrently.

Figure 4. Start Configuration

In addition to the main register going to the array, there is an R-S latch in the feedback path that is used to convert the input condition to a pulse.

In operation, the START macrocell starts from a reset condition (output array input = FALSE). When a condition decode "fires" or a token is carried in (C\_IN), the register output (Q going to the array) goes true for exactly one cycle. The OR of the condition decode and the C\_IN must go FALSE before the START configuration can fire again. Local resets have no effect on this configuration

The TERMINATE macrocell (see Figure 5) captures a token via the C\_IN path. The token is then held in the state register until the condition decoder fires, which causes the token to be terminated. Another way of saying this is that the TERMINATE macrocell is like a synchronous SR flip-flop. It is set by C\_IN and reset by the condition decoder. Local resets have no effect on this configuration.

C1,C0 = 0,1: TERMINATE

Figure 5. Terminate Configuration

The TOGGLE macrocell (see Figure 6) operates like a T-type flip-flop. If C\_IN or the condition decode is asserted, the state register will toggle on every rising edge of the internal clock. If neither the C\_IN nor the condition decoder are asserted, the state register will retain its current state. The TOGGLE configuration is used to build counters. A local reset condition will synchronously reset the state register in this configuration.

Figure 6. Toggle Configuration

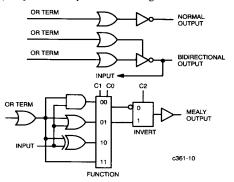

#### The Output Array

The output array is an OR-based array. The array inputs are the LOW-asserted outputs of the 32 state macrocells. There are five types of array outputs. The first type is the three clock enables for the input macrocells. Each enable is a programmable OR of asserted state macrocells; when one of the connected macrocells is asserted, the clock is enabled. Next are the four output enables of the bidirectional I/O pins. Again, the output enables are a programmable OR of the connected asserted state macrocells; when one of the connected macrocells is asserted, the output is enabled. The third type of array output is the "pure" device output. These six outputs are a functional OR of the Low-asserted outputs of the state registers. Next is the output path of the four bidirectional I/O pins, which is identical to that of the "pure" outputs. The last type of array output is the Mealy output macrocell. The CY7C361 has four of these outputs; they can be used as a fast combinatorial out-

put. The three device outputs are pictured in Figure 7. Note that the Mealy output is the only one that is configurable.

Figure 7. Output Configurations

In order to reduce output skew, the CY7C361 output array contains a set of self-timed latches in the output array path. These latches are controlled by an internal clock that has a delay equal to the worst-case path through the output array. While this delayed internal clock is LOW, the output array data is latched. When the delayed internal clock is HIGH, the latches become transparent, and the outputs change. These latches are the reason why the  $t_{\rm CO}$  max is 15 ns with respect to the state registers, but the part can change its outputs every 7.5 ns. Since these latches cannot be accessed by the user, they have been left off of the block diagram.

The normal output signal from the device is a boolean sum of a subset of the state macrocell outputs. The subset selection is programmed into the output array. The number of state machines in the device, and the output mappings of each are determined by the

### **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature 65°C to +150°C                                                       |

|------------------------------------------------------------------------------------------|

| Ambient Temperature with                                                                 |

| Power Applied 55°C to +125°C                                                             |

| Supply Voltage to Ground Potential (DIP Pins 7 or 22 to Pins 8, 21, or 23) 0.5V to +7.0V |

| DC Voltage Applied to Outputs<br>in High Z State                                         |

| DC Voltage Applied to Outputs                                                            |

| During Programming 0.0V to +7.0V                                                         |

| DC Input Voltage                                                                         |

| DC Programming Voltage                                                                   |

|                                                                                          |

user. The architecture is thus "horizontally divisible" and offers advantages in coding efficiency and event response time over the non-divisible architectures found in most PLA and sequencer implementations.

An output pin is normally LOW-asserted. The output gate performs an OR function over the flip-flop outputs of the state macrocells. The OR function includes only the outputs that are programmed to be connected to the OR line in the output array. When none of the connected state macrocell flip-flops are in the true or set condition, the output is HIGH, or deasserted. If any connected macrocell flip-flop is asserted (true) then the OR gate function is true and the output pin is LOW.

Forcing a false condition is easily accomplished by disconnecting all of the state macrocells from the OR line. To force a true condition, the OR line is connected only to node 73, which is labeled as  $V_{CC}$  in the block diagram. Any OR line connected to this node will be forced permanently true, which will cause any normal output to always be LOW.

The bidirectional outputs are I/O pins that may be used as either inputs or outputs. Under state machine control, these pins may be three-stated and used as inputs or outputs depending on how the OE term is programmed. If the OE is connected to node 73, the pin will always function as an output.

The Mealy outputs are designed to implement the fastest possible path between a device input and an output. Functions are available that combine the OR term and a specific input signal. These functions, XOR, AND, and OR, coupled with output polarity control are useful for data strobes and semaphore operations where signaling occurs based on the current state, but independent of a signal transition.

The AND and OR functions can be used to gate data strobe signals by the state. The XOR function can be used to implement two-cycle signaling, which is used in self-timed systems to minimize signaling delays. If these functions are not needed, then the Mealy outputs can be configured as normal outputs.

| Output Current into Outputs (LOW) |

|-----------------------------------|

| UV Exposure                       |

| Latch-Up Current                  |

| Static Discharge Voltage          |

## Operating Range

| Range      | Ambient<br>Temperature | v <sub>cc</sub> |

|------------|------------------------|-----------------|

| Commercial | 0°C to +70°C           | 5V ± 10%        |

| Military   | - 55°C to +125°C       | 5V ± 10%        |

## Electrical Characteristics Over the Operating Range

| Parameter         | Description                  | Test Conditions                                     | s                                    | Min. | Max. | Unit |

|-------------------|------------------------------|-----------------------------------------------------|--------------------------------------|------|------|------|

| V <sub>OH</sub>   | Output HIGH Voltage          | $V_{CC} = Min., V_{IN} = V_{IH} \text{ or } V_{IL}$ | $I_{OH} = -4.0 \text{ mA}$           | 2.4  |      | V    |

| V <sub>OL</sub>   | Output LOW Voltage           | $V_{CC} = Min., V_{IN} = V_{IH} \text{ or } V_{IL}$ | $I_{OL} = 8.0 \text{ mA}$            |      | 0.4  | V    |

| $V_{IH}$          | Input HIGH Level             | Guaranteed HIGH Input, All Inp                      | Guaranteed HIGH Input, All Inputs[1] |      |      | V    |

| V <sub>IL</sub>   | Input LOW Level              | Guaranteed LOW Input, All Inputs[1]                 |                                      |      | 0.8  | V    |

| $I_{IX}$          | Input Leakage Current        | $V_{SS} < V_{IN} < V_{CC}, V_{CC} = Max.$           |                                      | -10  | +10  | μΑ   |

| I <sub>OZ</sub>   | Output Leakage Current       | $V_{CC} = Max., V_{SS} < V_{OUT} < V_{CC}$          |                                      | - 40 | +40  | μΑ   |

| $I_{SC}^{[2]}$    | Output Short Circuit Current | $V_{CC} = Max., V_{OUT} = 0.5V^{[3]}$               |                                      | -30  | -110 | mA   |

| $I_{CC}^{[2, 4]}$ | Power Supply Current         | $V_{CC} = Max., V_{IN} = GND,$ Commercial           |                                      |      | 200  | mA   |

|                   |                              | Outputs Open,<br>Operating at $f = f_{MAX}$         | Military                             |      |      |      |

#### Notes:

- These are absolute values with respect to device ground and all overshoots due to system or tester noise are included.

- 2. Tested initially and after any design or process changes that may affect this parameter.

- Not more than one output should be tested at a time. Duration of the short circuit should not be more than one second. V<sub>QUT</sub> = 0.5V has been chosen to avoid test problems caused by tester ground degradation.

- 4. Tested with device programmed as an 8-bit counter.

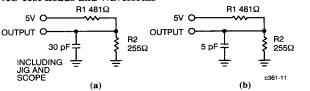

## **AC Test Loads and Waveforms**

Equivalent to: THÉVENIN EQUIVALENT

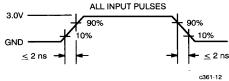

## **Test Waveforms**

| Parameter           | V <sub>X</sub>  |                   | Output Waveform—Measurement Level |

|---------------------|-----------------|-------------------|-----------------------------------|

| t <sub>CER(-)</sub> | 0.0V            | V <sub>OH</sub> – | 0.5V VX c361-14                   |

| t <sub>CER(+)</sub> | 2.6V            | V <sub>OL</sub> _ | 0.5V <sub>X</sub> V <sub>X</sub>  |

| t <sub>CEA(+)</sub> | V <sub>th</sub> | V <sub>X</sub> -  | 0.5V V <sub>OH</sub>              |

| t <sub>CEA(-)</sub> | $V_{th}$        | V <sub>X</sub> -  | 0.5V V <sub>OL</sub> c361-17      |

## Commercial Switching Characteristics Over the Operating Range [5, 6]

|                              |                                                | _     | 125         | _     | 100      | _        | -83        |      |

|------------------------------|------------------------------------------------|-------|-------------|-------|----------|----------|------------|------|

| Parameter                    | Description                                    | Min.  | Max.        | Min.  | Max.     | Min.     | Max.       | Unit |

| t <sub>PD</sub>              | Input to Mealy Output Delay                    | 2     | 9           | 2     | 11       | 2        | 12         | ns   |

| t <sub>CO</sub> [7]          | Clock to Output Delay                          |       | 15          |       | 19       |          | 23         | ns   |

| t <sub>CM</sub> [7]          | Clock to Mealy Output Delay                    |       | 17          |       | 20       | <u> </u> | 25         | ns   |

| t <sub>OH</sub>              | Output Stable Time                             | 5     | <u> </u>    | 5     |          | 5        |            | ns   |

| t <sub>IS</sub>              | Input Register Input Set-Up Time               | 2     | <del></del> | 3     | <u> </u> | 5        |            | ns   |

| t <sub>IH</sub>              | Input Register Input Hold Time                 | 3     |             | 4     | 1        | 5        |            | ns   |

| t <sub>S</sub> [8]           | State Register Input Set-Up Time               | 7     |             | 9     | <u> </u> | 12       |            | ns   |

| t <sub>H</sub> [8]           | State Register Input Hold Time                 | 0     | <u> </u>    | 0     | -        | 0        | <b></b>    | ns   |

| t <sub>DWH</sub> [2, 9, 10]  | Input Clock Pulse Width HIGH (Doubler Enabled) | 6     |             | 7     |          | 9        |            | ns   |

| t <sub>DWL</sub> [2, 9, 10]  | Input Clock Pulse Width LOW (Doubler Enabled)  | 6     |             | 7     |          | 9        |            | ns   |

| t <sub>DP</sub> [2, 10]      | Input Clock Period (Doubler Enabled)           | 15    |             | 20    |          | 24       |            | ns   |

| t <sub>WH</sub> [2, 9, 11]   | Input Clock Pulse Width HIGH                   | 2     |             | 3     |          | 4        | <b>—</b> — | ns   |

| t <sub>WL</sub> [2, 9, 11]   | Input Clock Pulse Width LOW                    | 2     |             | 3     | -        | 4        |            | ns   |

| t <sub>P</sub> [2, 11]       | Input Clock Period                             | 7.5   |             | 10    |          | 12       |            | ns   |

| t <sub>SO</sub> [12]         | Output Skew                                    |       | 2           |       | 2        |          | 2          | ns   |

| t <sub>SM</sub> [13]         | Mealy Output Skew                              |       | 3           |       | 3        |          | 3          | ns   |

| f <sub>MAXI</sub> [2, 11]    | Input Maximum Frequency (Doubler Enabled)      | 62.5  |             | 50.0  |          | 41.7     |            | MHz  |

| f <sub>MAX</sub> [2, 4]      | Output Maximum Frequency                       | 125.0 |             | 100.0 |          | 83.3     |            | MHz  |

| t <sub>CER</sub> [2, 6]      | Clock to Output Disable Delay                  |       | 16          |       | 20       | _        | 22         | ns   |

| t <sub>CEA</sub> [2, 14, 15] | Clock to Output Enable Delay                   |       | 16          |       | 20       |          | 22         | ns   |

## Notes:

- Output reference point on AC measurements is 1.5V, except as noted in Test Waveforms;

- tCER(+) positive going is measured at V<sub>OH</sub> 0.5V. t<sub>CER(+)</sub> positive going is measured at V<sub>OL</sub> + 0.5V Part (a) of AC Test Loads and Waveforms is used for all parameters

- Part (a) of AC Test Loads and Waveforms is used for all parameters except t<sub>CEA</sub> and t<sub>CER</sub>. Part (b) of AC Test Loads and Waveforms is used for t<sub>CEA</sub> and t<sub>CER</sub>.

- This specification is guaranteed for the worst-case programmed pattern for which all device outputs are changing state on a given access or clock cycle.

- Input register bypassed.

- The clock input is tested to accommodate a 60/40 duty cycle waveform at the maximum frequency.

- 10. This applies to the input clock when the doubler is enabled.

- 11. This applies to the input clock when the doubler is disabled.

- 12. This parameter specifies the maximum allowable t<sub>CO</sub> clock to output delay difference, or skew, between any two outputs on the same device triggered by the same clock edge with all other device outputs changing state within the same clock cycle.

- 13. This parameter specifies the maximum allowable tpp difference between any two Mealy outputs on the same device triggered by the same or simultaneous input signals with all other device outputs changing state within the same access or clock cycle.

- R1 is disconnected for t<sub>CEA(+)</sub> positive going (open circuited). See part (b) of AC Test Loads and Waveforms.

- R2 is disconnected for t<sub>CEA(-)</sub> negative going (open circuited). See part (b) of AC Test Loads and Waveforms.

# Military Switching Characteristics Over the Operating Range [5,6]

|                                 |                                                   | -     | Mil  | itary |      |      |

|---------------------------------|---------------------------------------------------|-------|------|-------|------|------|

|                                 |                                                   | -1    | _    | 1     |      |      |

| Parameter                       | Description                                       | Min.  | Max. | Min.  | Max. | Unit |

| t <sub>PD</sub>                 | Input to Mealy Output Delay                       | 1.5   | 11   | 1.5   | 13   | ns   |

| t <sub>CO</sub> [7]             | Clock to Output Delay                             |       | 19   |       | 23   | ns   |

| t <sub>CM</sub> <sup>[7]</sup>  | Clock to Mealy Output Delay                       |       | 21   |       | 25   | ns   |

| t <sub>OH</sub>                 | Output Stable Time                                | 5     |      | 5     |      | ns   |

| t <sub>IS</sub>                 | Input Register Input Set-Up Time                  | 3     |      | 5     |      | ns   |

| t <sub>IH</sub>                 | Input Register Input Hold Time                    | 4     |      | 5     | 1    | ns   |

| t <sub>S</sub> [8]              | State Register Input Set-Up Time                  | 9     |      | 12    | Ī    | ns   |

| t <sub>H</sub> [8]              | State Register Input Hold Time                    | 0     |      | 0     |      | ns   |

| t <sub>DWH</sub> [2, 9, 10]     | Input Clock Pulse Width HIGH<br>(Doubler Enabled) | 7     |      | 9     |      | ns   |

| t <sub>DWL</sub> [2, 9, 10]     | Input Clock Pulse Width LOW<br>(Doubler Enabled)  | 7     |      | 9     |      | ns   |

| t <sub>DP</sub> [2, 10]         | Input Clock Period (Doubler Enabled)              | 20    |      | 24    |      | ns   |

| twH <sup>[2, 9, 11]</sup>       | Input Clock Pulse Width HIGH                      | 3     |      | 4     |      | ns   |

| t <sub>WL</sub> [2, 9, 11]      | Input Clock Pulse Width LOW                       | 3     |      | 4     |      | ns   |

| tp[2, 11]                       | Input Clock Period                                | 10    |      | 12    |      | ns   |

| t <sub>SO</sub> <sup>[12]</sup> | Output Skew                                       |       | 3    |       | 3    | ns   |

| t <sub>SM</sub> [13]            | Mealy Output Skew                                 |       | 4    |       | 4    | ns   |

| f <sub>MAXI</sub> [2, 11]       | Input Maximum Frequency (Doubler Enabled)         | 50    |      | 41.7  |      | MHz  |

| f <sub>MAX</sub> [2, 4]         | Output Maximum Frequency                          | 100.0 |      | 83.3  |      | MHz  |

| t <sub>CER</sub> [6]            | Clock to Output Disable Delay                     |       | 20   |       | 22   | ns   |

| t <sub>CEA</sub> [2, 14, 15]    | Clock to Output Enable Delay                      |       | 20   | 1     | 22   | ns   |

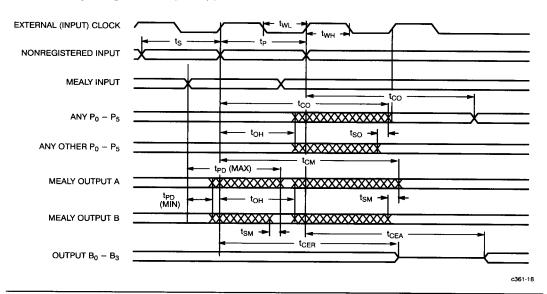

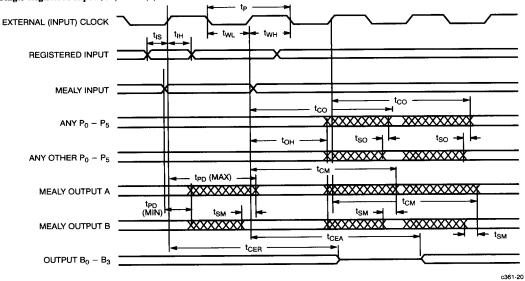

## **Switching Waveforms**

Clock Doubler Inactive (Virgin State). Nonregistered Input (Virgin State -C1,C0=0,0).

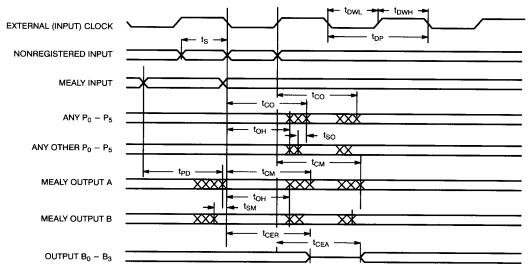

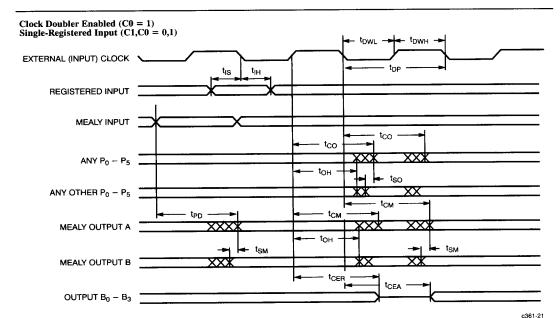

Clock Doubler Enabled (C0 = 1) Nonregistered Input (Virgin State -C1,C0 = 0,0)

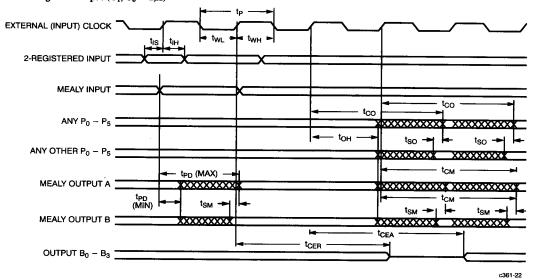

## Switching Waveforms (continued)

Clock Doubler Inactive (Virgin State). Single-Registered Input (C1,C0=0,1).

## Switching Waveforms (continued)

Clock Doubler Inactive (Virgin State) Double-Registered Input  $(C_1, C_0 = 1, X)$

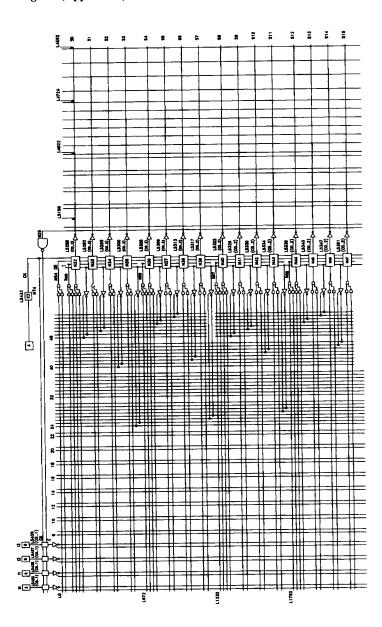

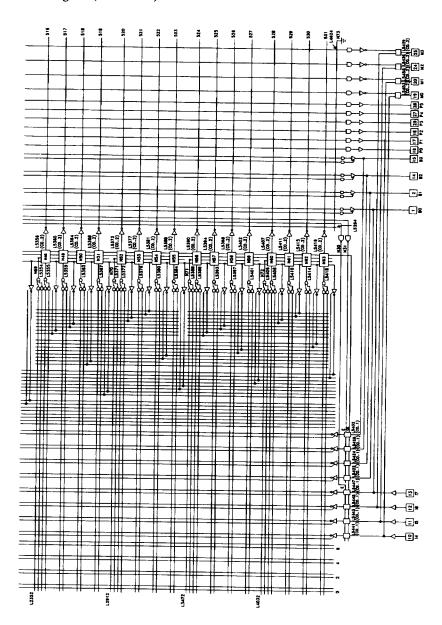

# CY7C361 Block Diagram (Upper Half)

## CY7C361 Block Diagram (Lower Half)

## **Ordering Information**

| I <sub>CC</sub> mA | f <sub>MAX</sub><br>MHz | Ordering Code  | Package<br>Name | Package Type                          | Operating<br>Range |

|--------------------|-------------------------|----------------|-----------------|---------------------------------------|--------------------|

| 200                | 125.0                   | CY7C361-125HC  | H64             | 28-Pin Windowed Leaded Chip Carrier   | Commercial         |

|                    |                         | CY7C361-125WC  | W22             | 28-Lead (300-Mil) Windowed CerDIP     | 1                  |

|                    | 100.0                   | CY7C361-100HC  | H64             | 28-Pin Windowed Leaded Chip Carrier   | Commercial         |

|                    |                         | CY7C361-100WC  | W22             | 28-Lead (300-Mil) Windowed CerDIP     | 1                  |

|                    |                         | CY7C361-100HMB | H64             | 28-Pin Windowed Leaded Chip Carrier   | Military           |

|                    |                         | CY7C361-100QMB | Q64             | 28-Pin Windowed Leadless Chip Carrier | 1                  |

|                    |                         | CY7C361-100WMB | W22             | 28-Lead (300-Mil) Windowed CerDIP     |                    |

|                    | 83.3                    | CY7C361-83HC   | H64             | 28-Pin Windowed Leaded Chip Carrier   | Commercial         |

|                    |                         | CY7C361-83WC   | W22             | 28-Lead (300-Mil) Windowed CerDIP     | 1                  |

|                    |                         | CY7C361-83HMB  | H64             | 28-Pin Windowed Leaded Chip Carrier   | Military           |

|                    |                         | CY7C361-83QMB  | Q64             | 28-Pin Windowed Leadless Chip Carrier | 1                  |

|                    |                         | CY7C361-83WMB  | W22             | 28-Lead (300-Mil) Windowed CerDIP     | 1                  |

# MILITARY SPECIFICATIONS Group A Subgroup Testing

## **DC Characteristics**

| Parameter       | Subgroups |

|-----------------|-----------|

| $V_{OH}$        | 1, 2, 3   |

| V <sub>OL</sub> | 1, 2, 3   |

| V <sub>IH</sub> | 1, 2, 3   |

| $V_{IL}$        | 1, 2, 3   |

| I <sub>IX</sub> | 1, 2, 3   |

| I <sub>OZ</sub> | 1, 2, 3   |

# **Switching Characteristics**

| Parameter       | Subgroups       |

|-----------------|-----------------|

| t <sub>PD</sub> | 7, 8, 9, 10, 11 |

| t <sub>CO</sub> | 7, 8, 9, 10, 11 |

| t <sub>CM</sub> | 7, 8, 9, 10, 11 |

| t <sub>OH</sub> | 7, 8, 9, 10, 11 |

| t <sub>IS</sub> | 7, 8, 9, 10, 11 |

| t <sub>IH</sub> | 7, 8, 9, 10, 11 |

| t <sub>S</sub>  | 7, 8, 9, 10, 11 |

| t <sub>H</sub>  | 7, 8, 9, 10, 11 |

Document #: 38-00106-C