# M30218 Group User's manual (tentative)

Specifications written in this user's manual are believed to be accurate, but are not guaranteed to be entirely free of error.

Specifications in this manual may be changed for functional or performance improvements. Please make sure your manual is the latest edition.

#### -Keep safety first in your circuit designs!-

• Mitsubishi Electric Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of non-flammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection

of the Mitsubishi semiconductor product best suited to the customer's application;

they do not convey any license under any intellectual property rights, or any other

rights, belonging to Mitsubishi Electric Corporation or a third party.

- Mitsubishi Electric Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Mitsubishi Electric Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors. Mitsubishi Electric Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Mitsubishi Electric Corporation by various means, including the Mitsubishi Semiconductor home page (http://www.mitsubishichips.com).

- When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Mitsubishi Electric Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- Mitsubishi Electric Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- The prior written approval of Mitsubishi Electric Corporation is necessary to reprint or reproduce in whole or in part these materials.

- If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semicon ductor product distributor for further details on these materials or the products con tained therein.

#### **Preface**

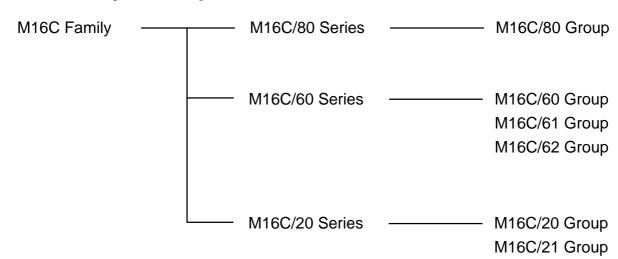

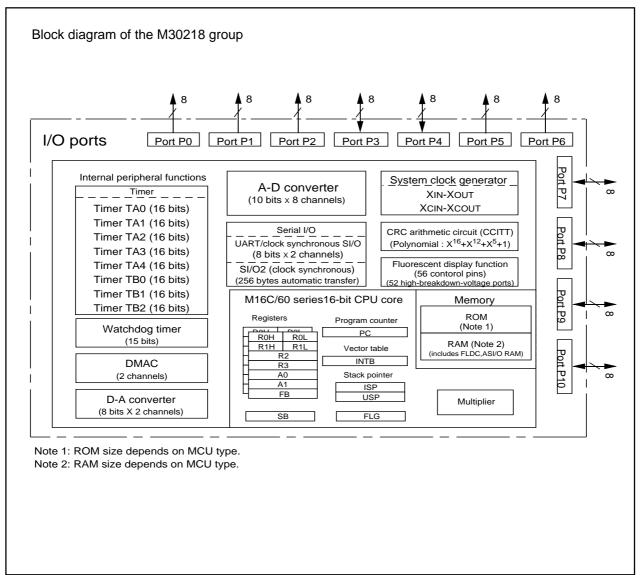

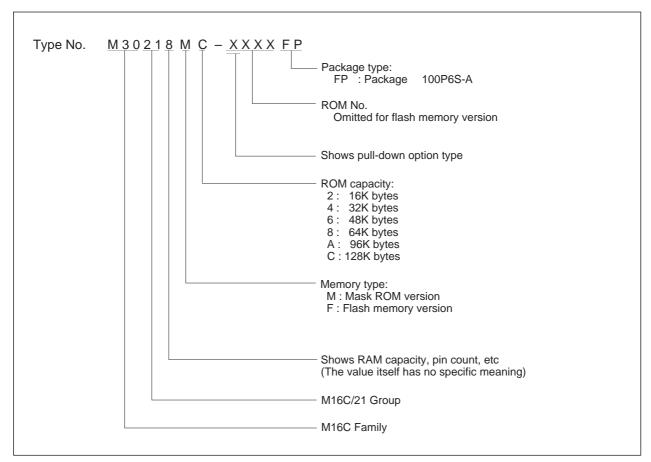

This user's manual describes the function and features of the Mitsubishi M30218 Group CMOS 16-bit microcomputer. The software features are explained to help designers take full advantage of the M16C functions.

For details about the software, please refer to the "M16C/60, M16C/20 series software manual", and for the development support tools, please refer to the related instruction manual.

#### How to Use This Manual

This user's manual is written for the M30218 group.

The reader of this manual is expected to have the basic knowledge of electric and logic circuits and microcomputers.

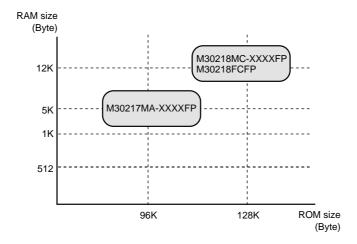

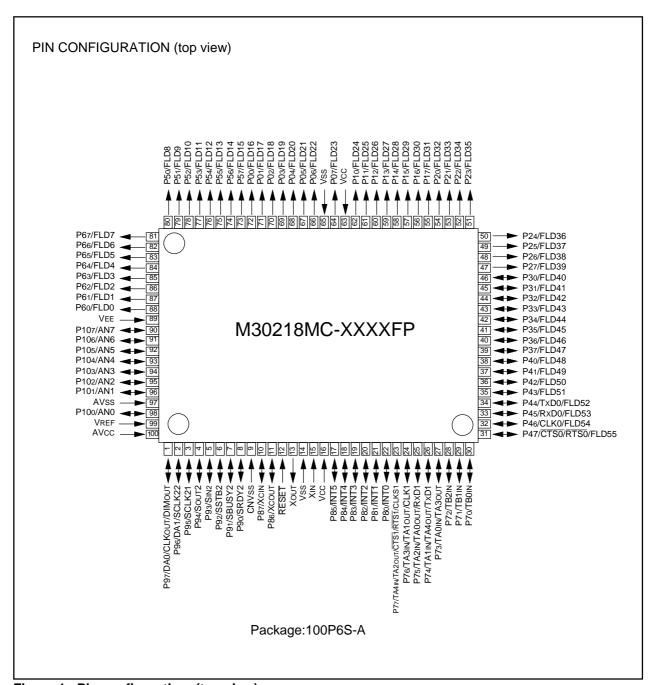

This manual is for the use of the models below.

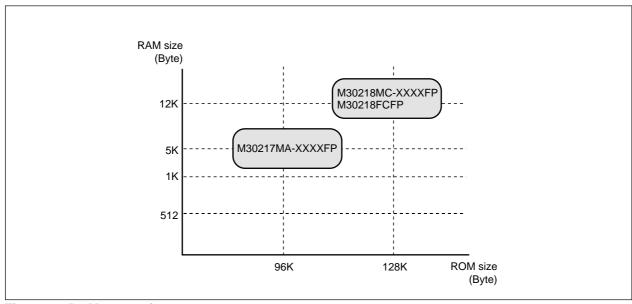

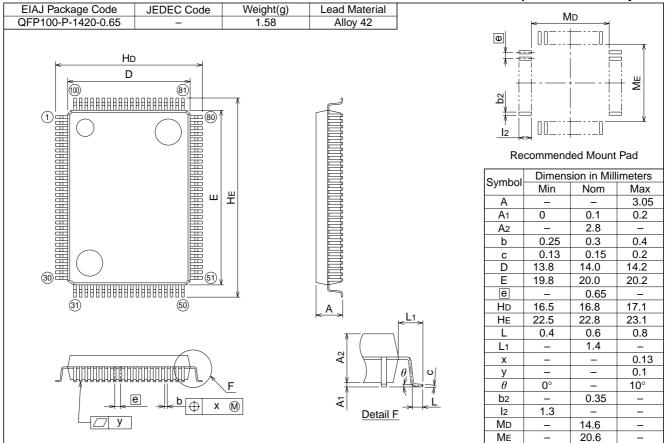

- M30217MA-XXXXFP

- M30218MC-XXXXFP

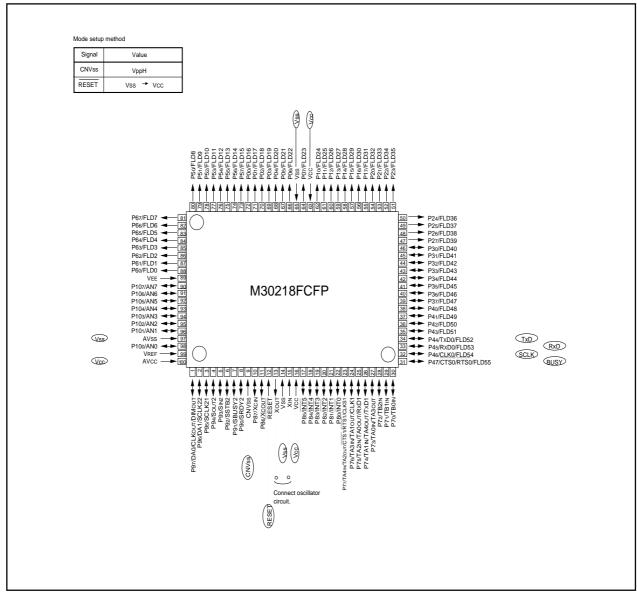

- M30218FCFP

These products have similar features except for the memories, which differ from one product to another. This manual gives descriptions of M30218MC-XXXXFP. Memories built-in are as shown below. Be careful when writing a program, as the memories have different capacities.

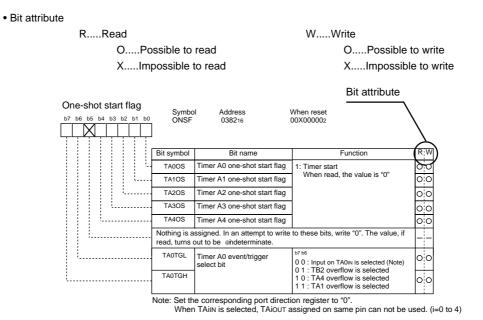

The figure of each register configuration describes its functions, contents at reset, and attributes as follows:

| This manual comprises of five chapters. Use the suggested chapters as a referer following topics: | nce for the  |

|---------------------------------------------------------------------------------------------------|--------------|

| * To understand hardware specifications Chapter 1                                                 | Hardware     |

| * To understand the basic way of using peripheral features and the operation timing               | ons Usage    |

| * To observe applications of peripheral features                                                  | pplications  |

| * To understand interrupt timing in detail                                                        |              |

|                                                                                                   | Interrupts   |

| * To understand standard dataChapter 5 Standard Cha                                               | •            |

|                                                                                                   | racteristics |

## M16C Family-related document list

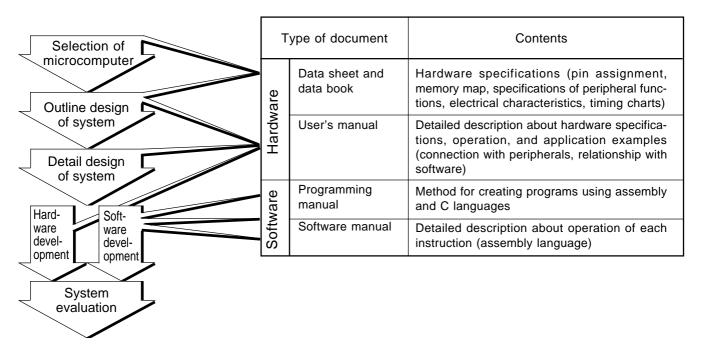

## Usages (Microcomputer development flow)

## M16C Family Line-up

## **Table of Contents**

| Description                                                          | 2   |

|----------------------------------------------------------------------|-----|

| Pin Description                                                      |     |

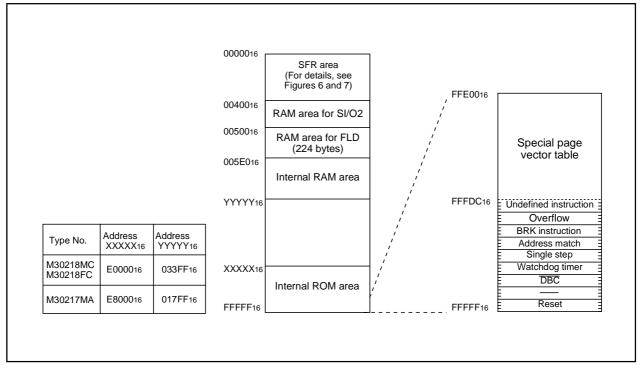

| Memory                                                               | 9   |

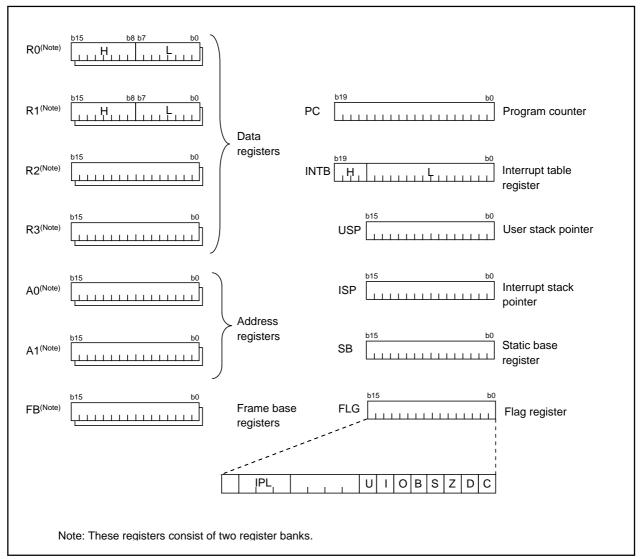

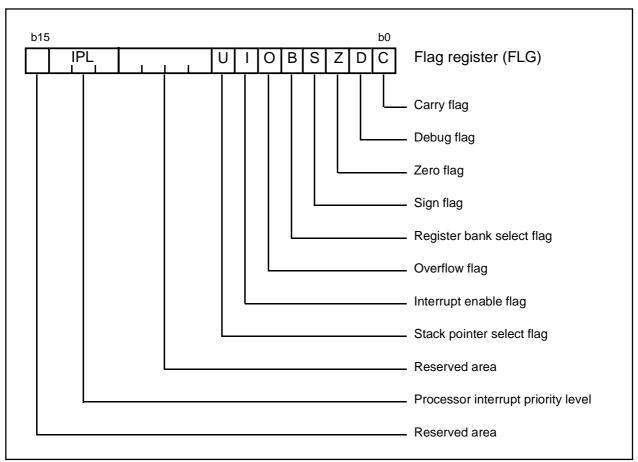

| Central Processing Unit (CPU)                                        | 12  |

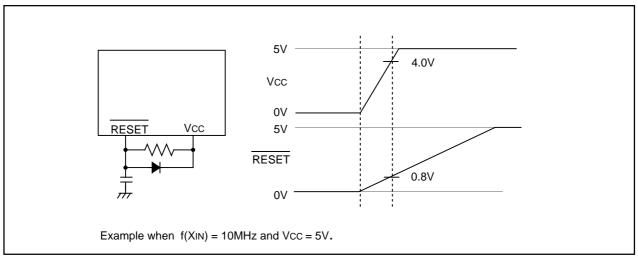

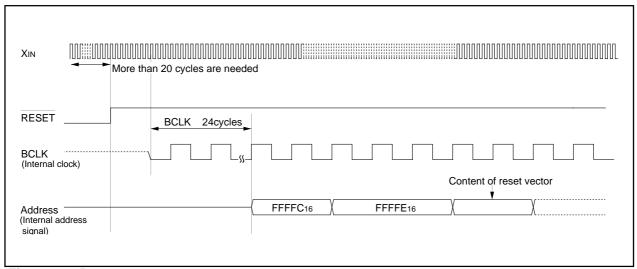

| Reset                                                                | 15  |

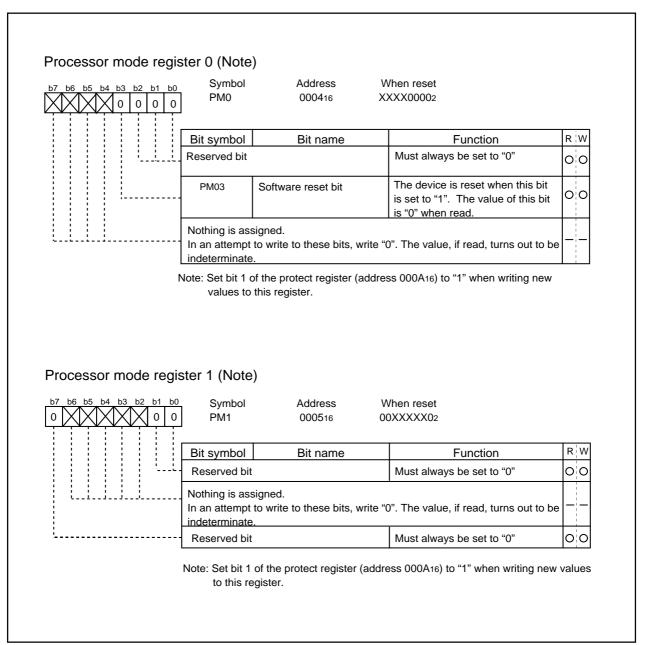

| Software Reset                                                       | 18  |

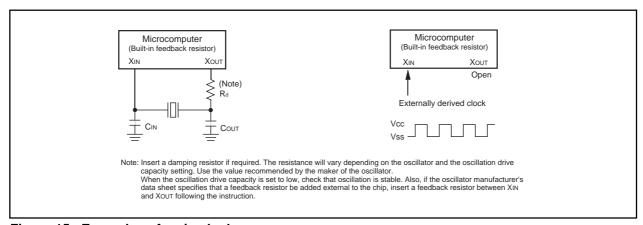

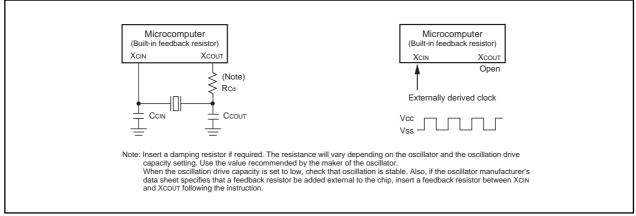

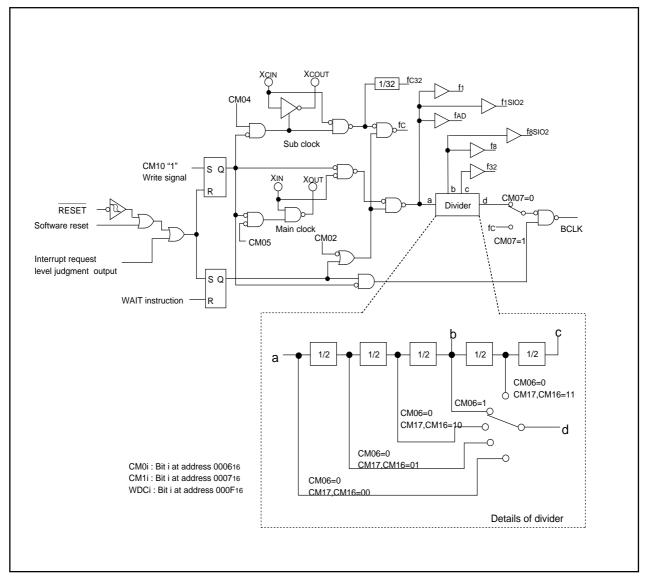

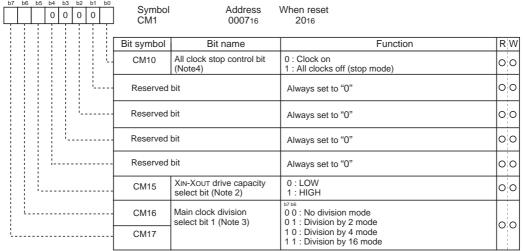

| Clock Generating Circuit                                             | 19  |

| Clock Output                                                         | 23  |

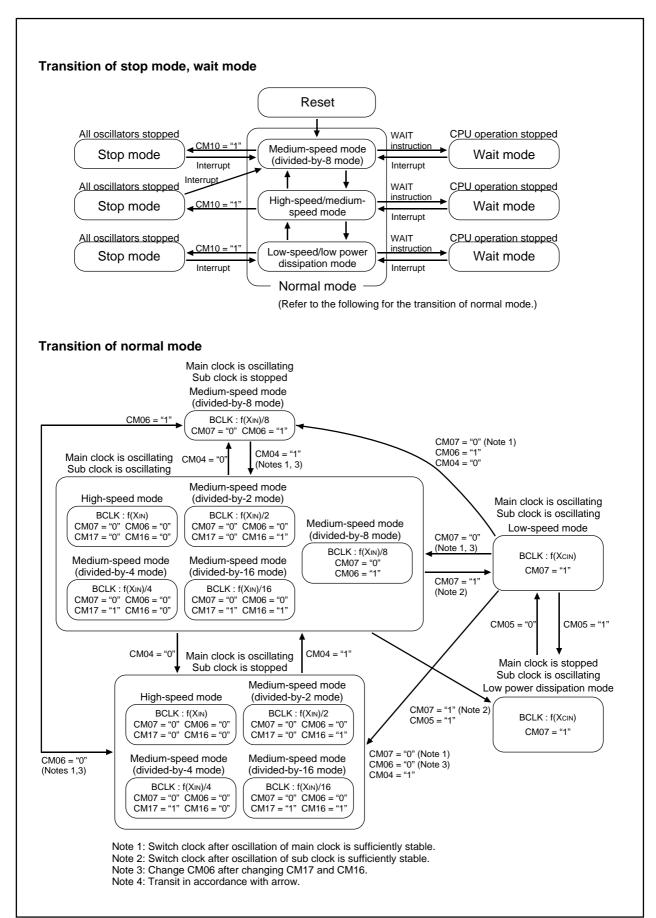

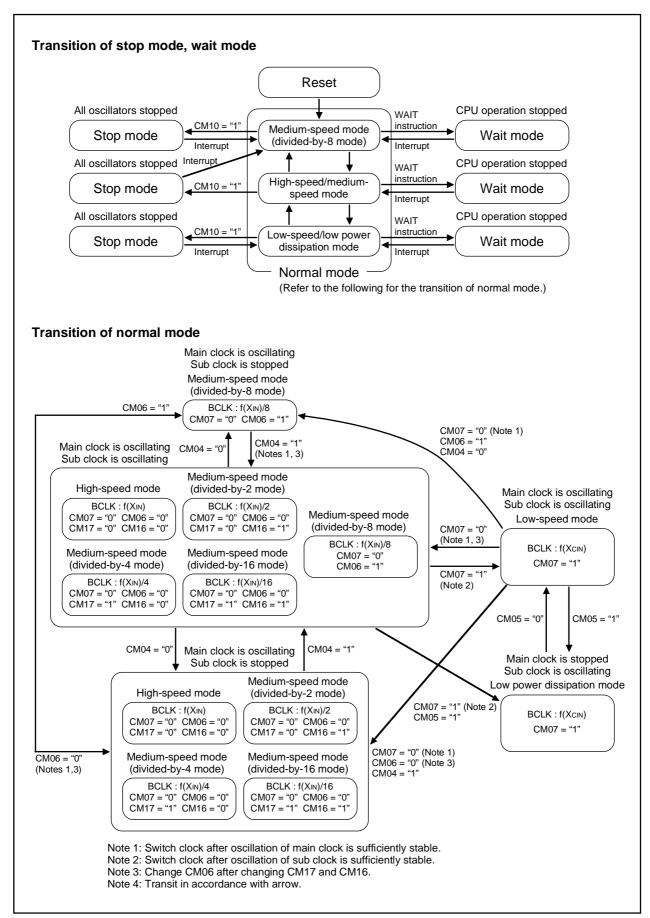

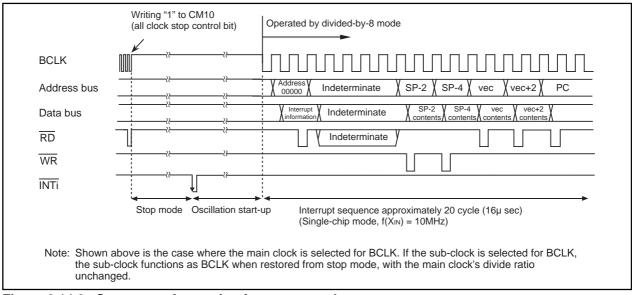

| Stop Mode                                                            | 23  |

| Wait Mode                                                            | 23  |

| Status Transition Of BCLK                                            | 24  |

| Power Control                                                        | 2   |

| Protection                                                           | 27  |

| Overview of Interrupt                                                | 28  |

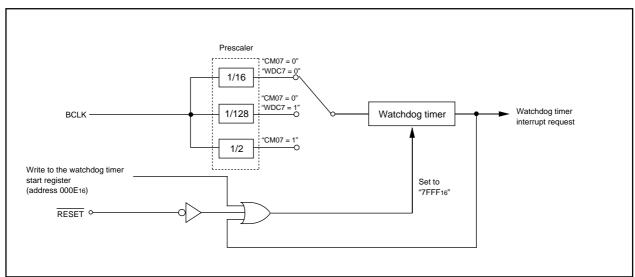

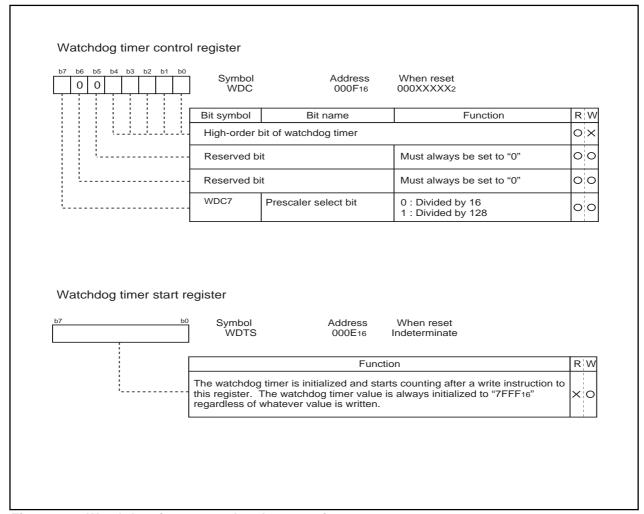

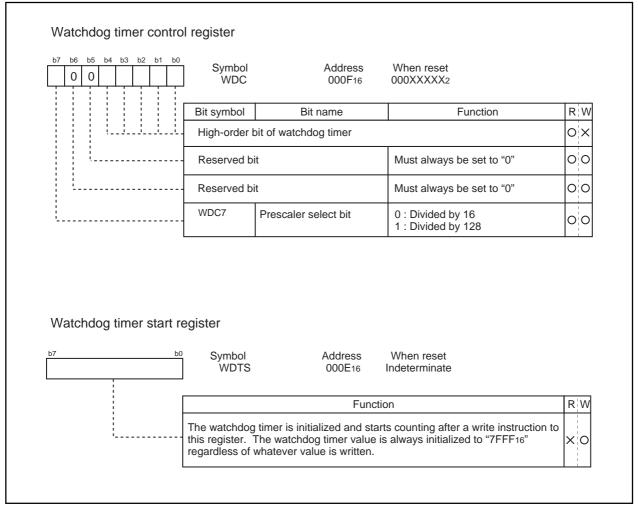

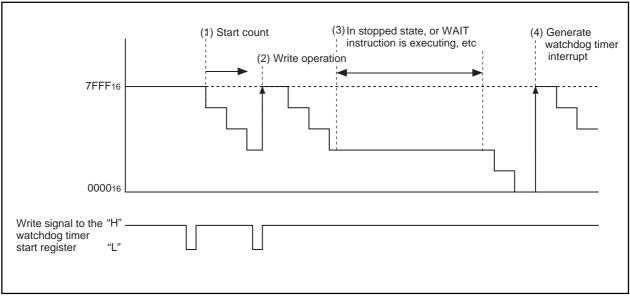

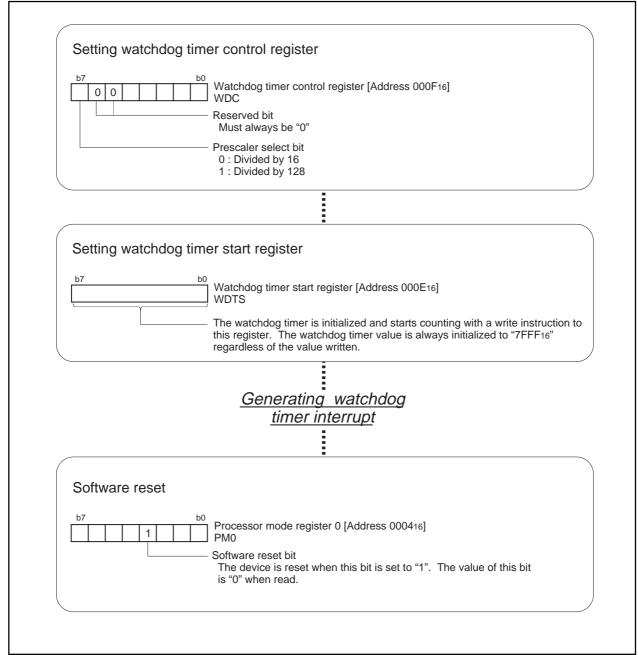

| Watchdog Timer                                                       | 46  |

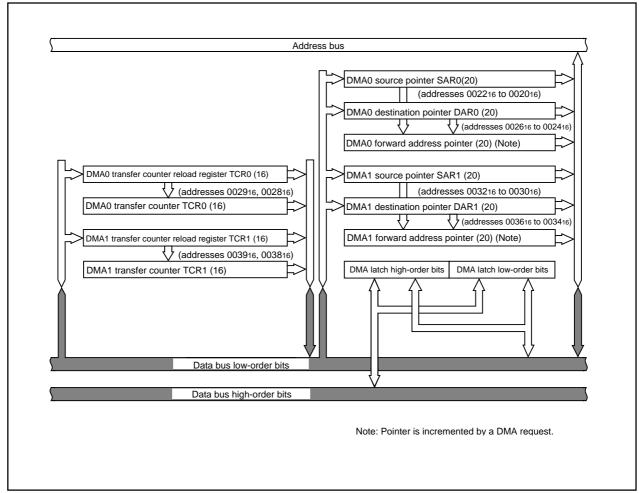

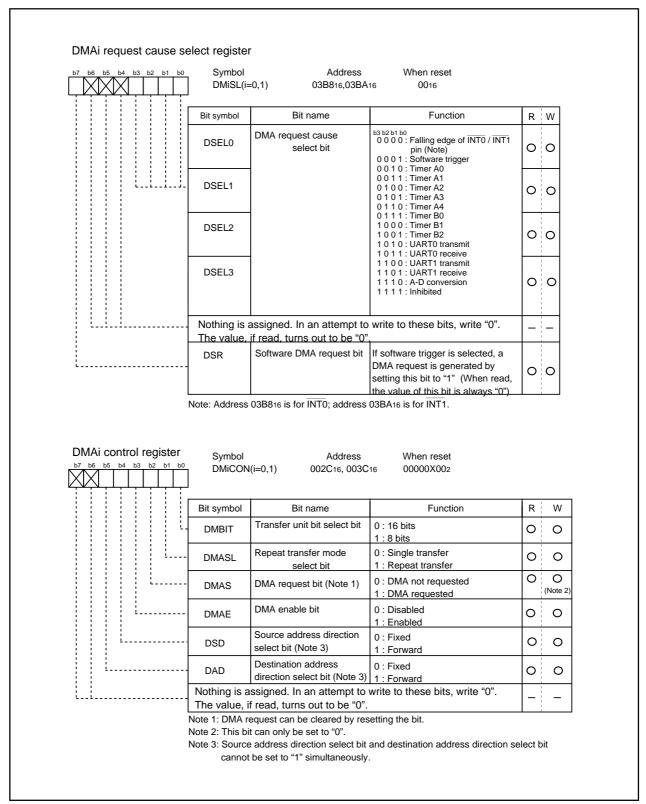

| DMAC                                                                 | 48  |

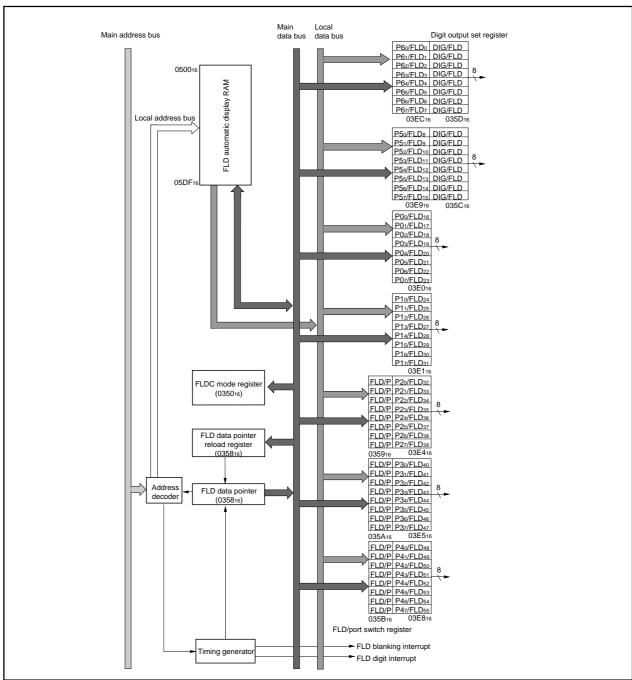

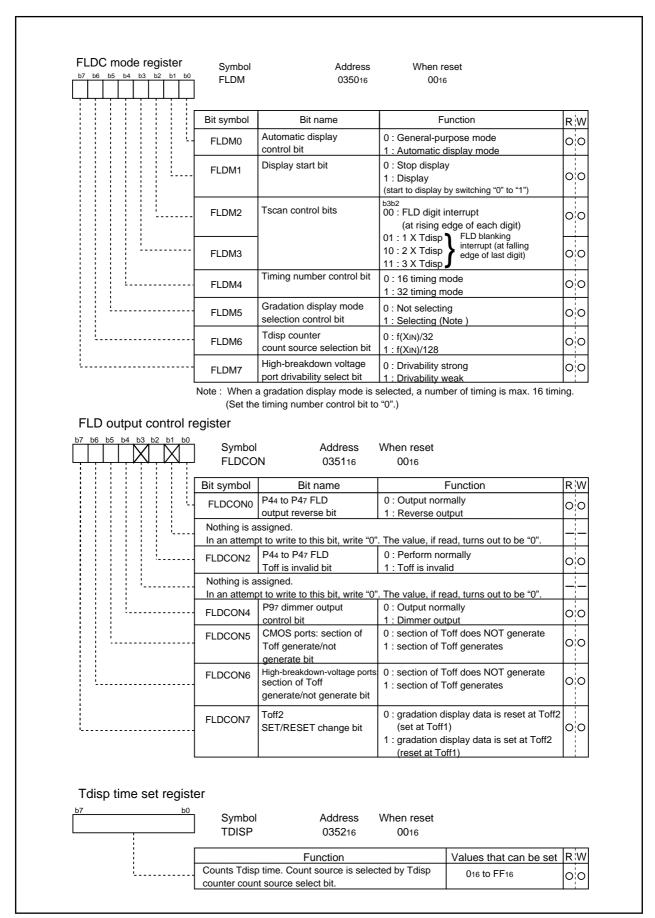

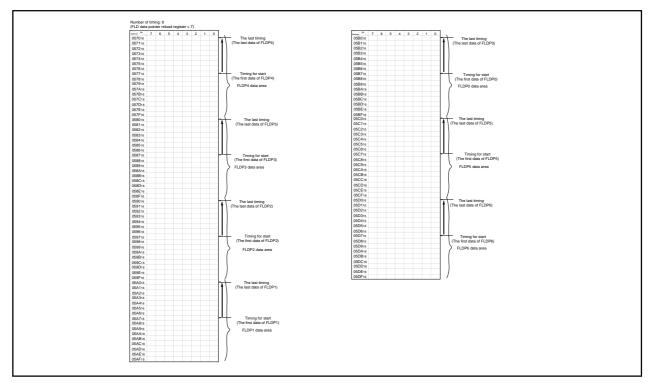

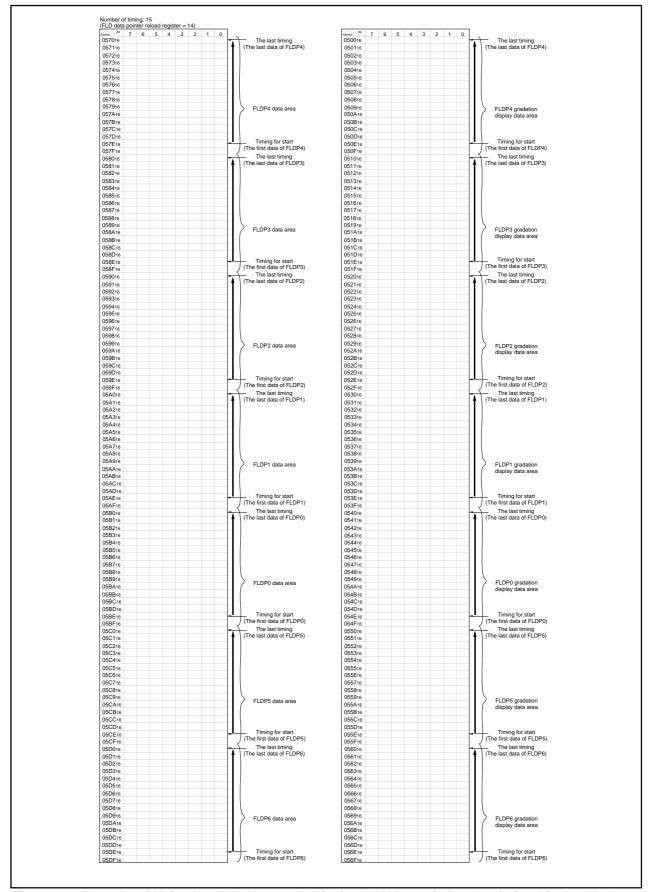

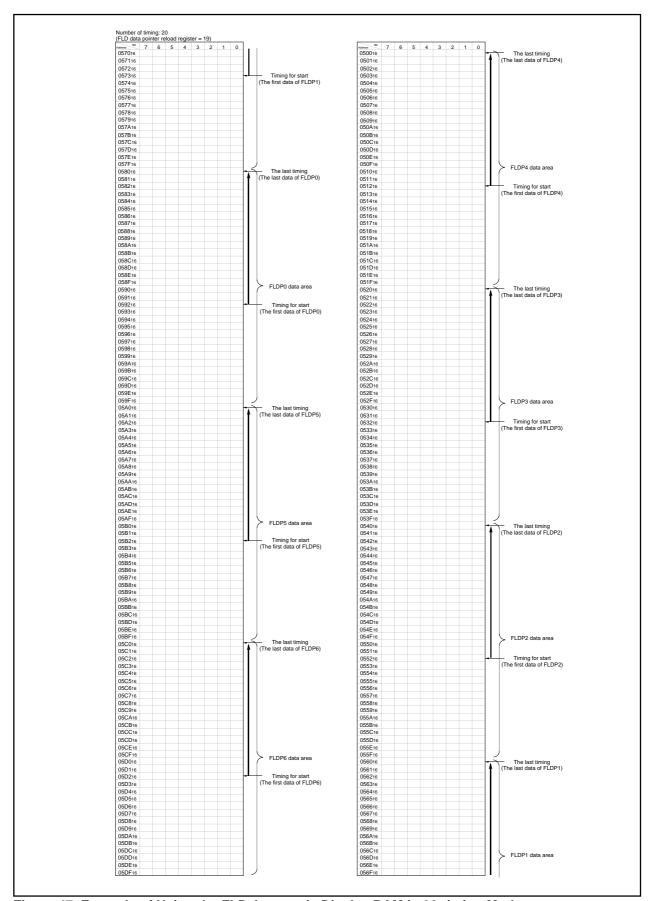

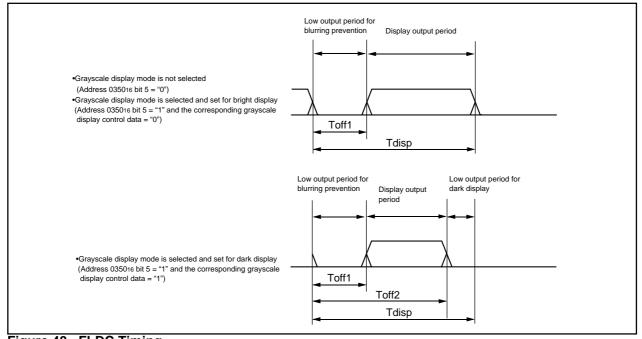

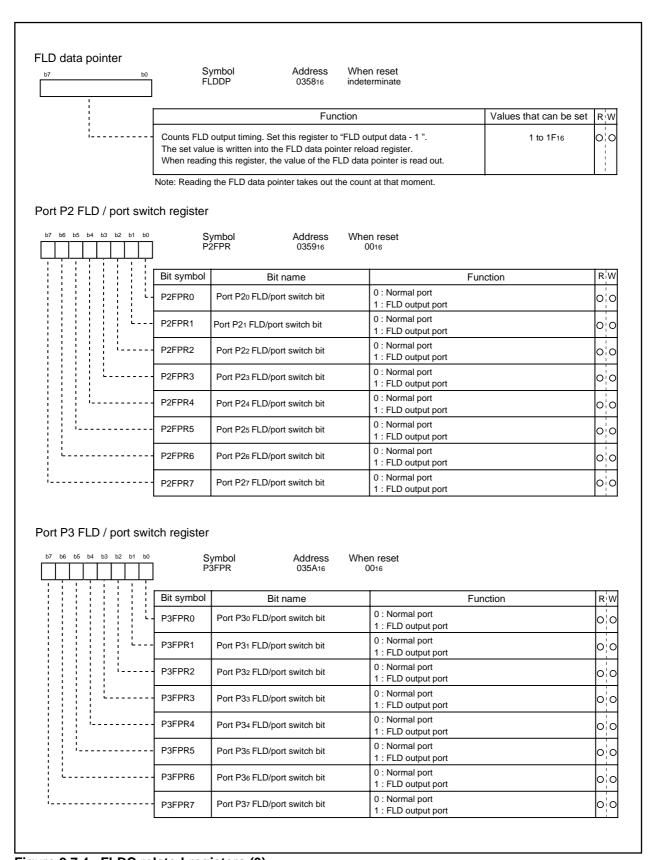

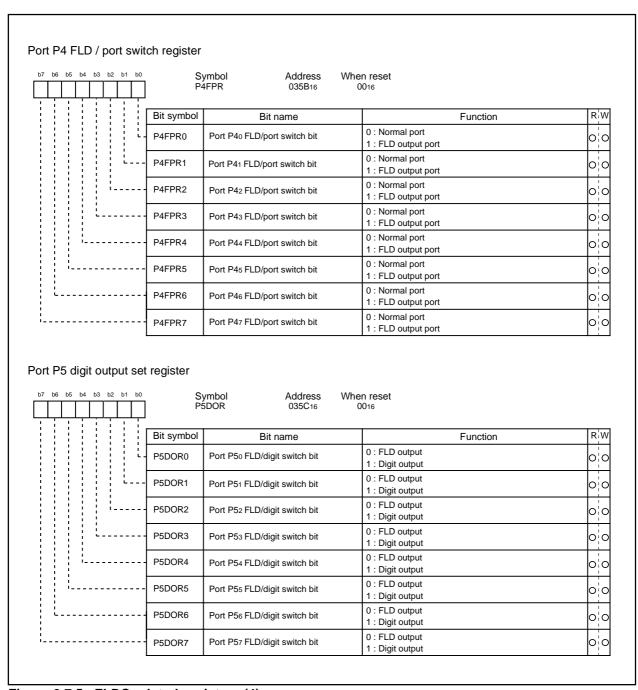

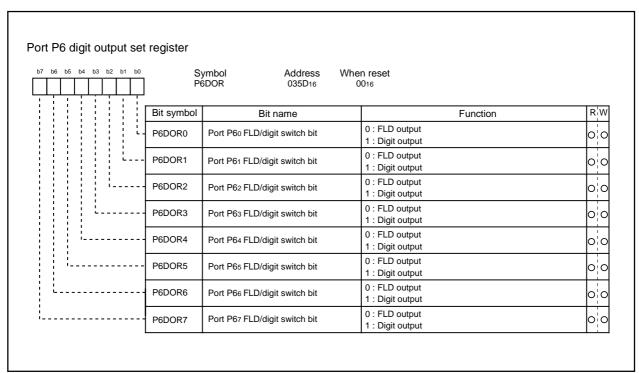

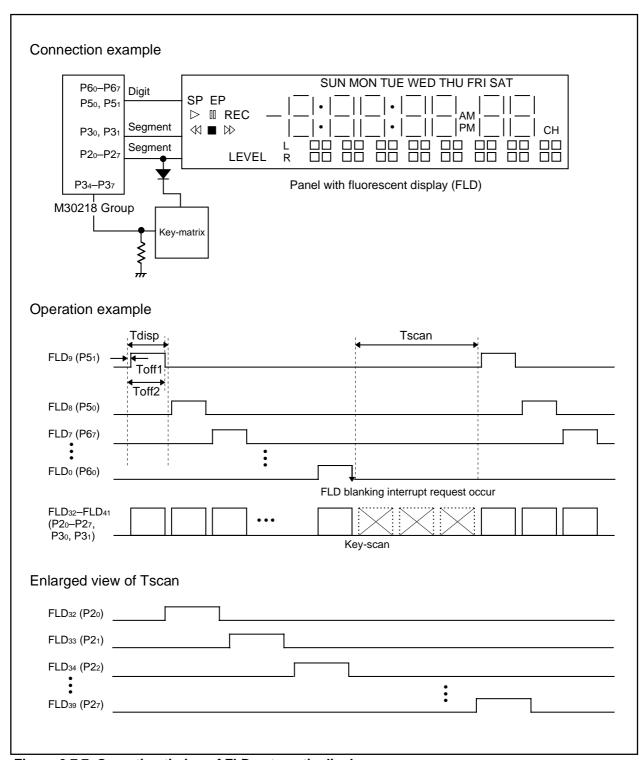

| FLD Controller                                                       | 54  |

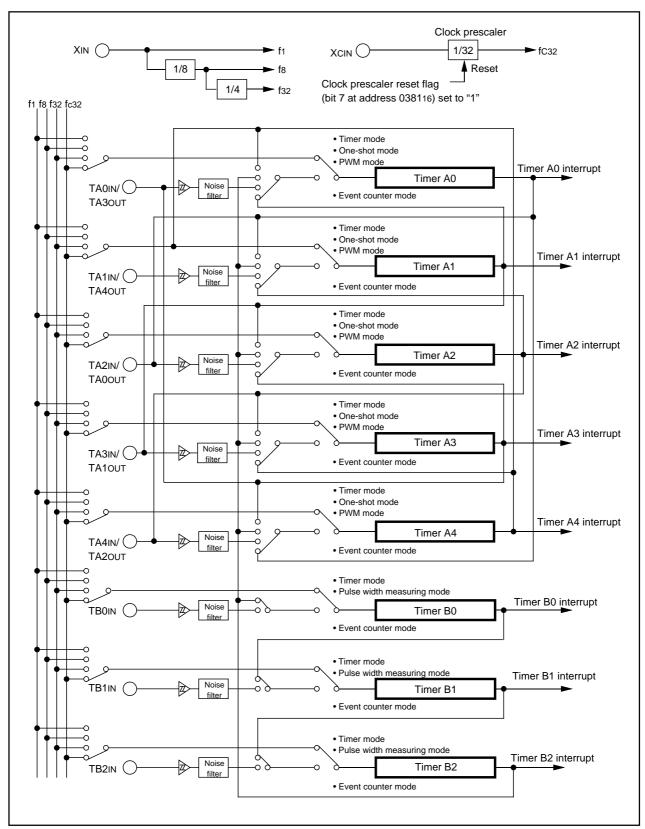

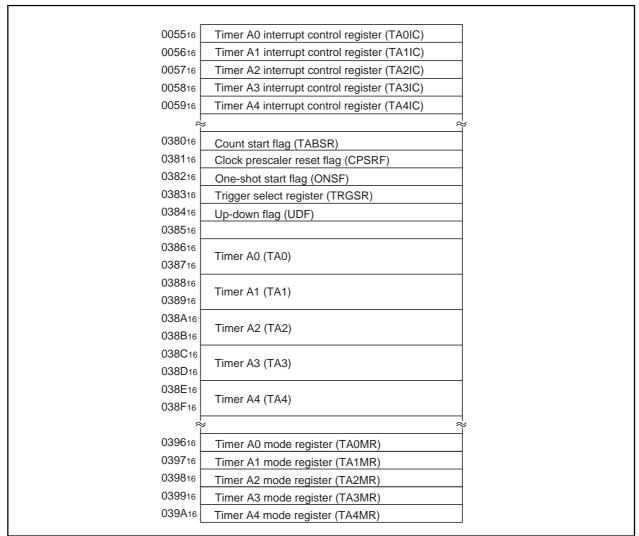

| Timer                                                                | 7   |

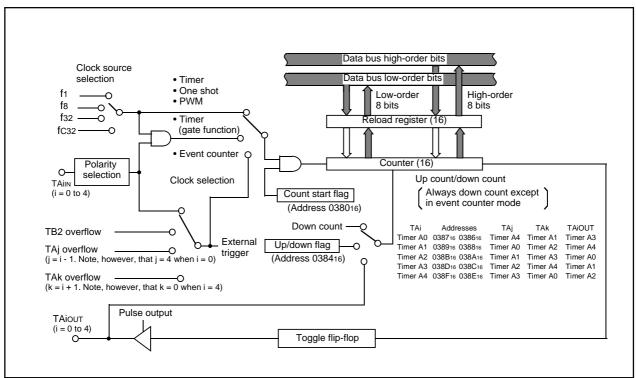

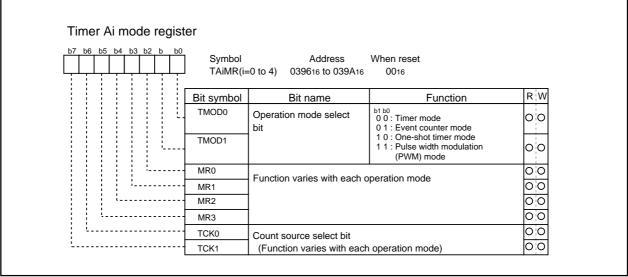

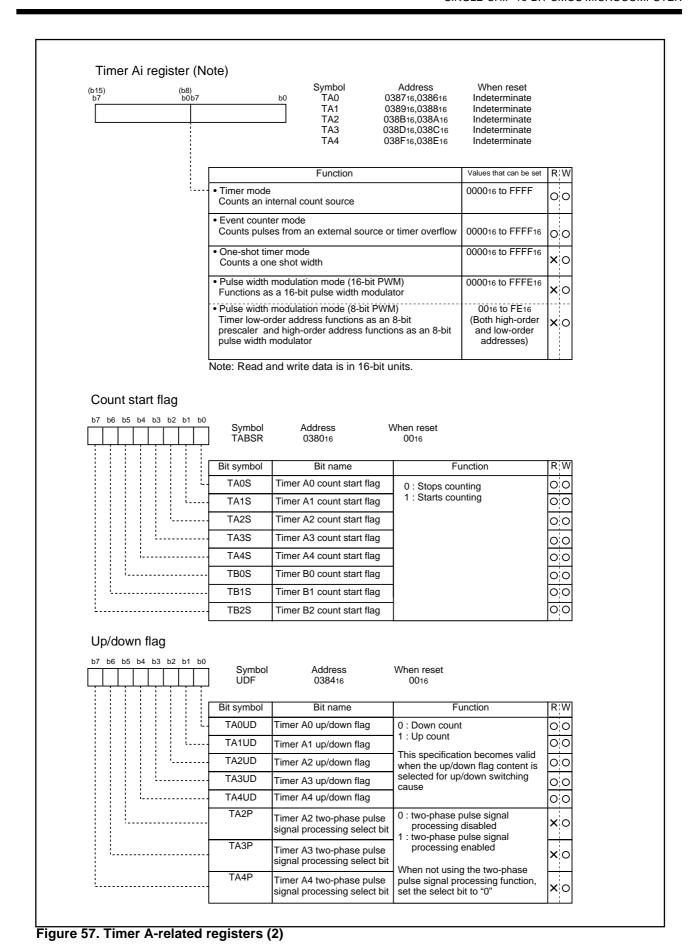

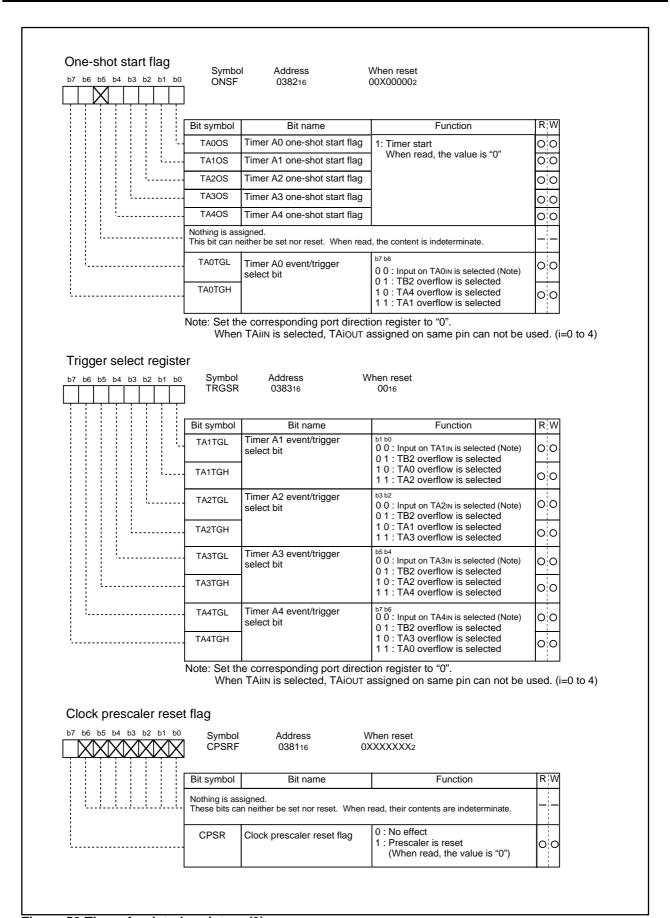

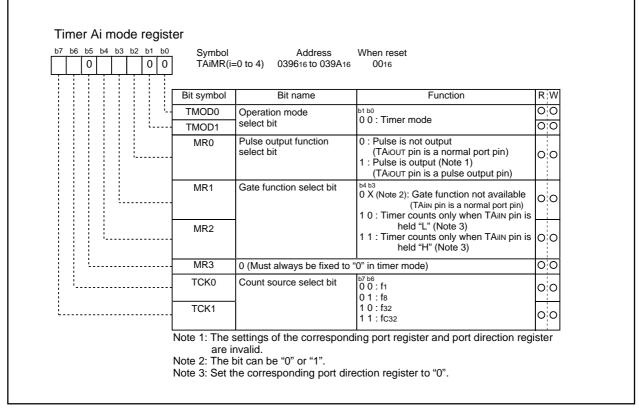

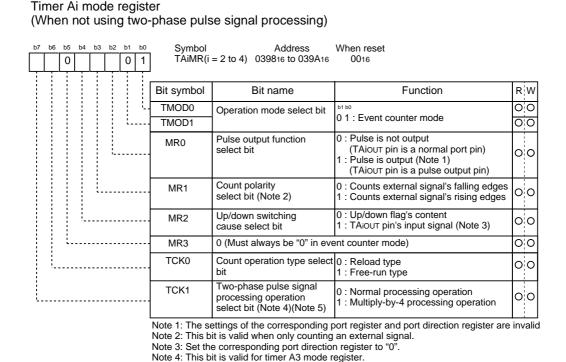

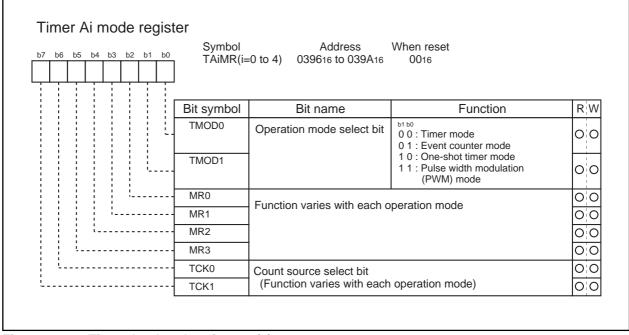

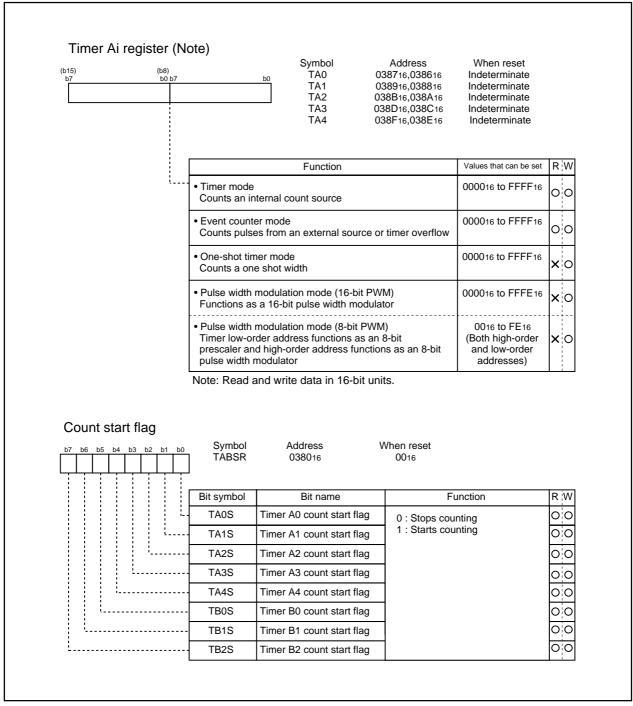

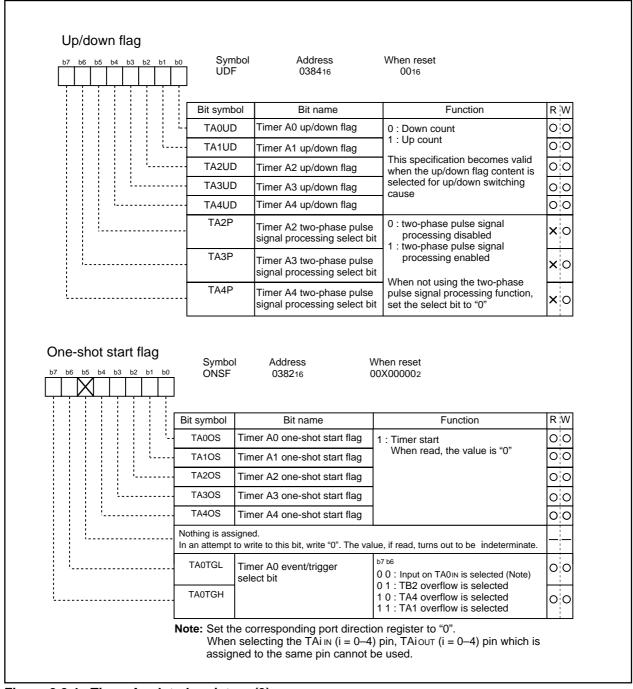

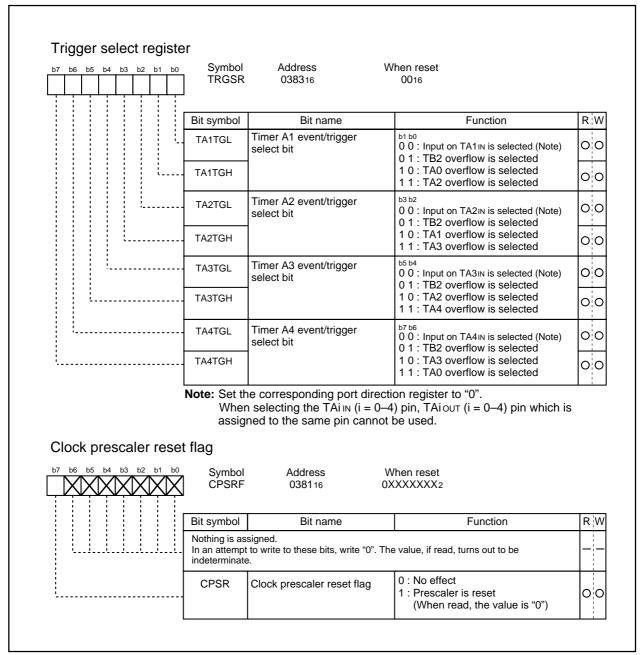

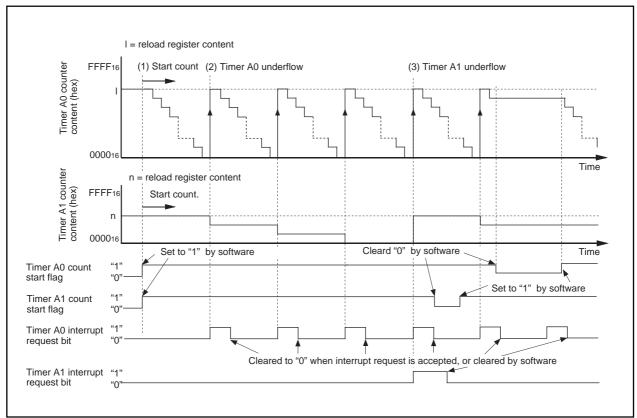

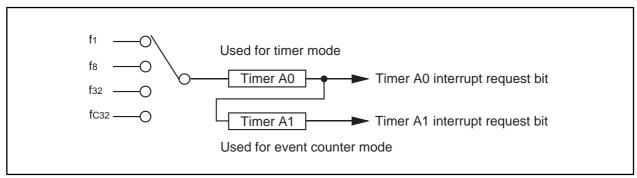

| Timer A                                                              | 72  |

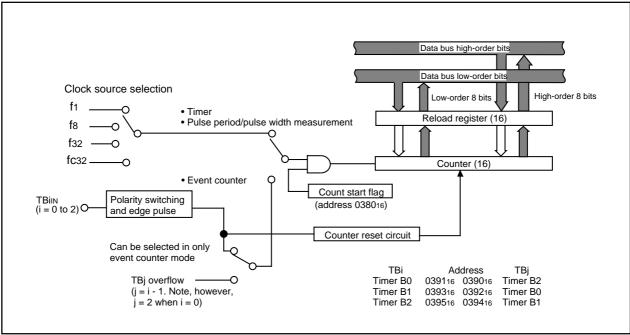

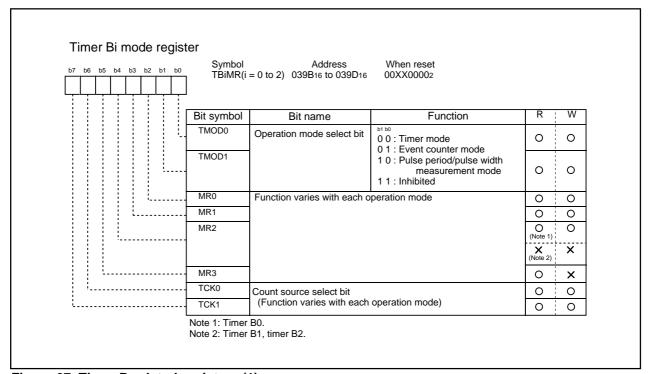

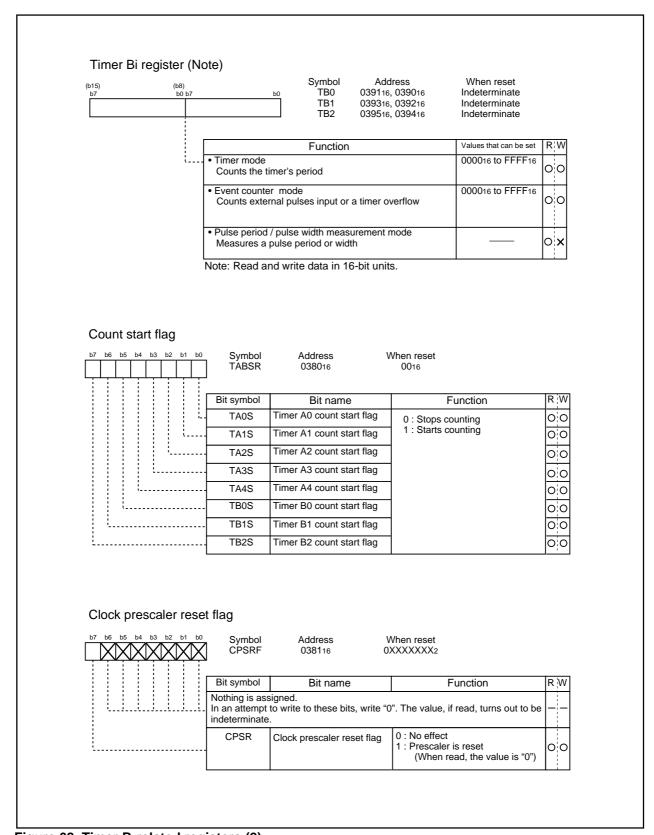

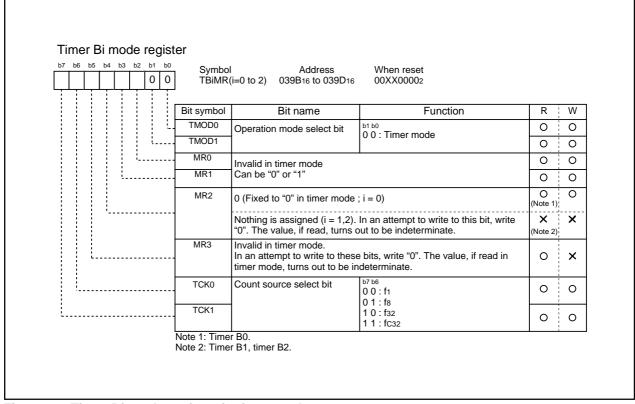

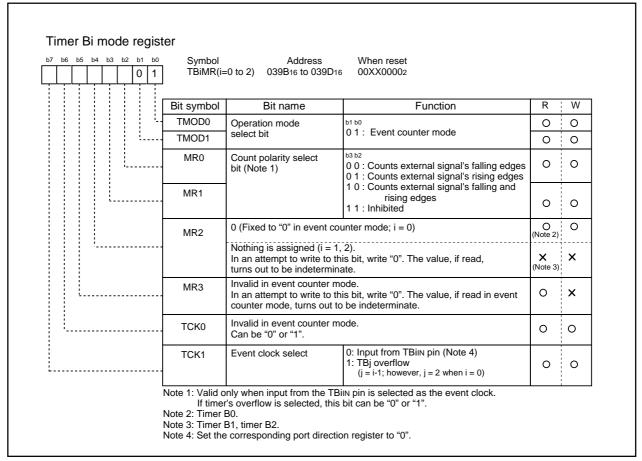

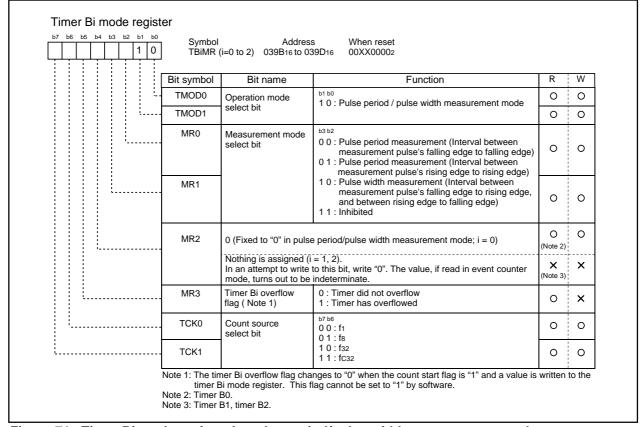

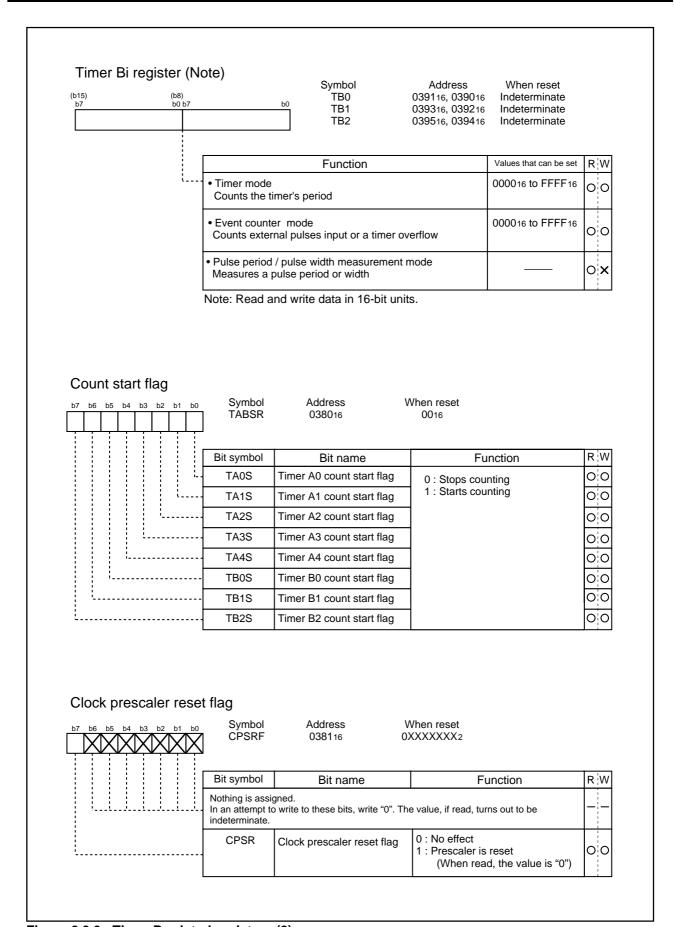

| Timer B                                                              | 82  |

| Serial I/O                                                           | 88  |

| Serial I/O2                                                          | 102 |

| A-D Converter                                                        | 115 |

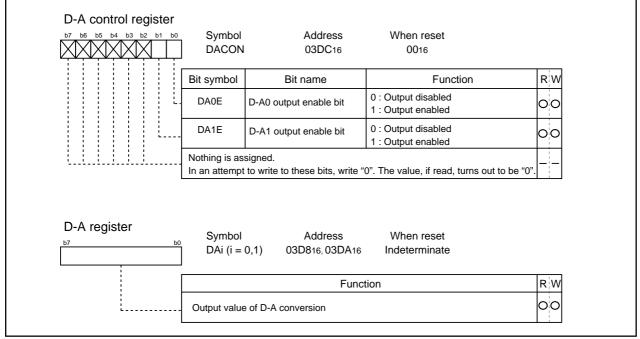

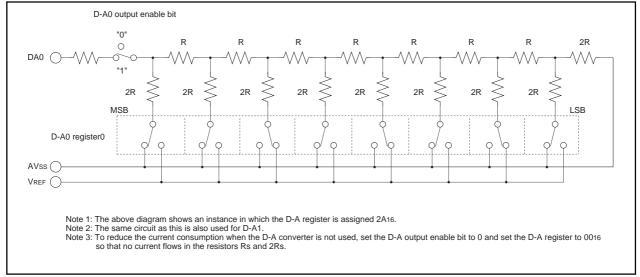

| D-A Converter                                                        | 125 |

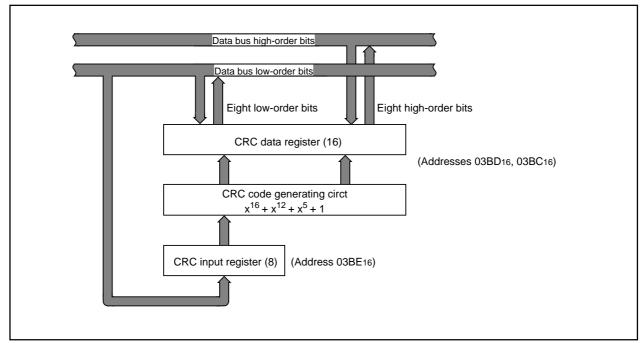

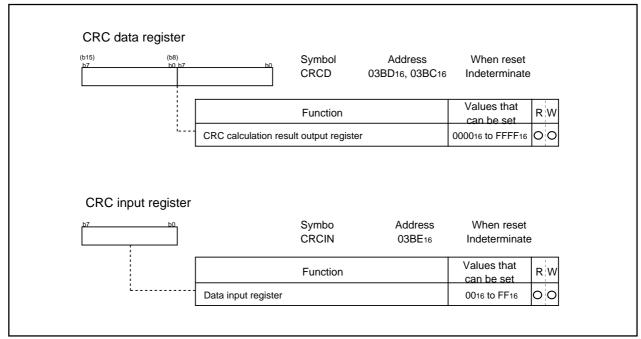

| CRC Calculation Circuit                                              | 127 |

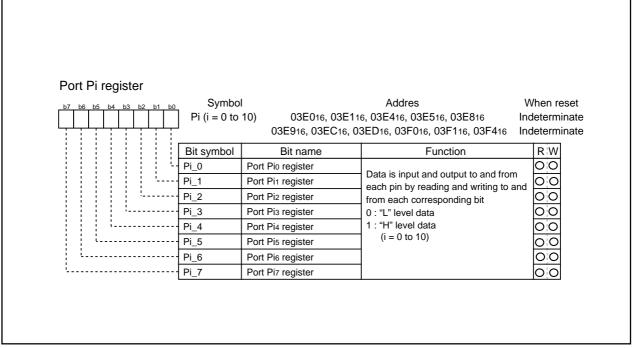

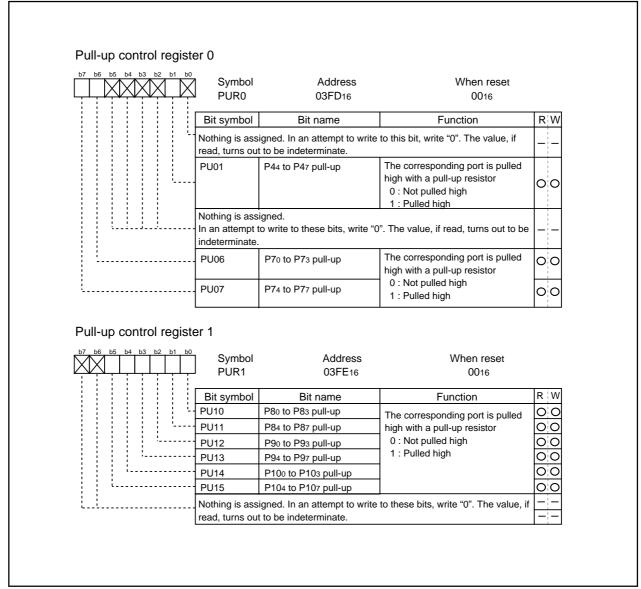

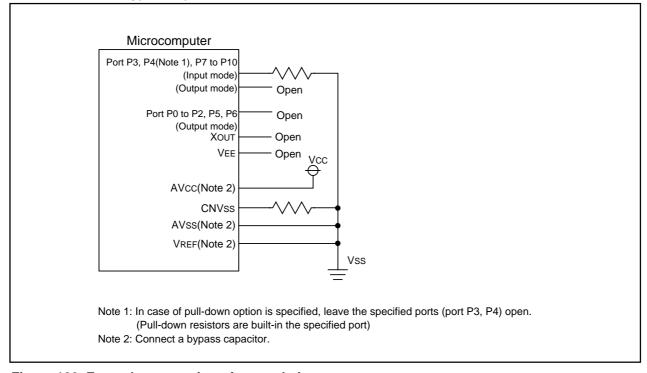

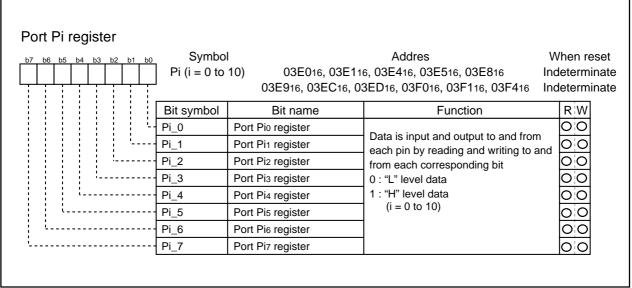

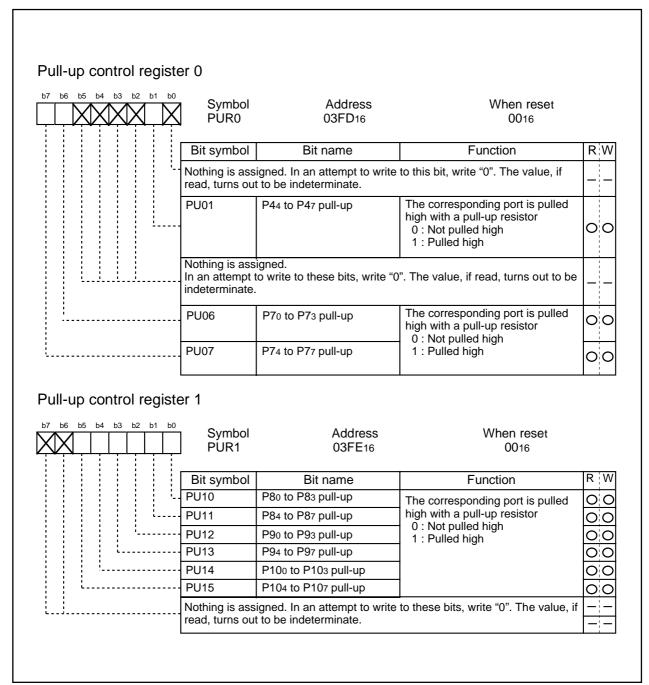

| Programmable I/O Ports                                               | 129 |

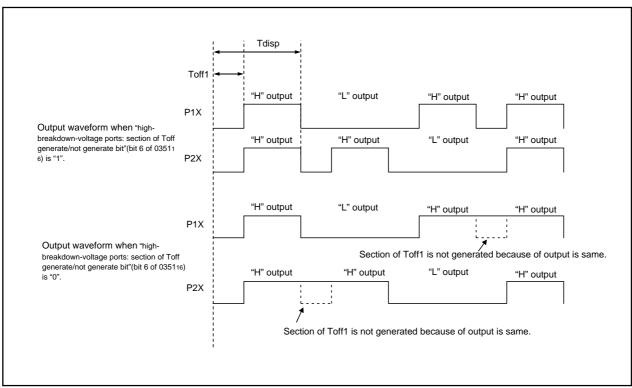

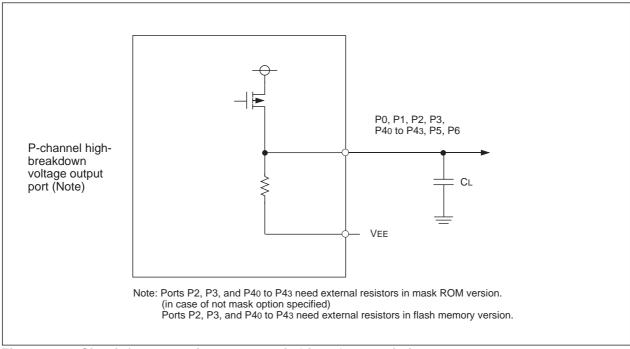

| Exclusive High-breakdown-voltage Output Ports                        | 129 |

| MASK OPTION OF PULL-DOWN RESISTOR (object product: mask ROM version) | 135 |

| EL LM                                                                | 4.5 |

## Chapter 2 Peripheral Functions Usage \_\_\_\_\_

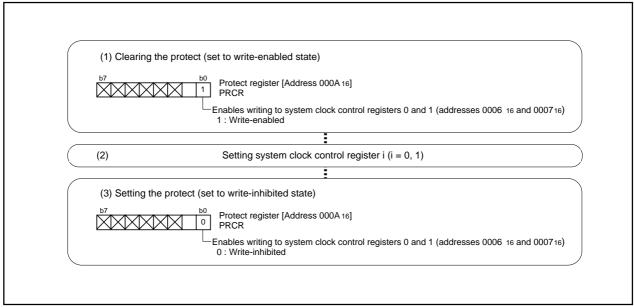

| 2 | .1 Protect                                                                                              | 178   |

|---|---------------------------------------------------------------------------------------------------------|-------|

|   | 2.1.1 Overview                                                                                          | 178   |

|   | 2.1.2 Protect Operation                                                                                 | 178   |

| 2 | .2 Timer A                                                                                              | 180   |

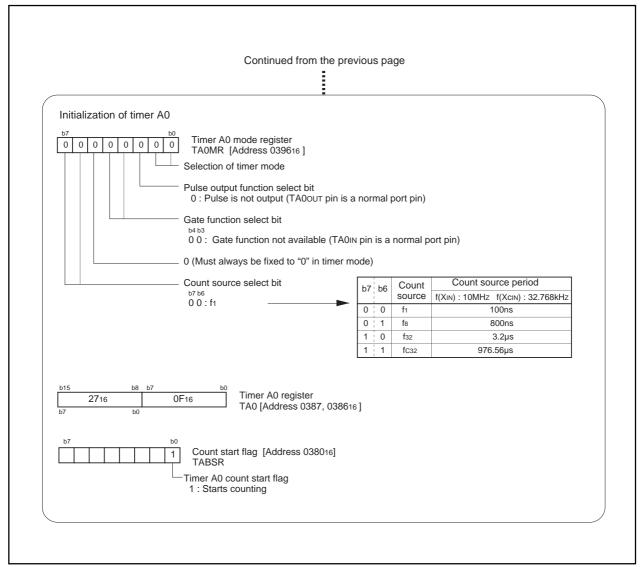

|   | 2.2.1 Overview                                                                                          | 180   |

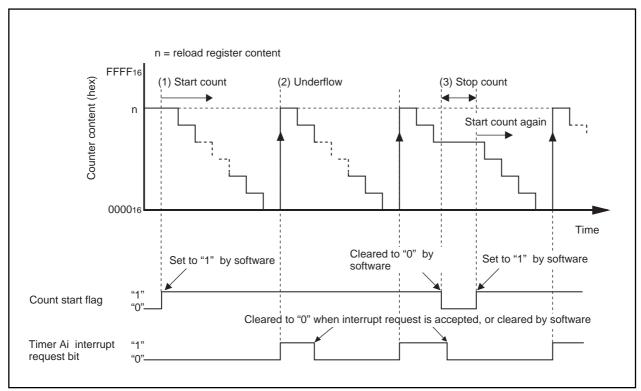

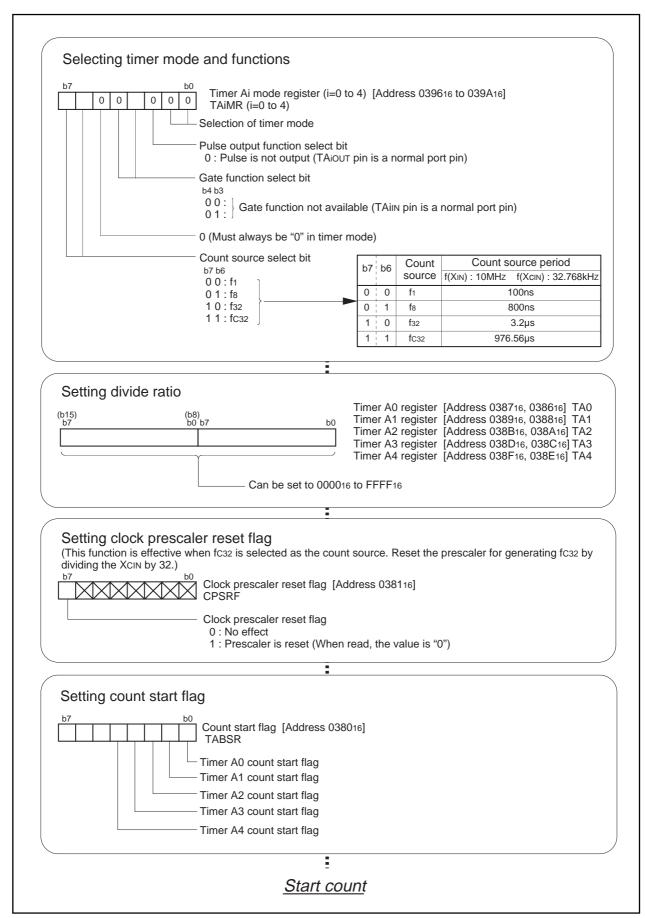

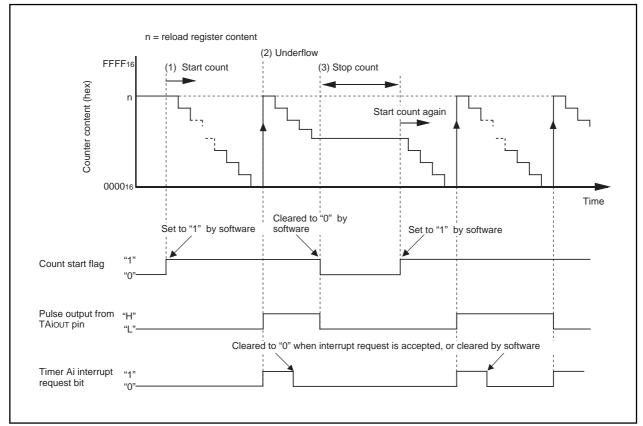

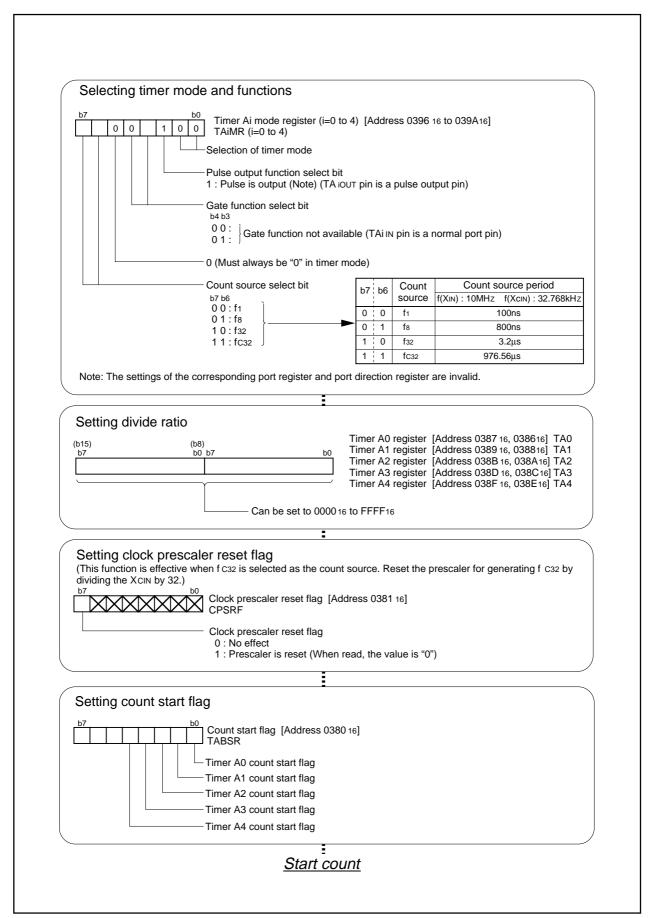

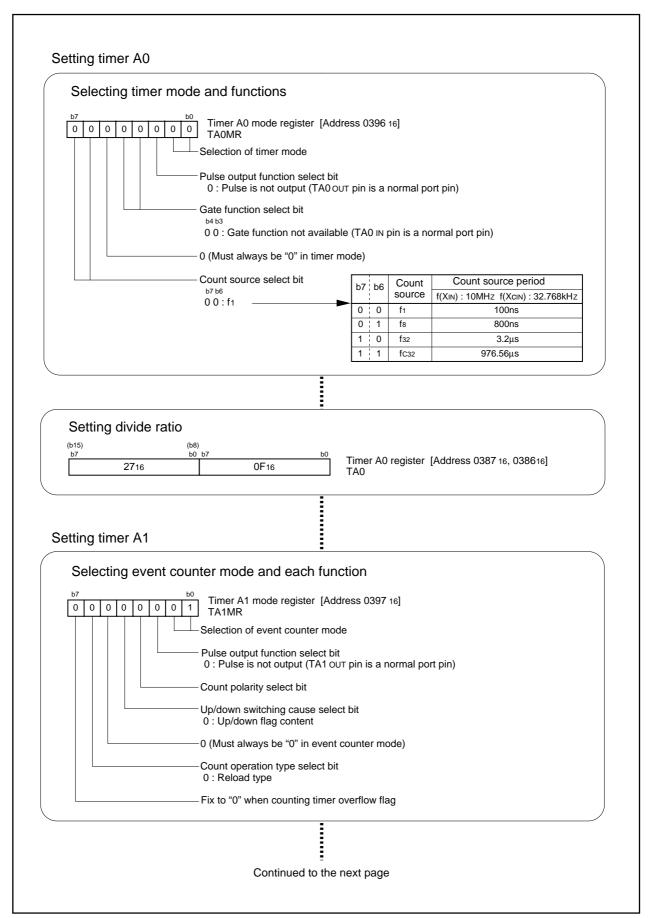

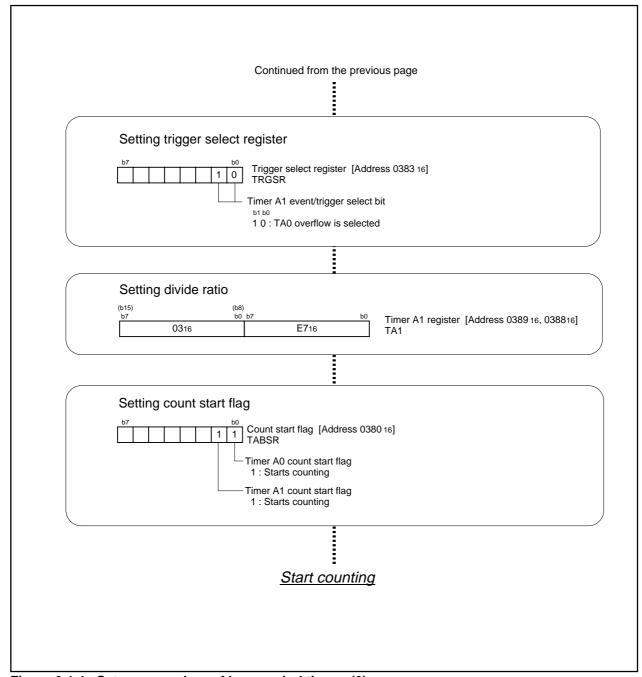

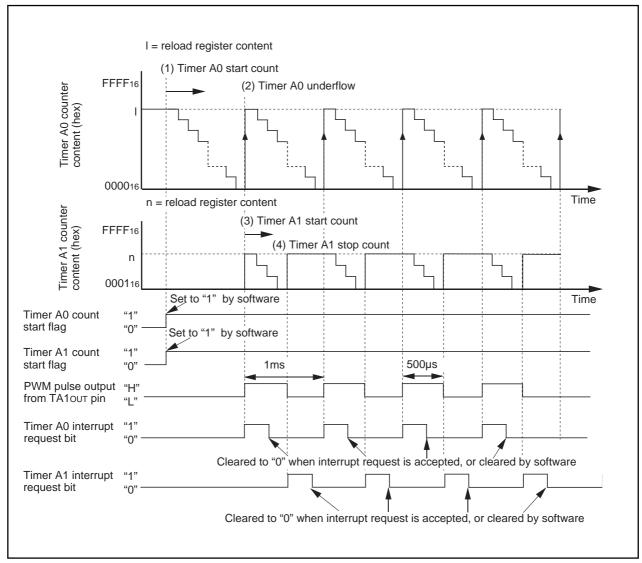

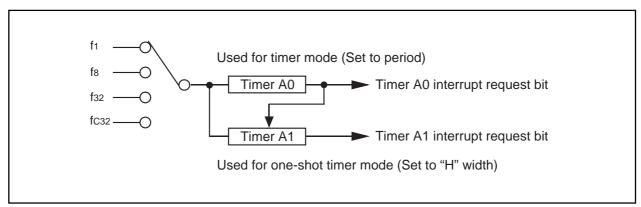

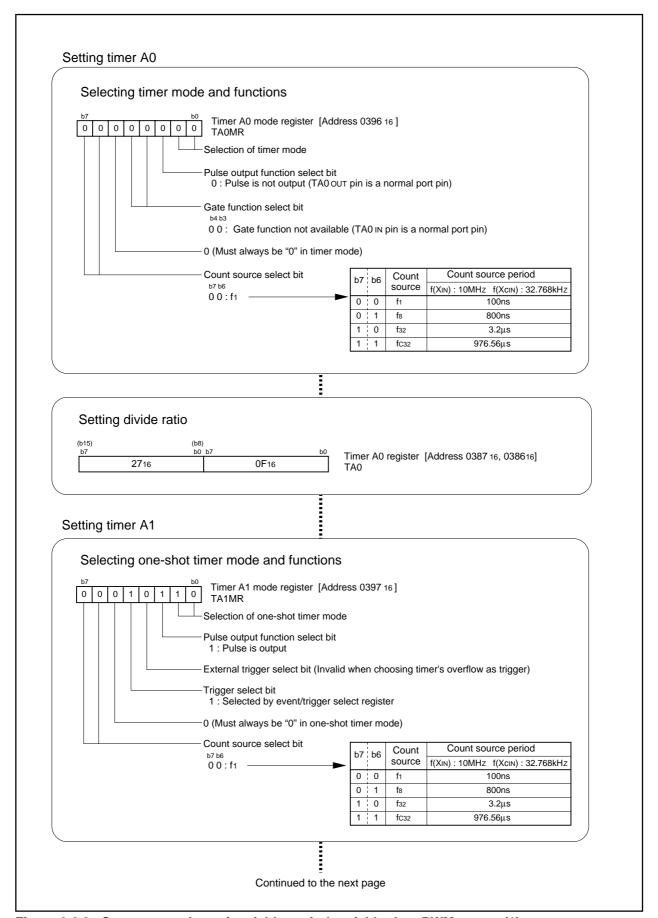

|   | 2.2.2 Operation of Timer A (timer mode)                                                                 | 186   |

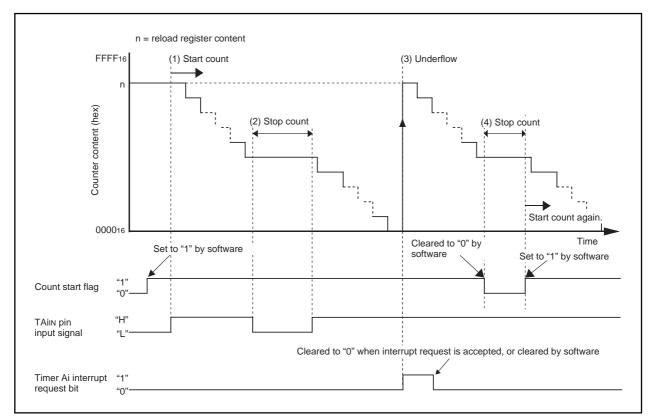

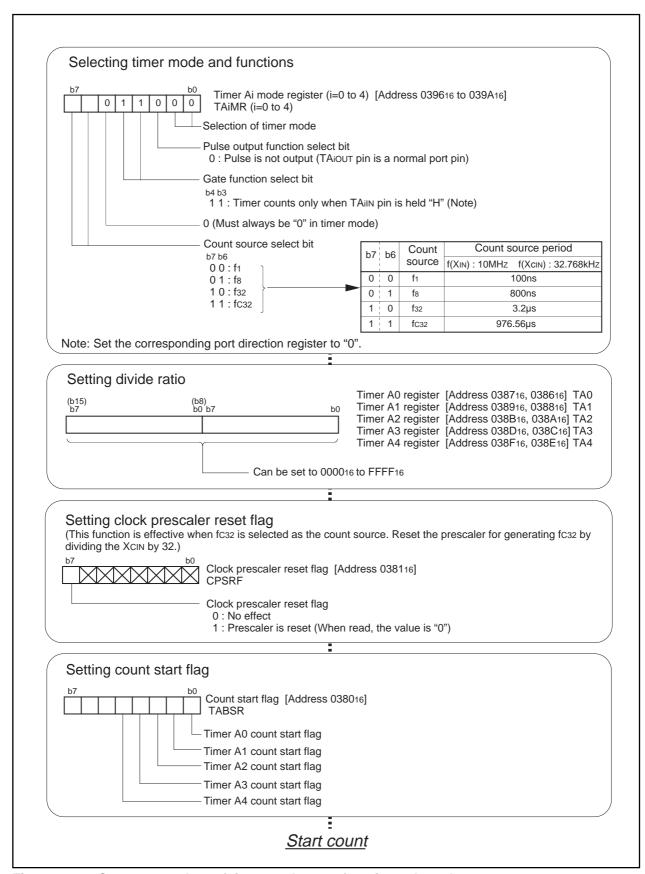

|   | 2.2.3 Operation of Timer A (timer mode, gate function selected)                                         | 188   |

|   | 2.2.4 Operation of Timer A (timer mode, pulse output function selected)                                 | 190   |

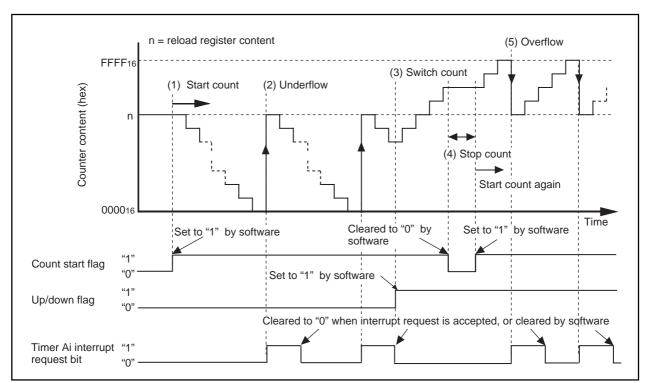

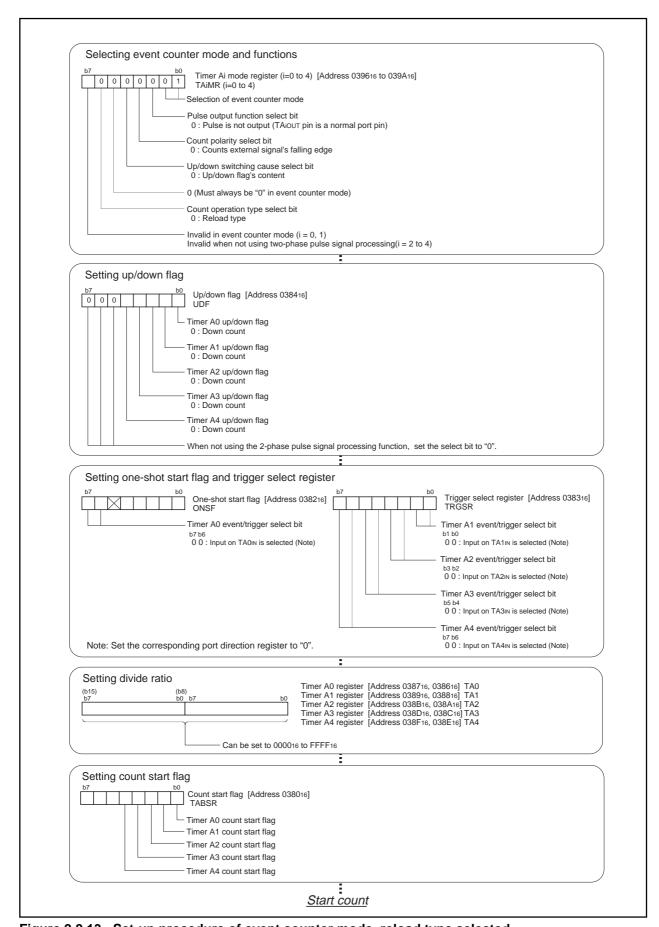

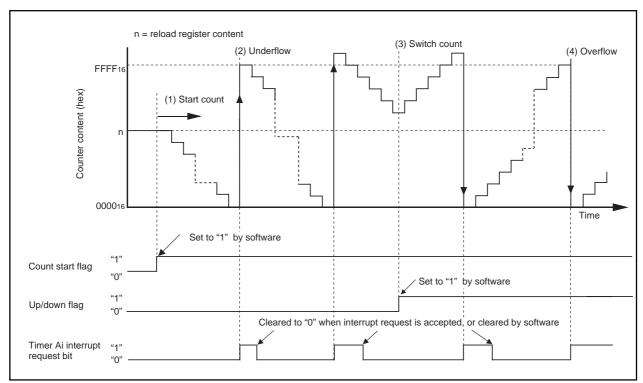

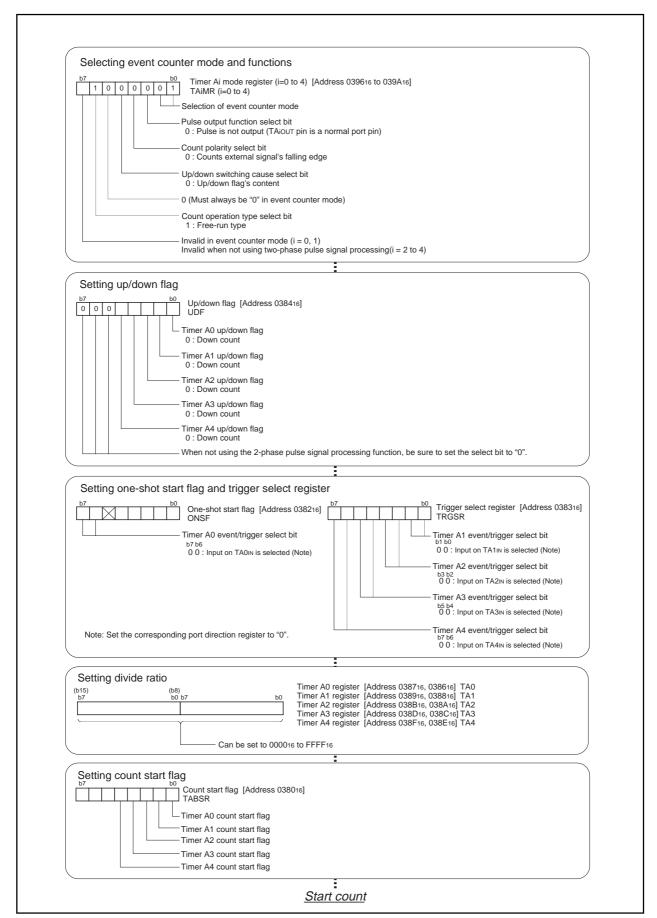

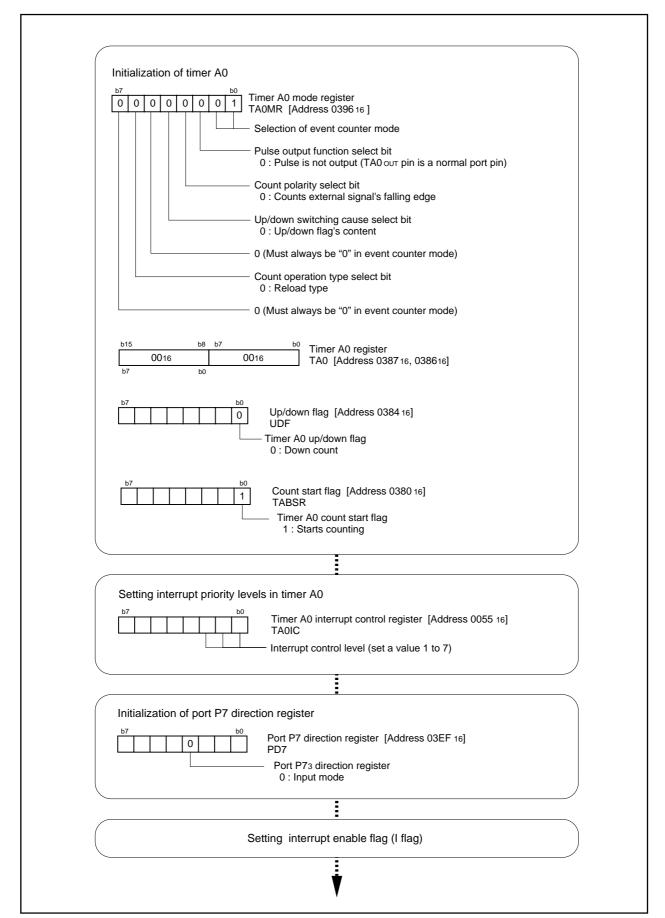

|   | 2.2.5 Operation of Timer A (event counter mode, reload type selected)                                   | 192   |

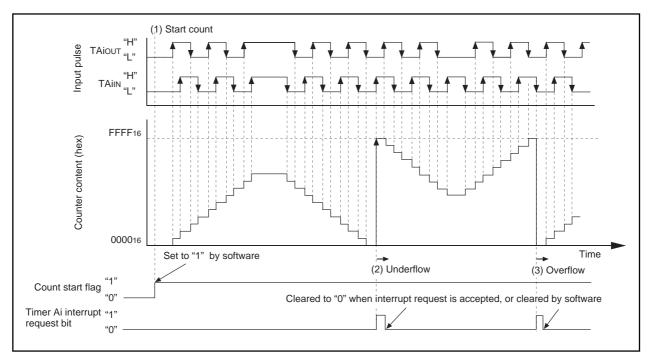

|   | 2.2.6 Operation of Timer A (event counter mode, free run type selected)                                 | 194   |

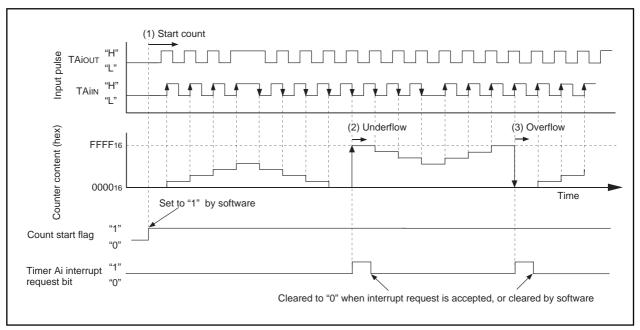

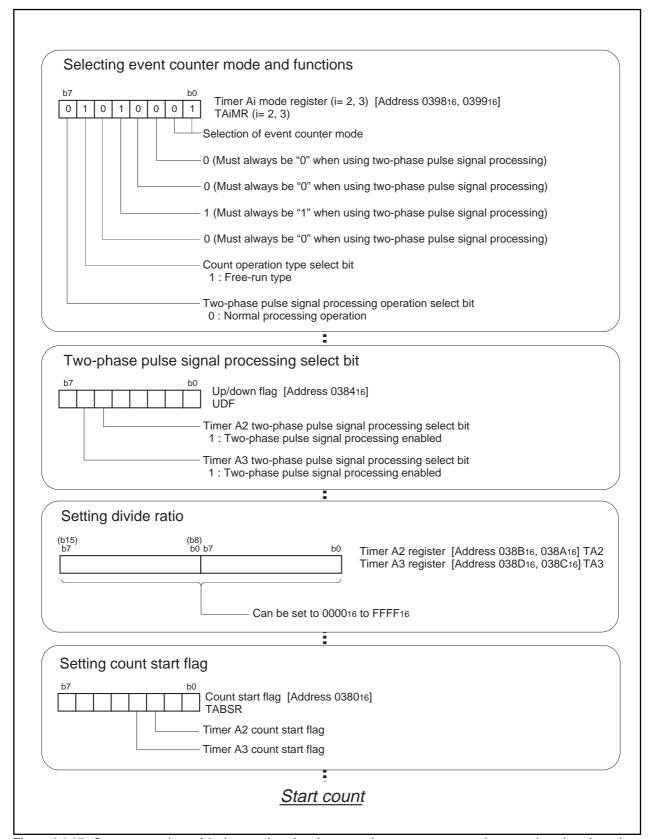

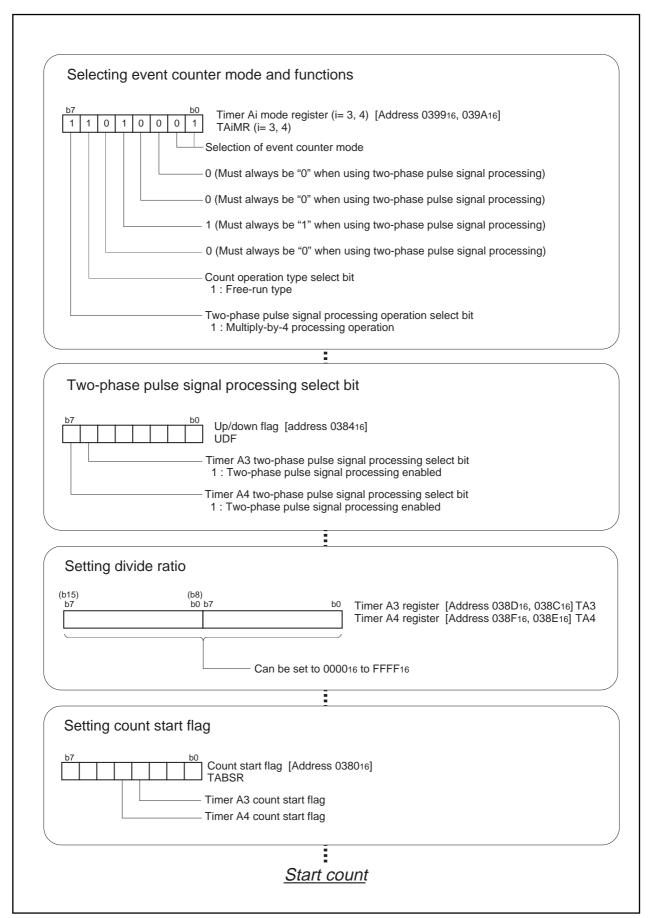

|   | 2.2.7 Operation of timer A (2-phase pulse signal process in event counter mode, normal modelected)      |       |

|   | 2.2.8 Operation of timer A (2-phase pulse signal process in event counter mode, multiply-by-4 selected) |       |

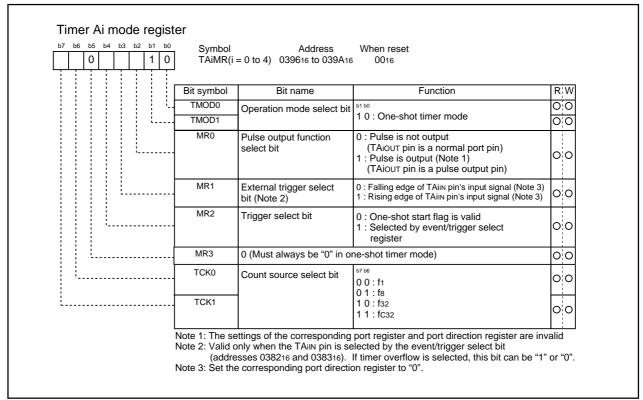

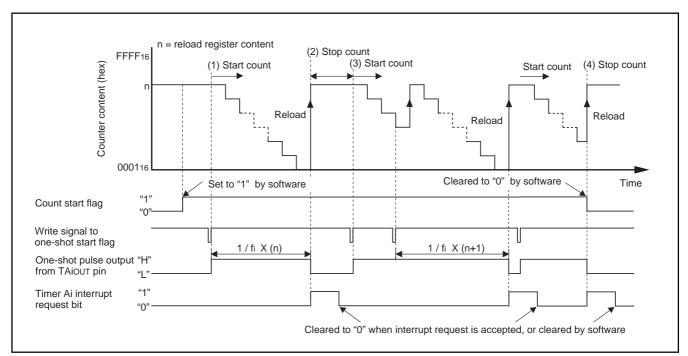

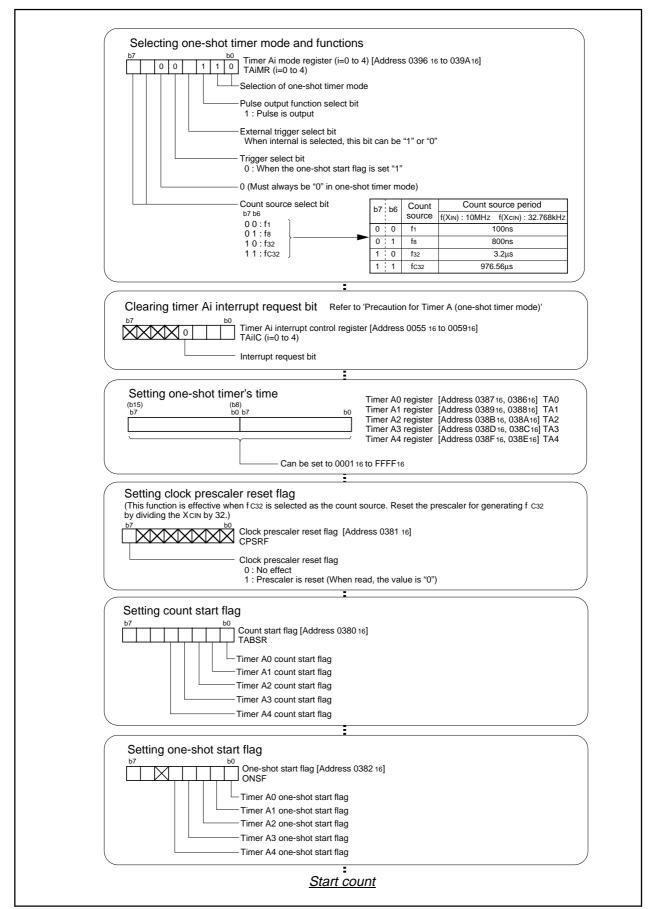

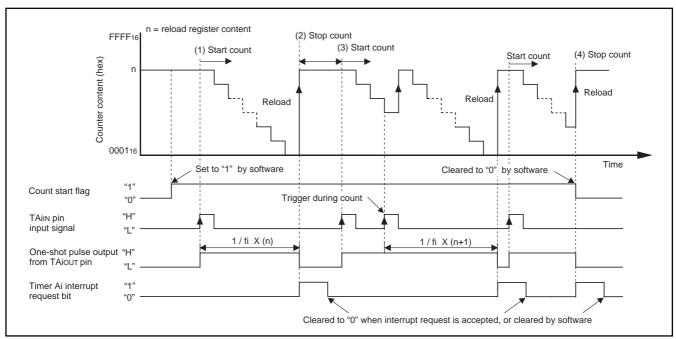

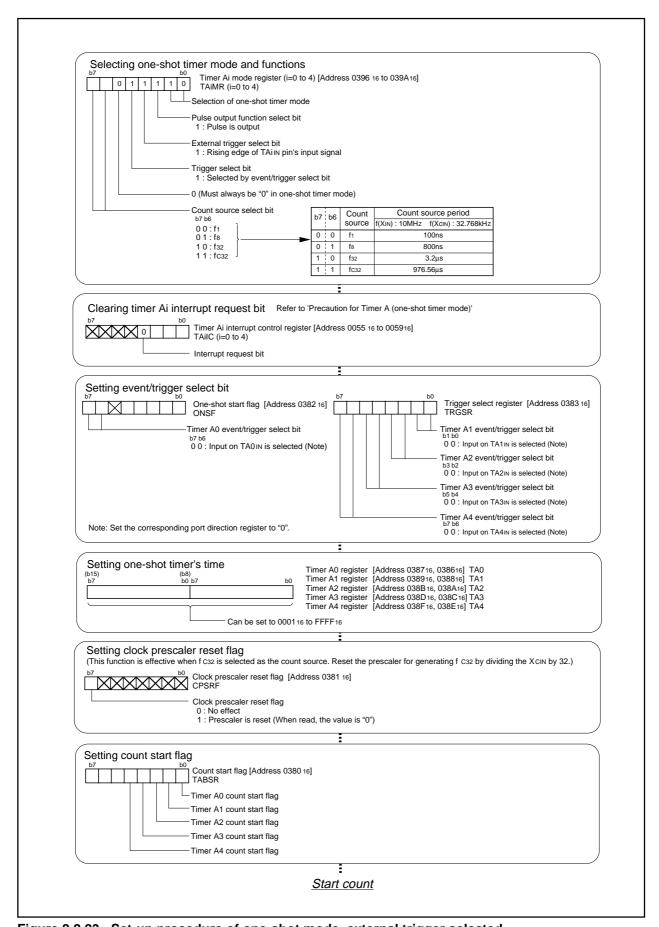

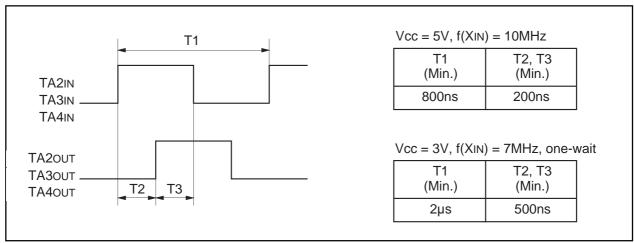

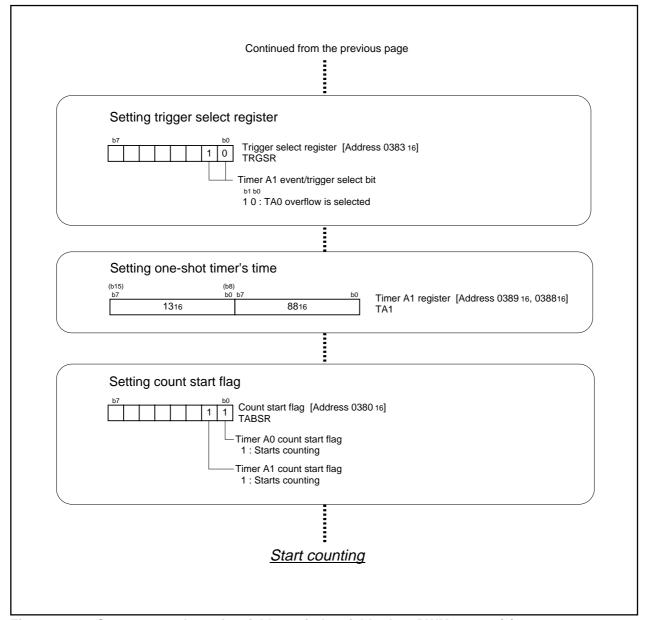

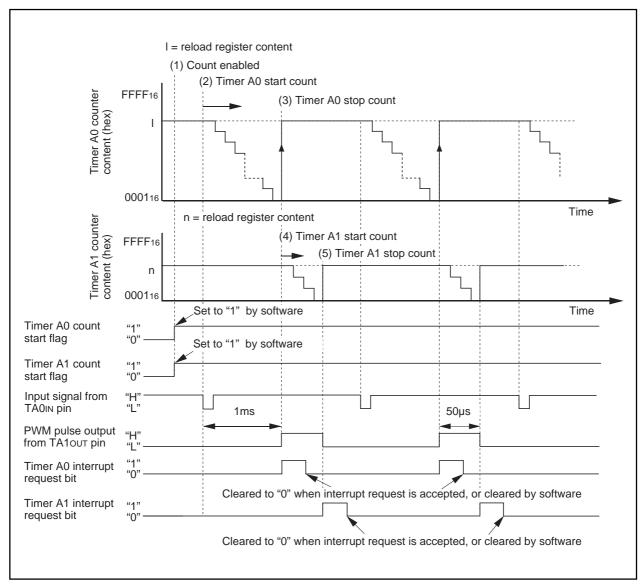

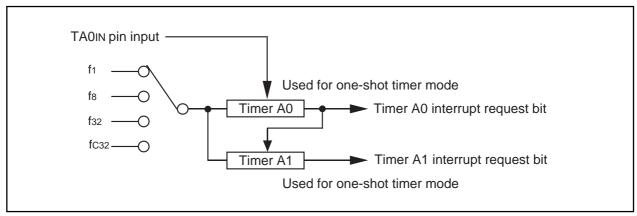

|   | 2.2.9 Operation of Timer A (one-shot timer mode)                                                        | 200   |

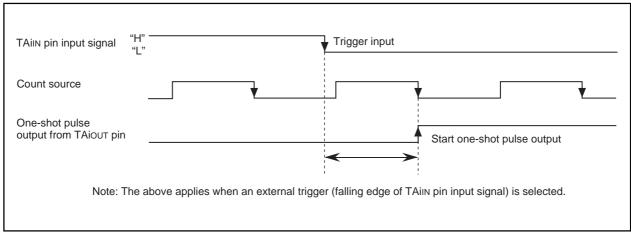

|   | 2.2.10 Operation of Timer A (one-shot timer mode, external trigger selected)                            | 202   |

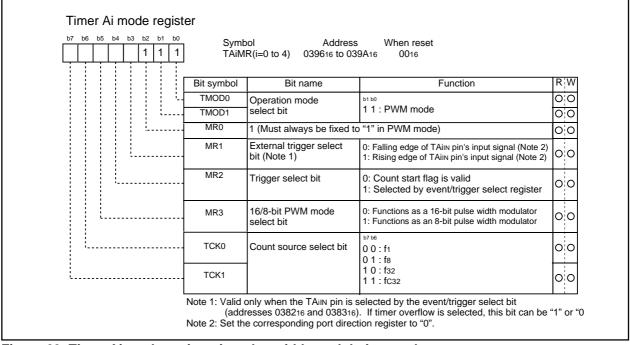

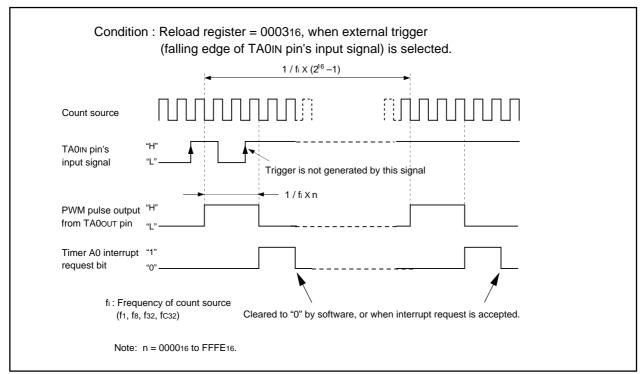

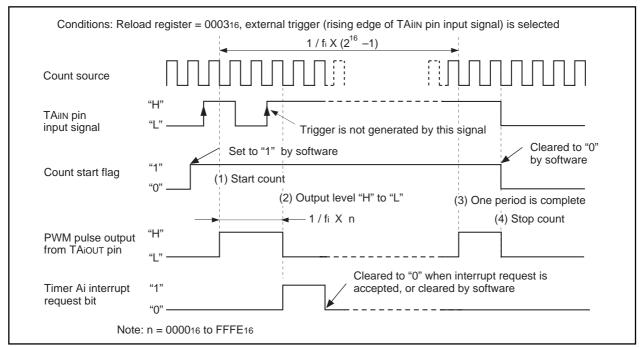

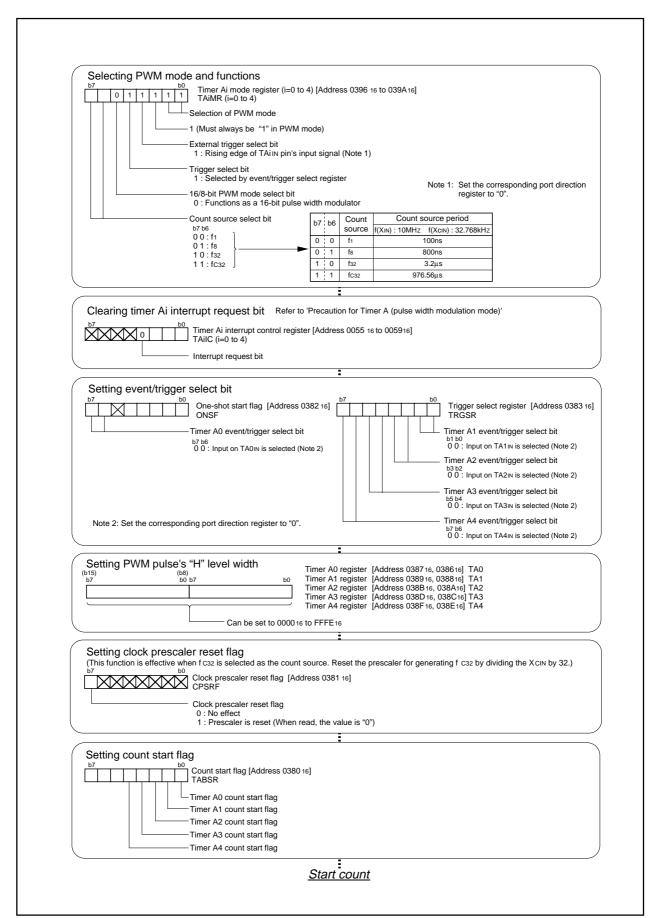

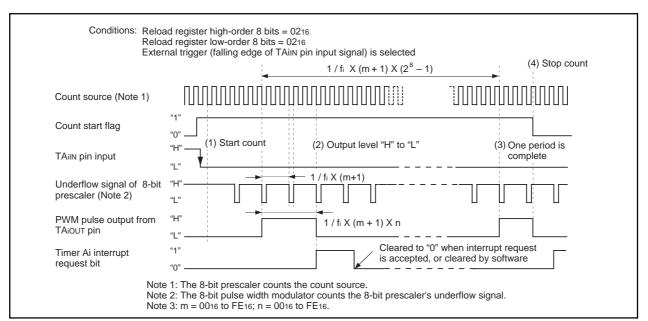

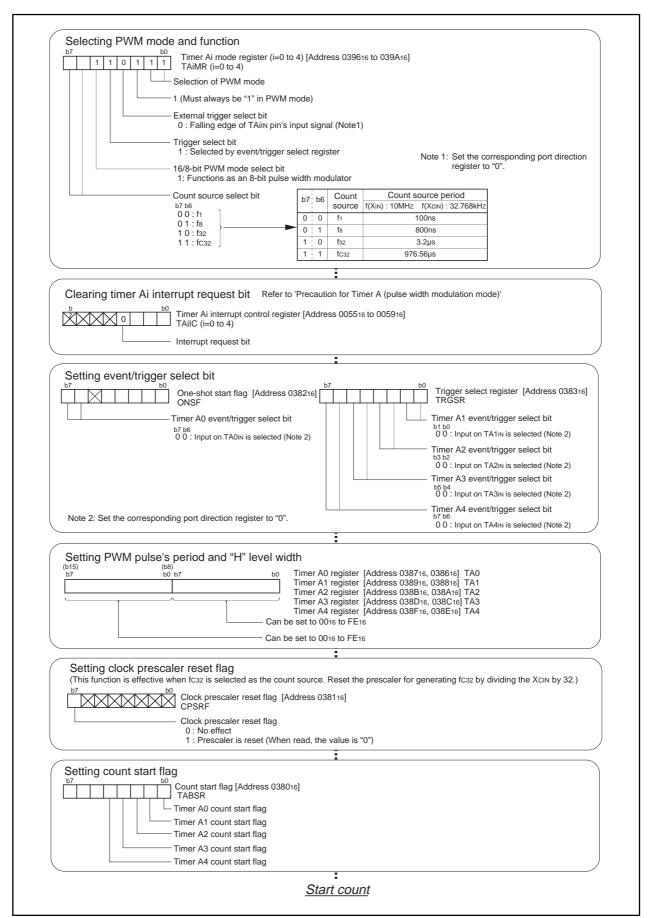

|   | 2.2.11 Operation of Timer A (pulse width modulation mode, 16-bit PWM mode selected)                     | 204   |

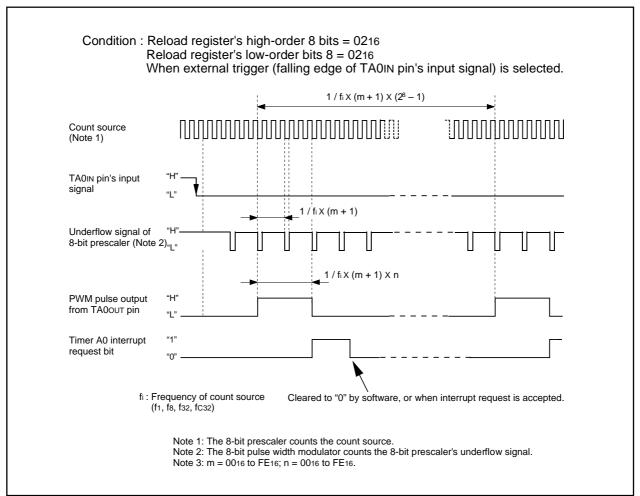

|   | 2.2.12 Operation of Timer A (pulse width modulation mode, 8-bit PWM mode selected)                      | 206   |

|   | 2.2.13 Precautions for Timer A (timer mode)                                                             | 208   |

|   | 2.2.14 Precautions for Timer A (event counter mode)                                                     | 209   |

|   | 2.2.15 Precautions for Timer A (one-shot timer mode)                                                    | 210   |

|   | 2.2.16 Precautions for Timer A (pulse width modulation mode)                                            | 211   |

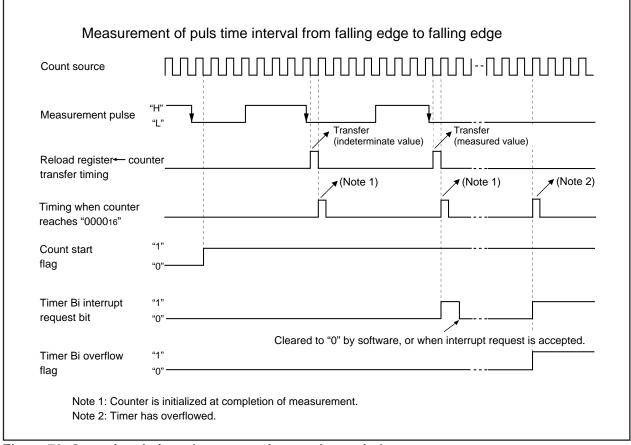

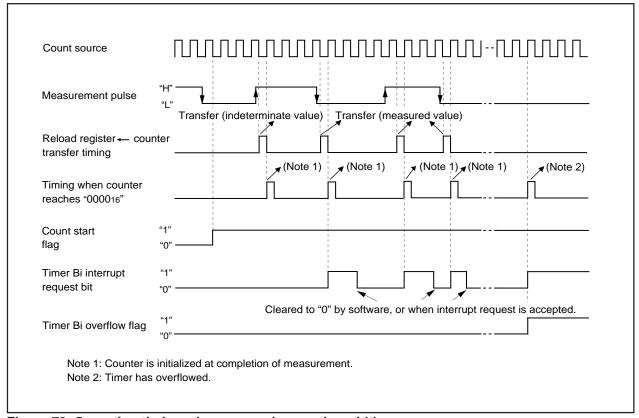

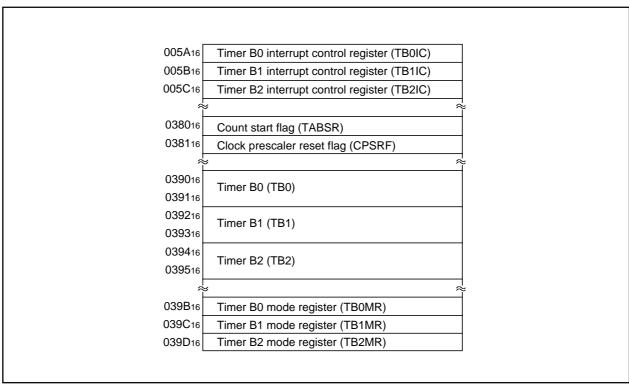

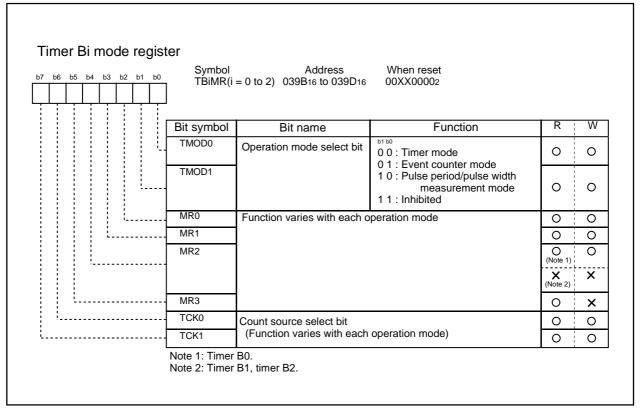

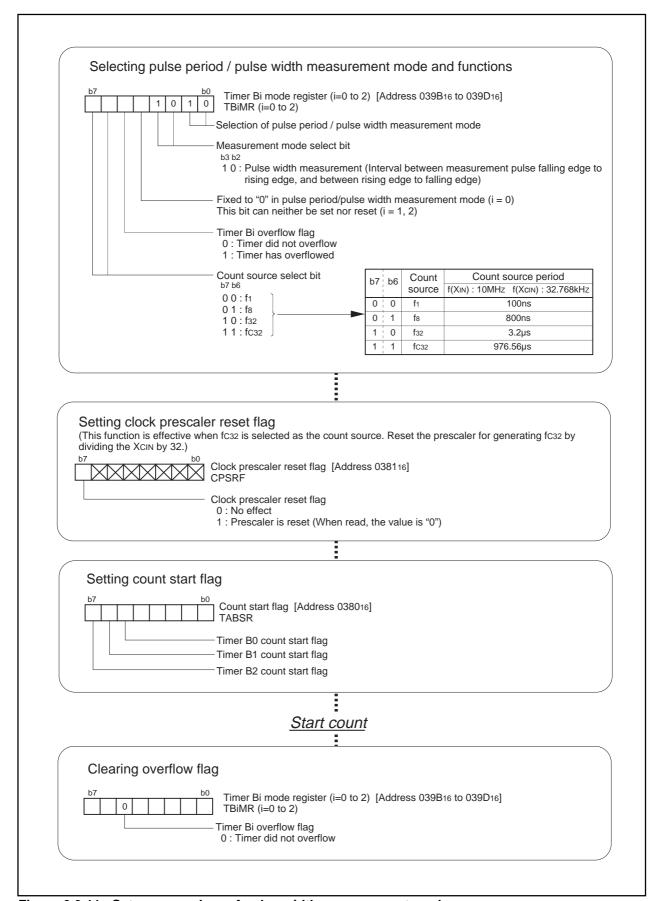

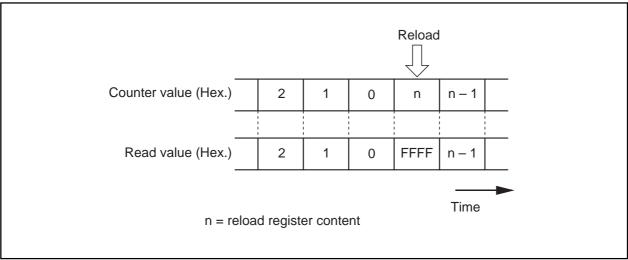

| 2 | .3 Timer B                                                                                              | 212   |

|   | 2.3.1 Overview                                                                                          | 212   |

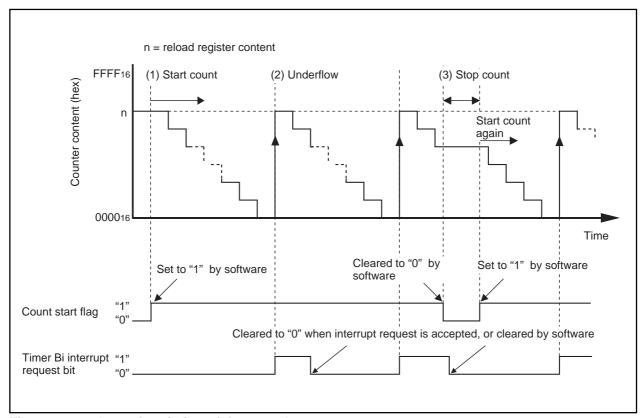

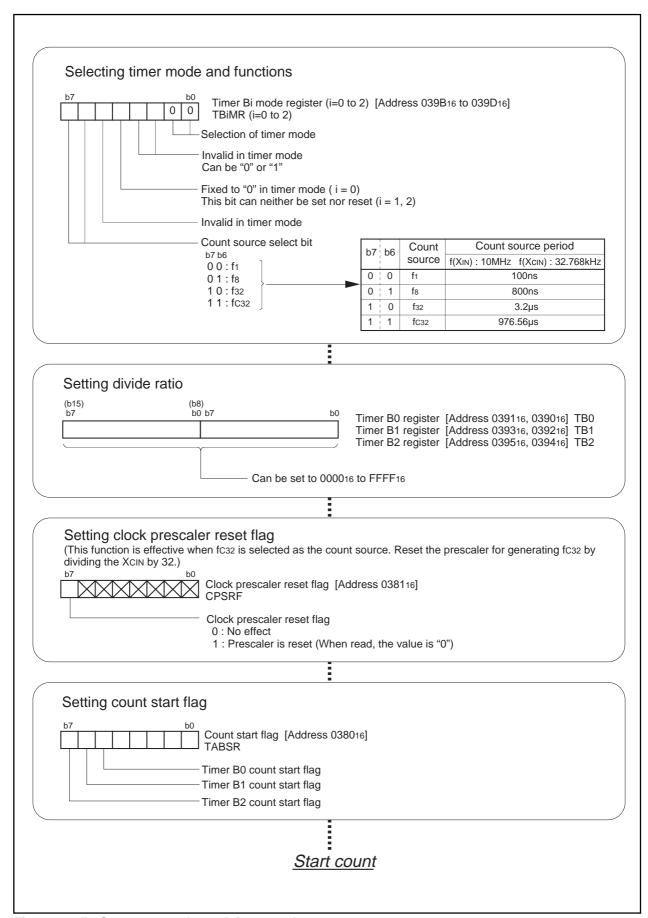

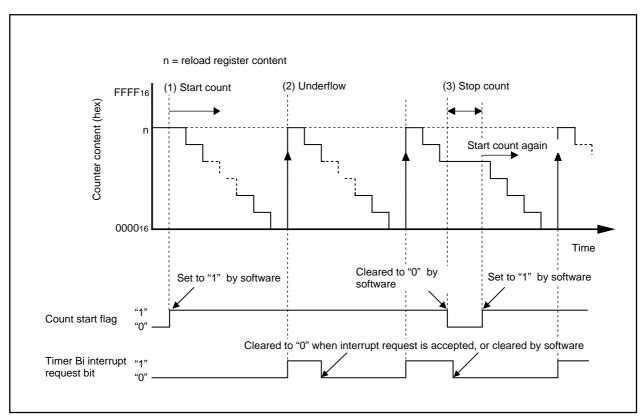

|   | 2.3.2 Operation of Timer B (timer mode)                                                                 | 216   |

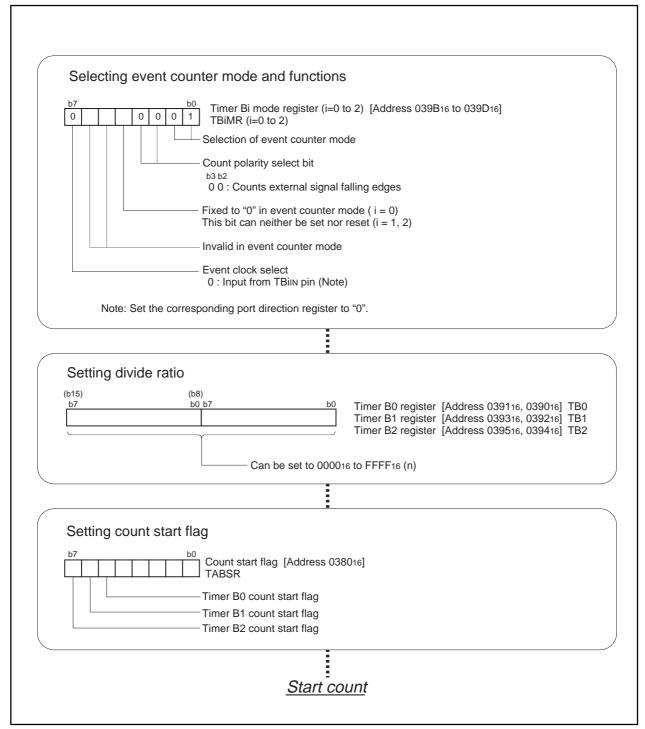

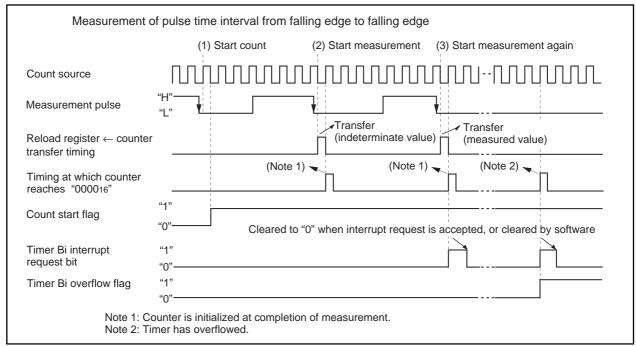

|   | 2.3.3 Operation of Timer B (event counter mode)                                                         | 218   |

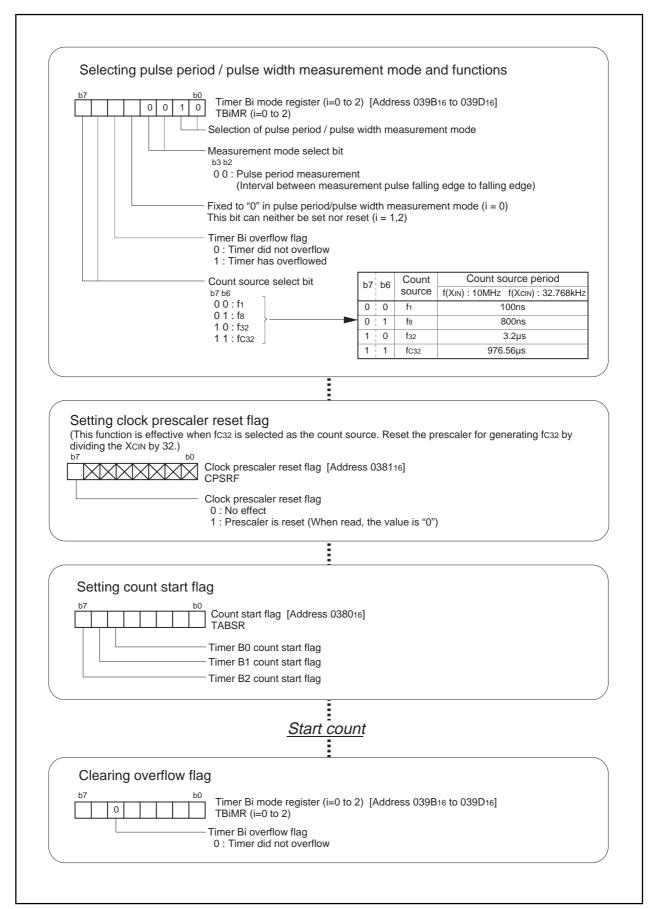

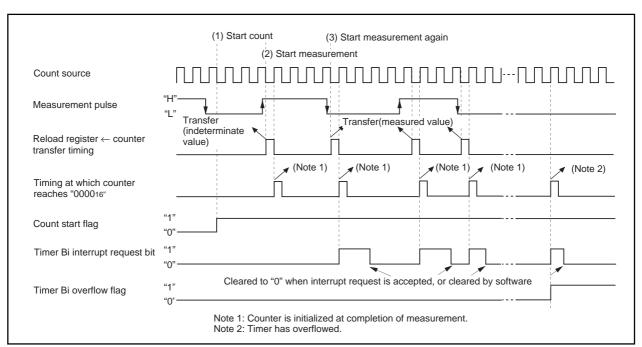

|   | 2.3.4 Operation of Timer B (pulse period measurement mode)                                              | 220   |

|   | 2.3.5 Operation of Timer B (pulse width measurement mode)                                               | 222   |

|   | 2.3.6 Precautions for Timer B (timer mode, event counter mode)                                          | 224   |

|   | 2.3.7 Precautions for Timer B (pulse period/pulse width measurement mode)                               | 225   |

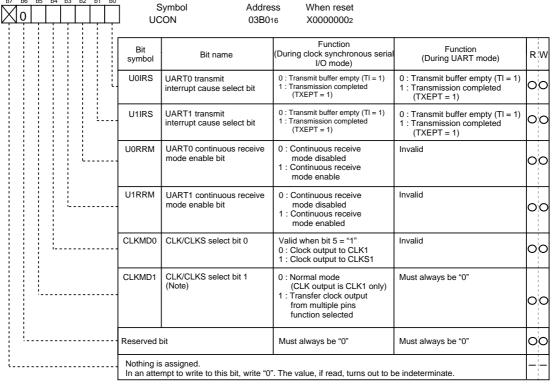

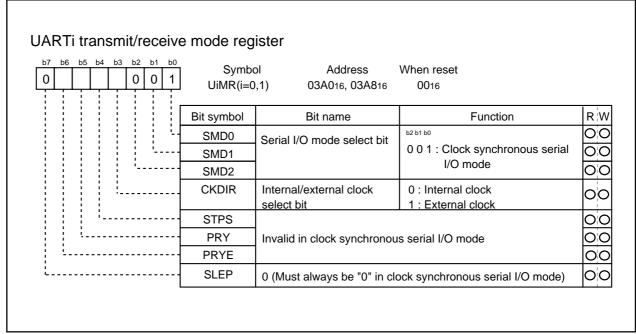

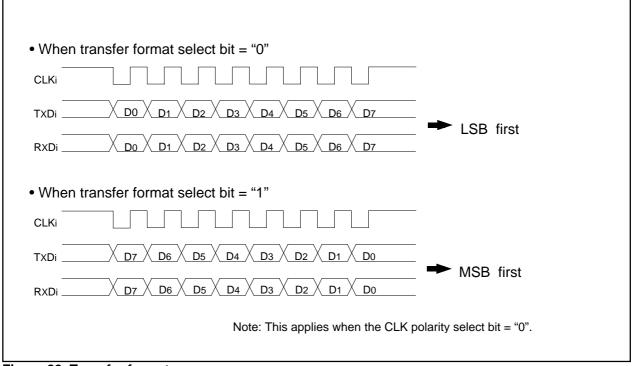

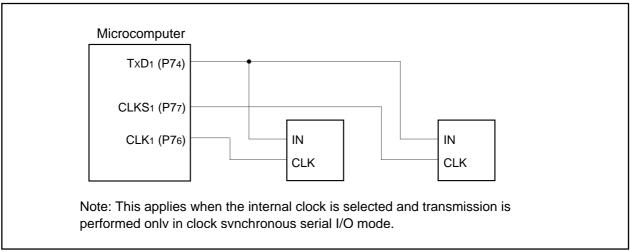

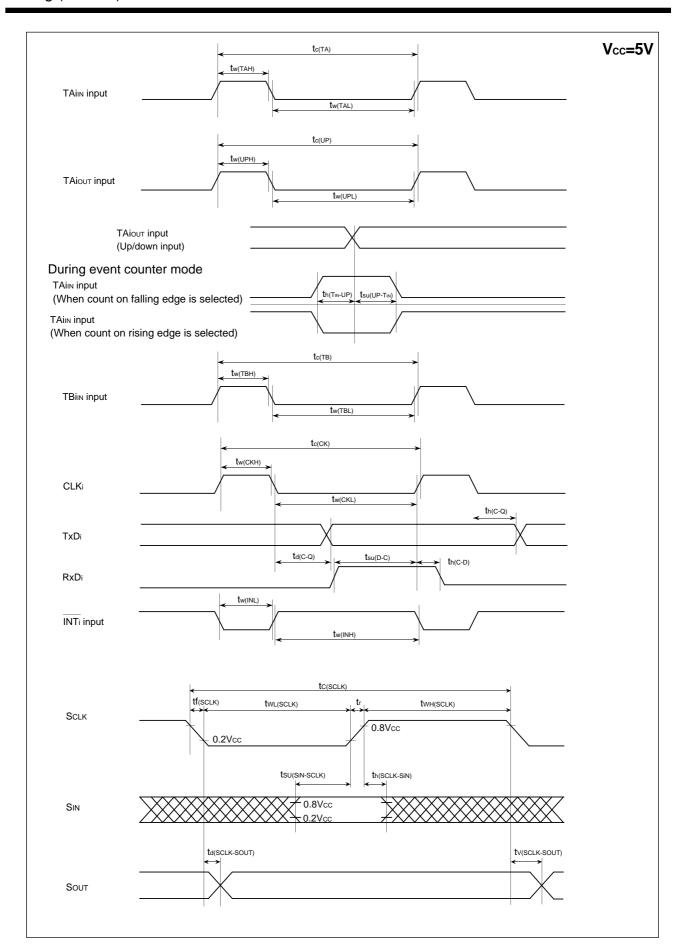

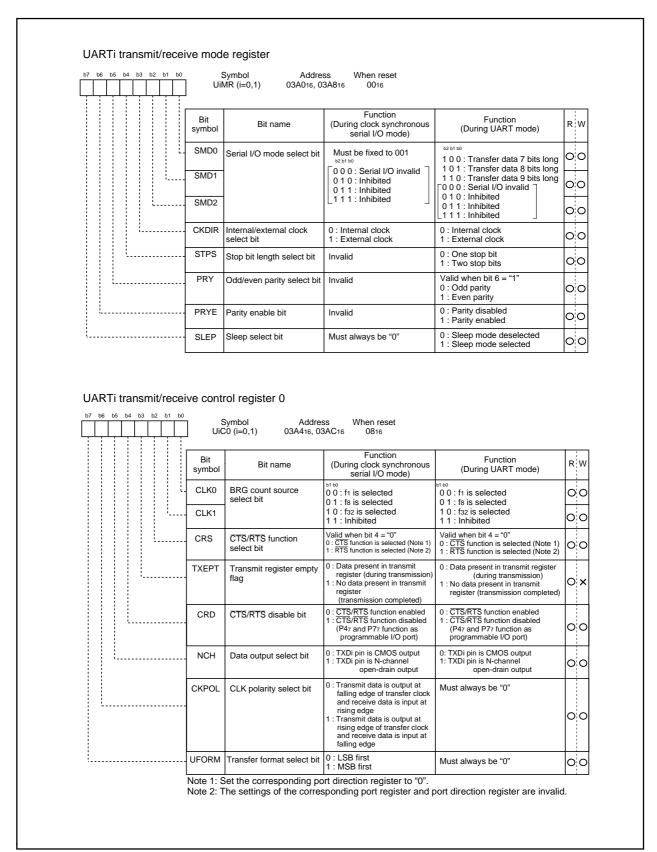

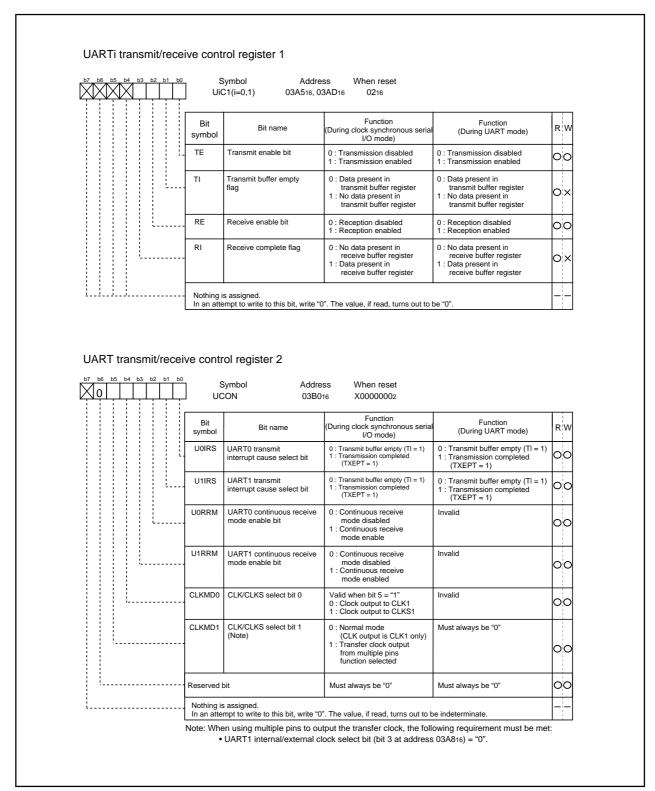

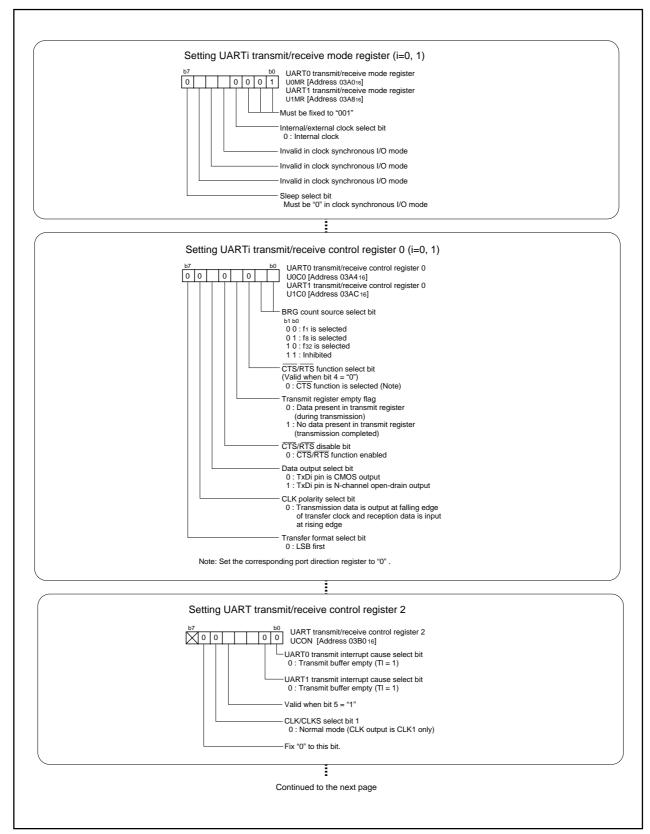

| 2 | .4 Clock-Synchronous Serial I/O                                                                         | 226   |

|   | 2.4.1 Overview                                                                                          | 226   |

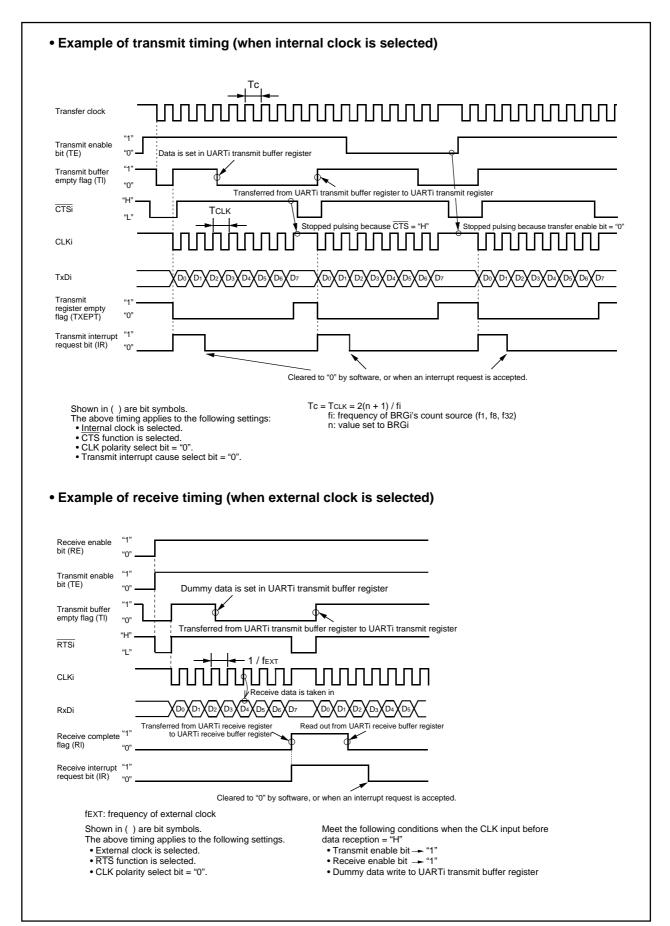

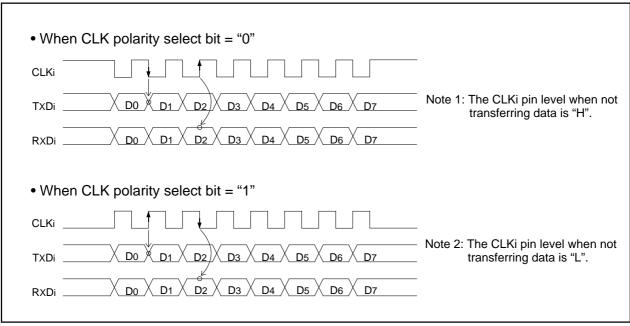

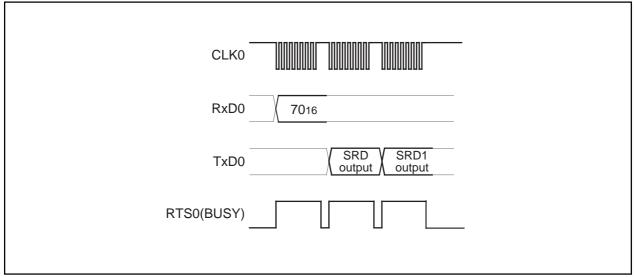

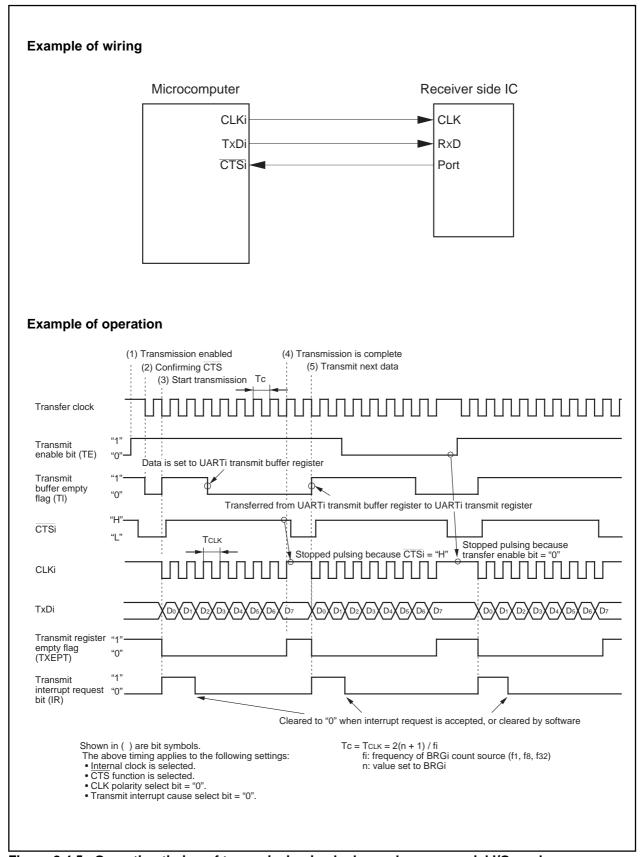

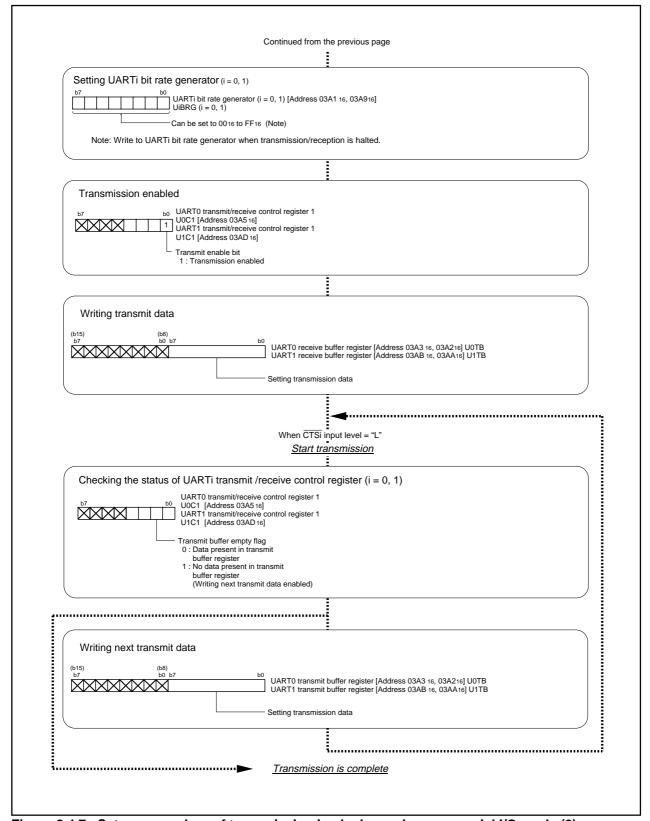

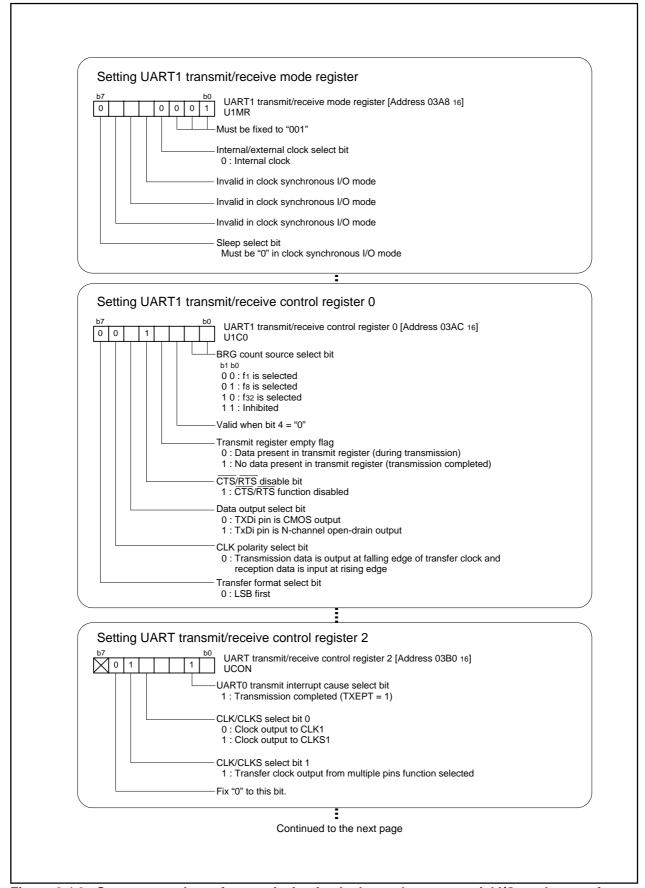

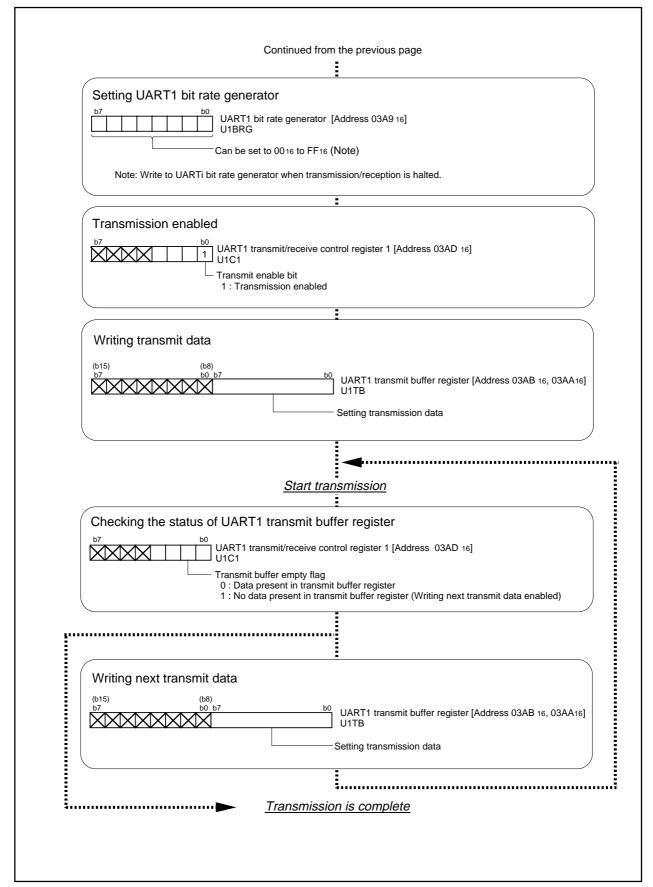

|   | 2.4.2 Operation of Serial I/O (transmission in clock-synchronous serial I/O mode)                       | 232   |

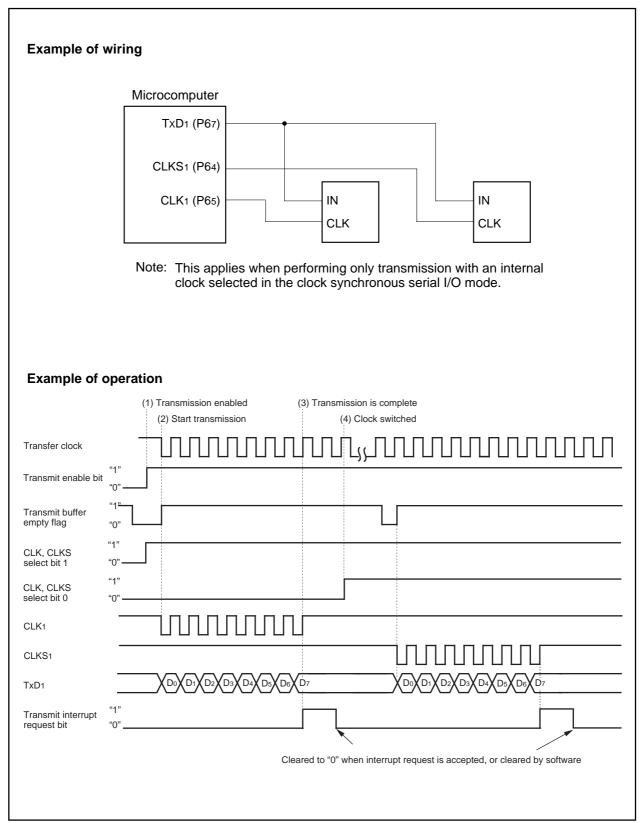

|   | 2.4.3 Operation of the Serial I/O (transmission in clock-synchronous serial I/O mode, transfer          | clock |

| output from multiple pins function selected)                                                            | 236       |

|---------------------------------------------------------------------------------------------------------|-----------|

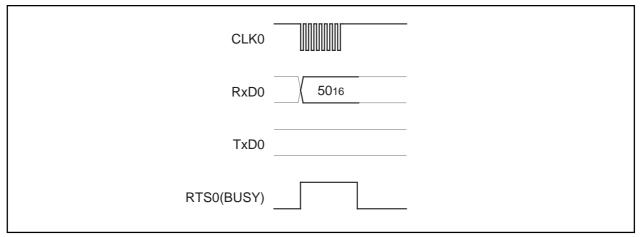

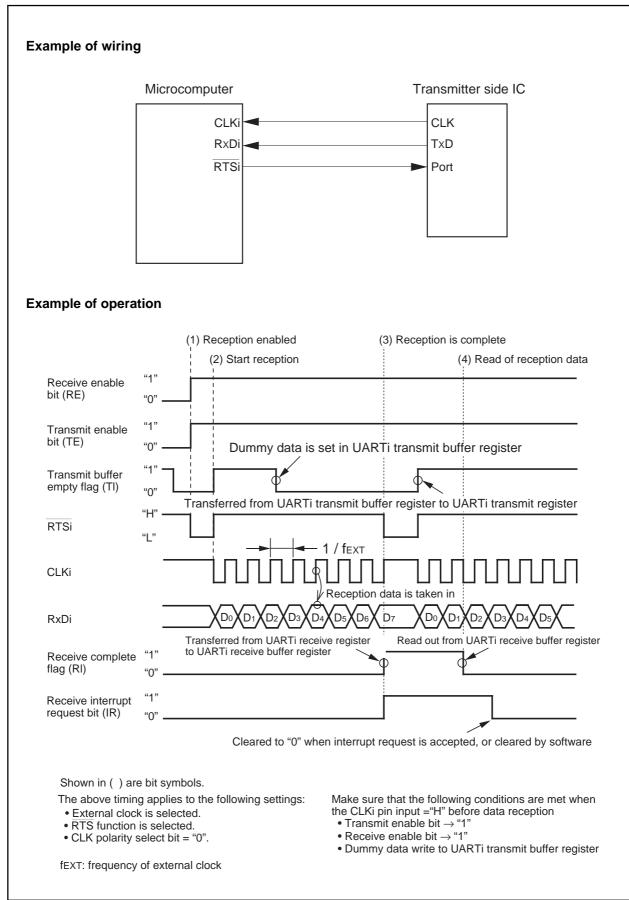

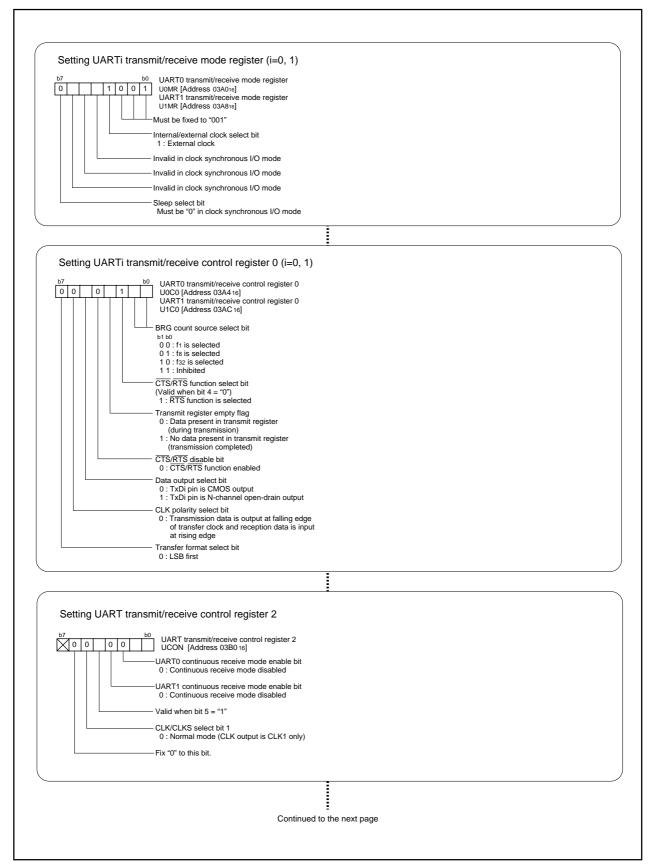

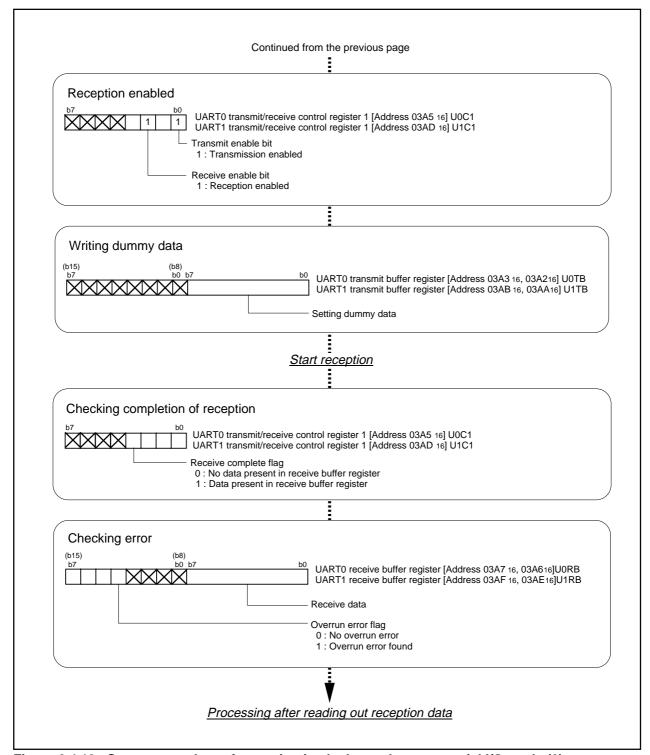

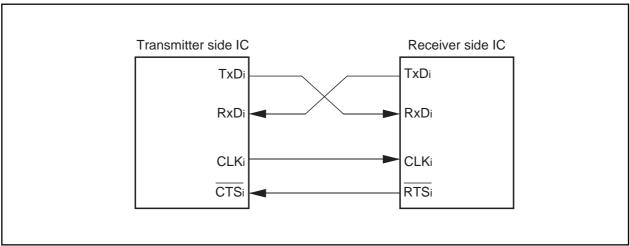

| 2.4.4 Operation of Serial I/O (reception in clock-synchronous serial I/O mode)                          | 240       |

| 2.4.5 Precautions for Serial I/O (in clock-synchronous serial I/O)                                      | 244       |

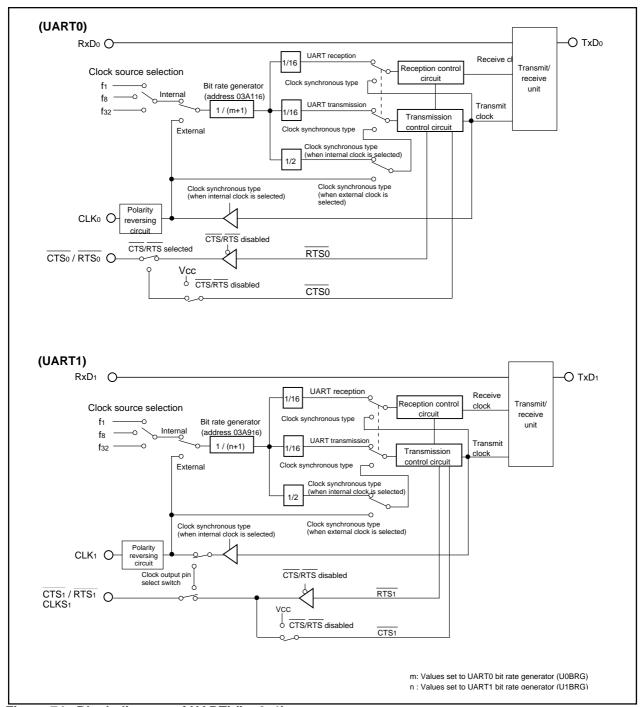

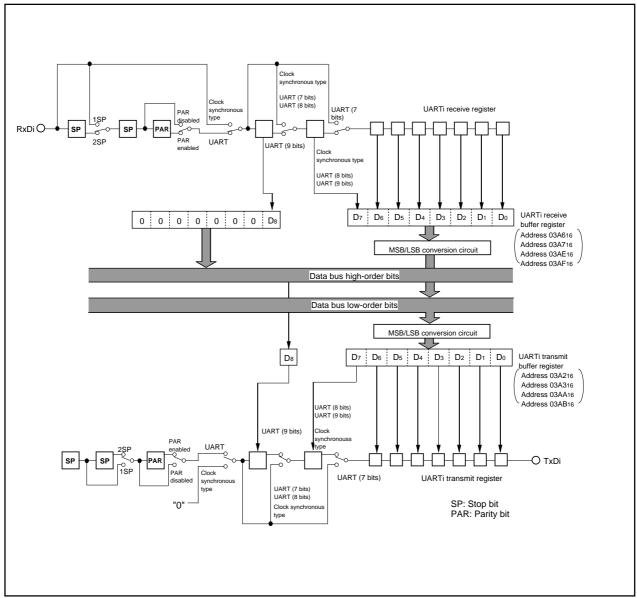

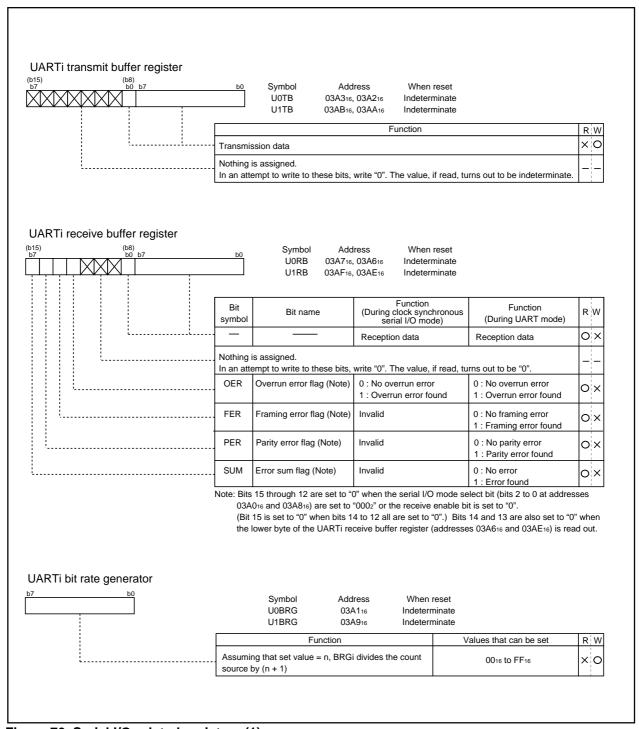

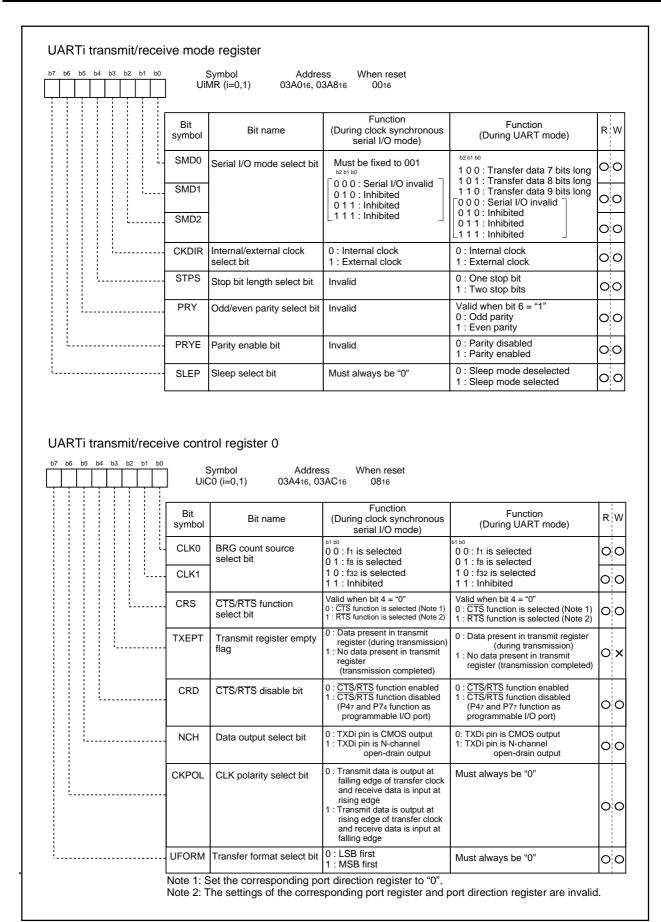

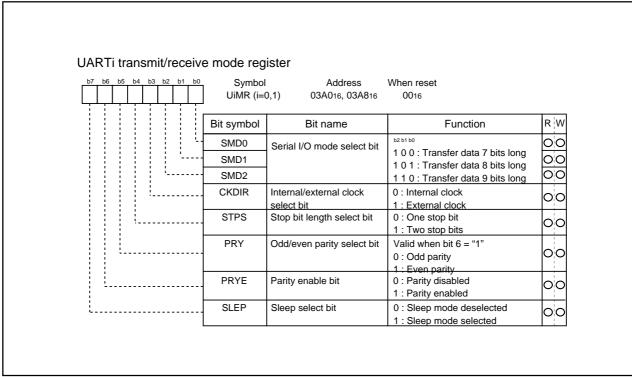

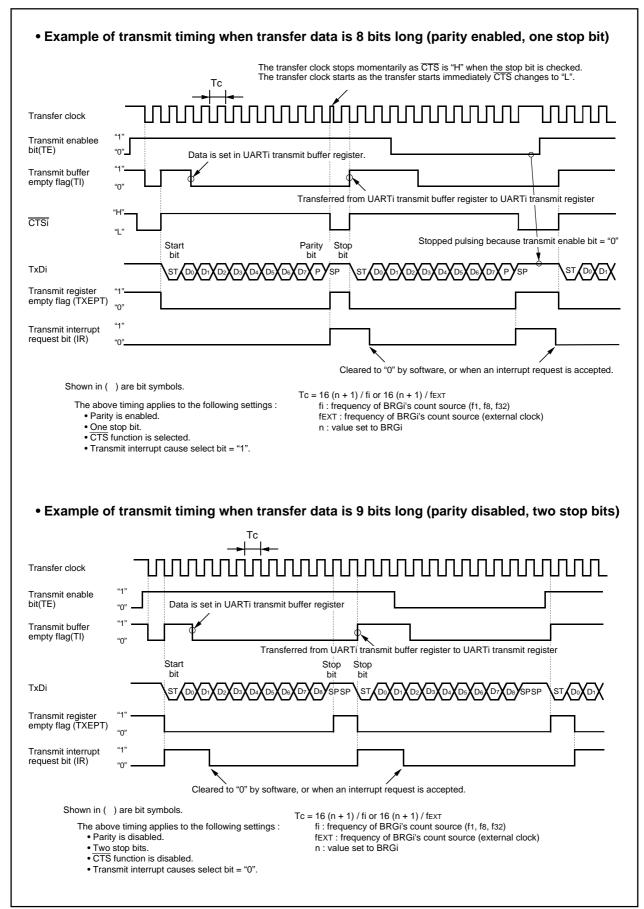

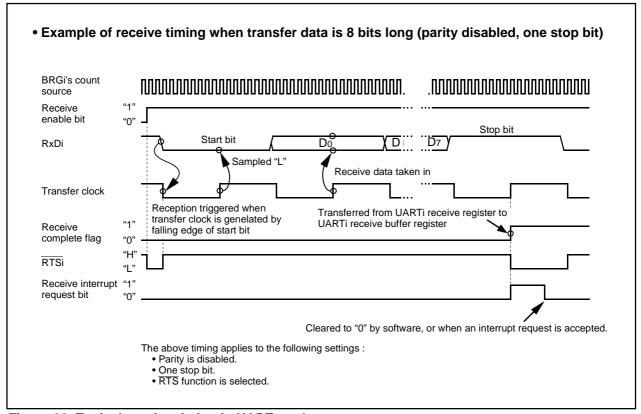

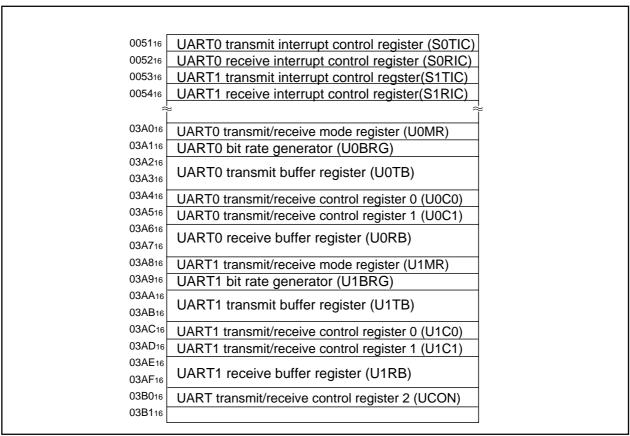

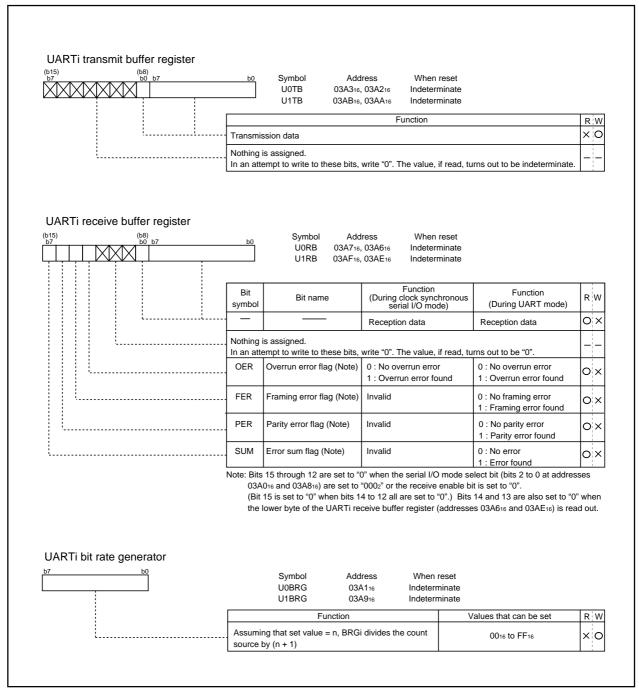

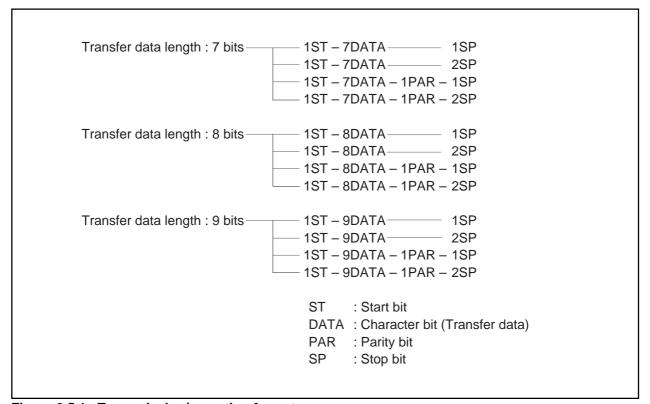

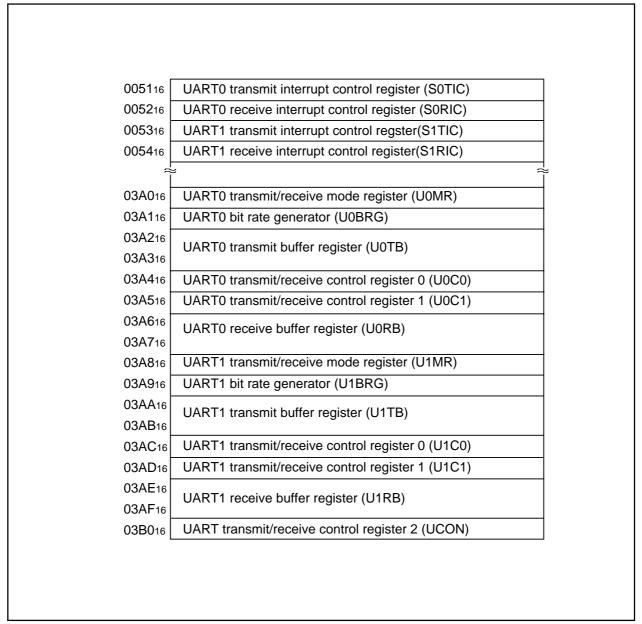

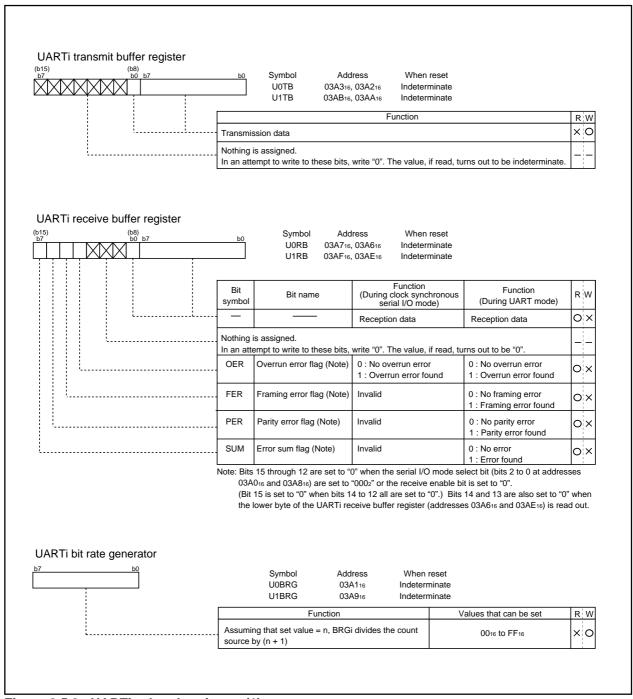

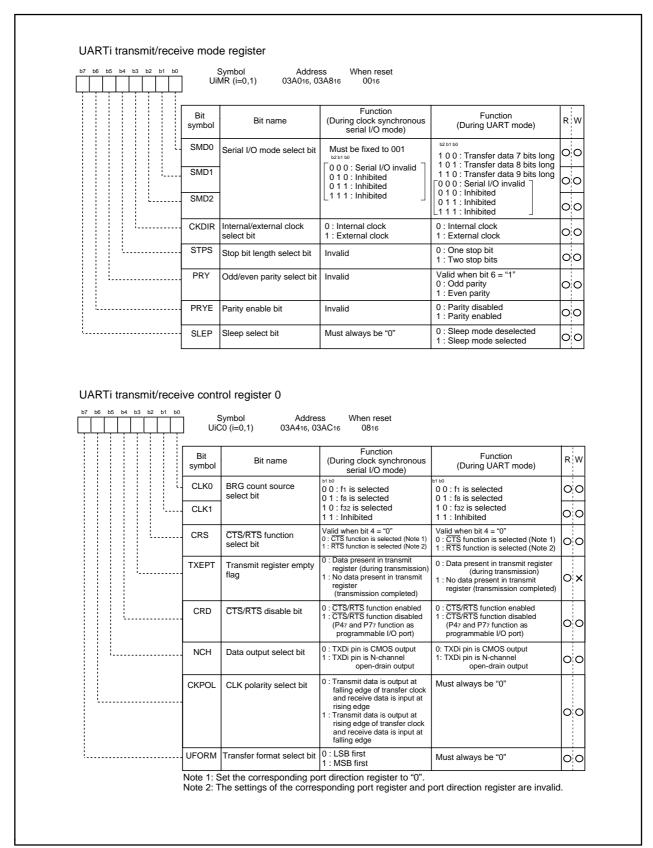

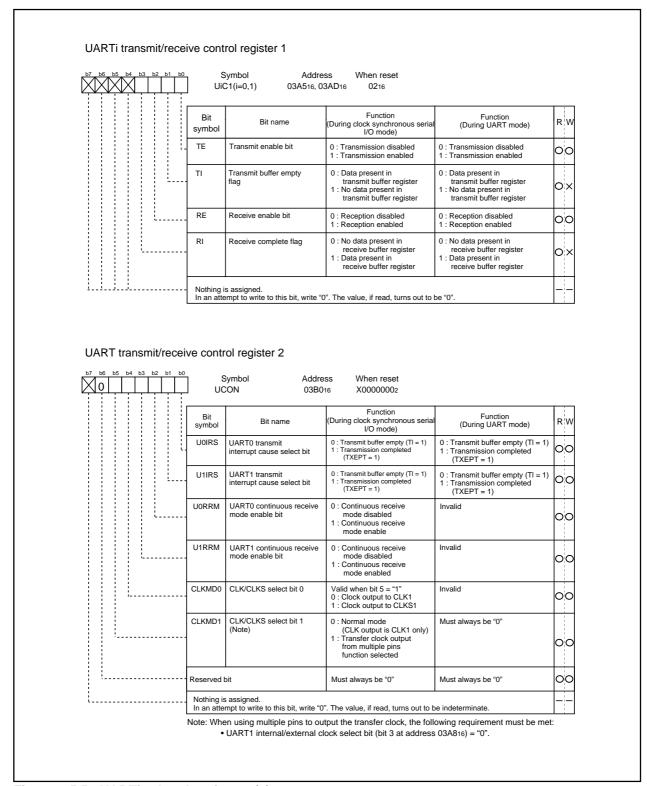

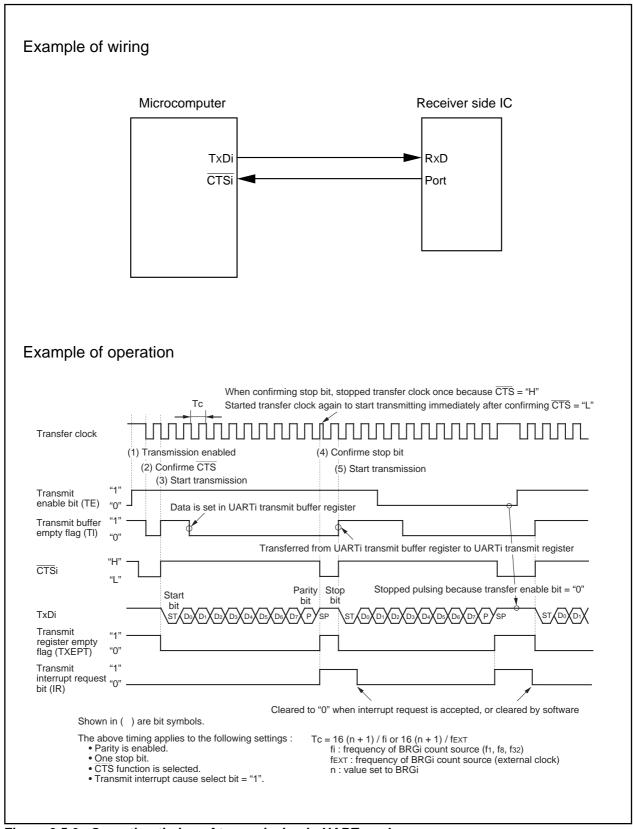

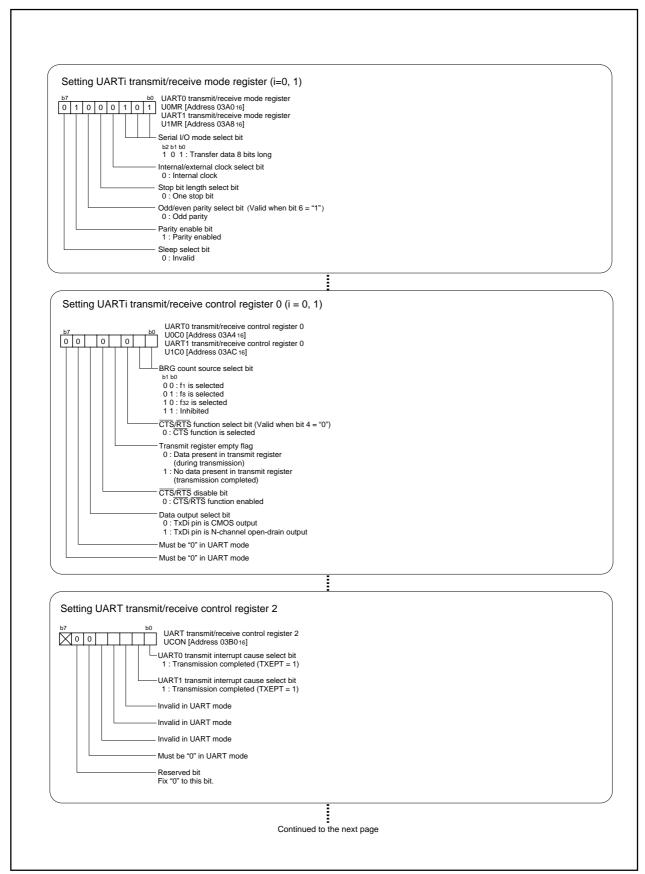

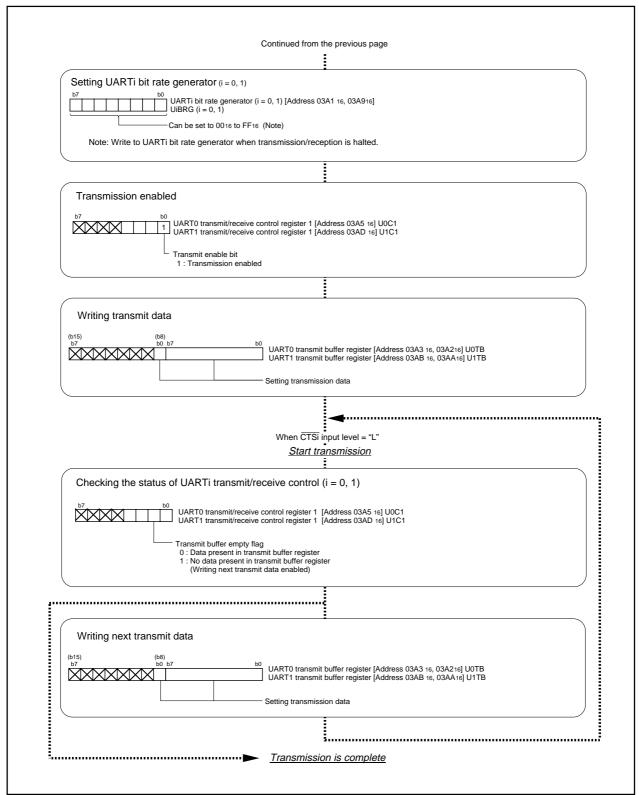

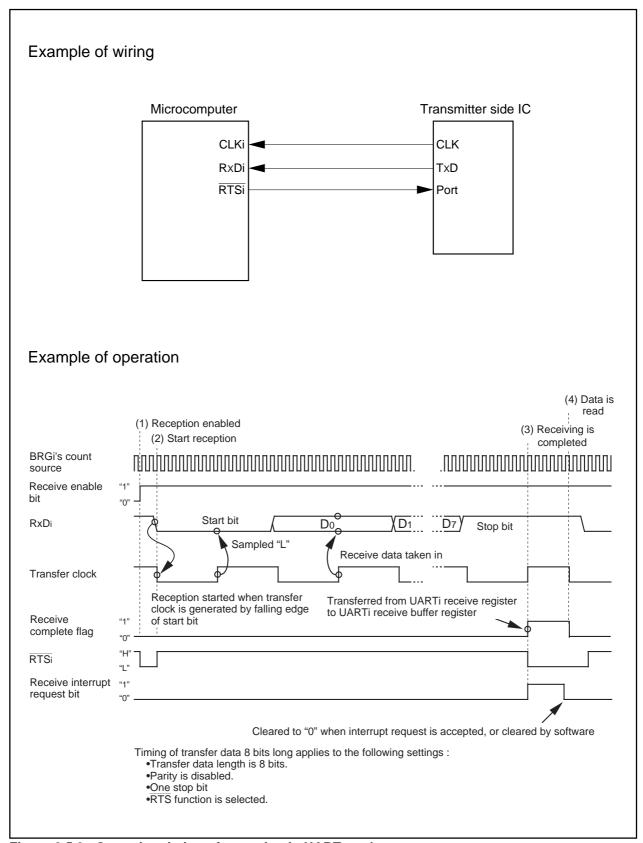

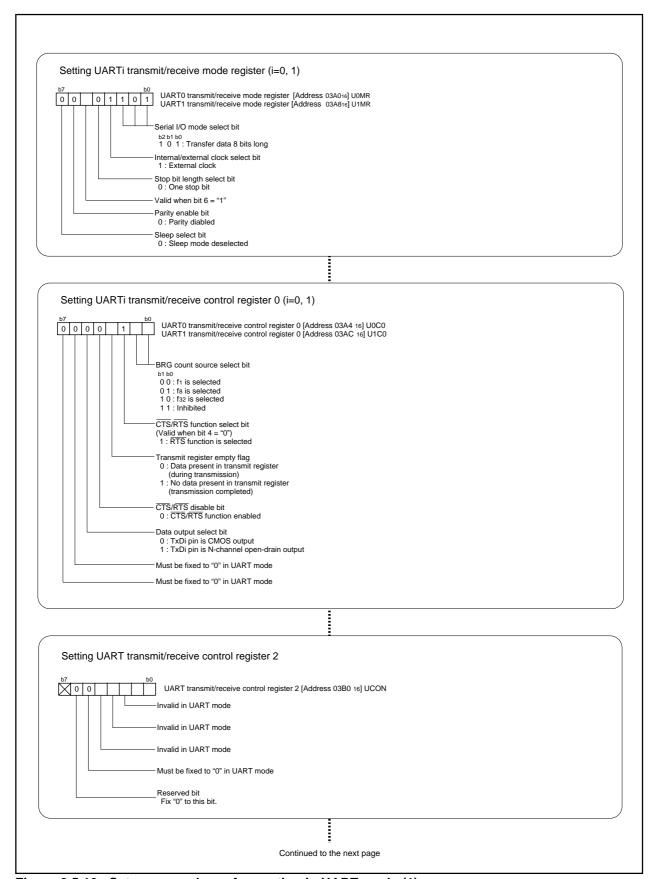

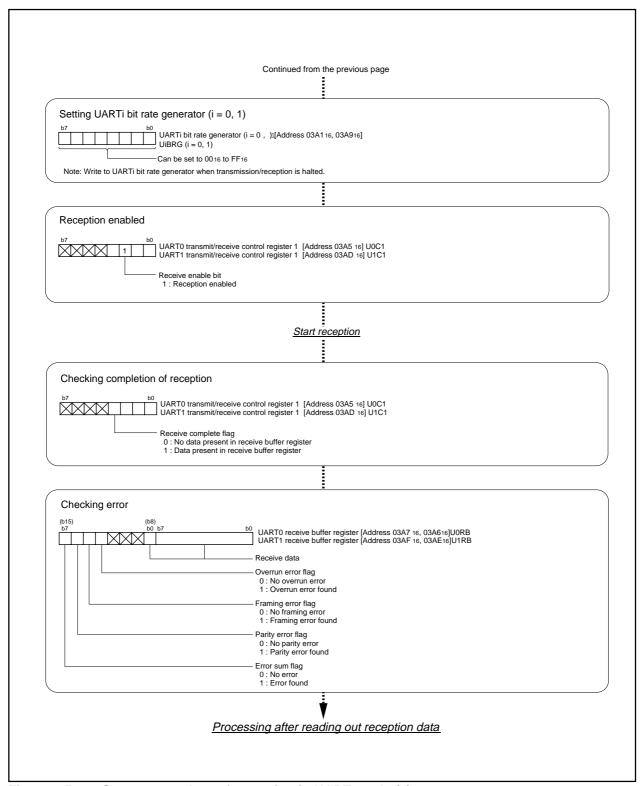

| 2.5 Clock-Asynchronous Serial I/O (UART)                                                                | 246       |

| 2.5.1 Overview                                                                                          | 246       |

| 2.5.2 Operation of Serial I/O (transmission in UART mode)                                               | 254       |

| 2.5.3 Operation of Serial I/O (reception in UART mode)                                                  | 258       |

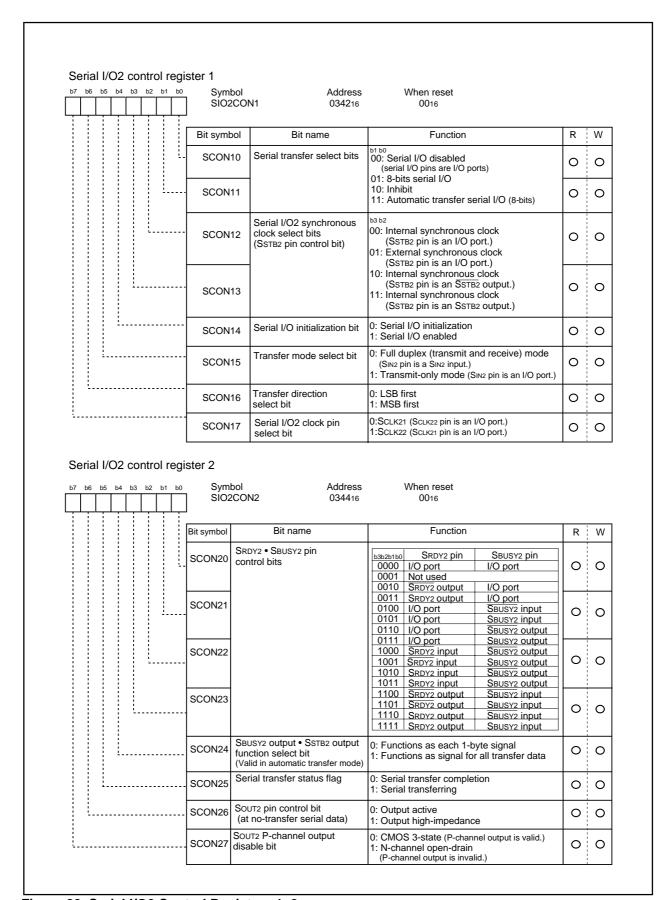

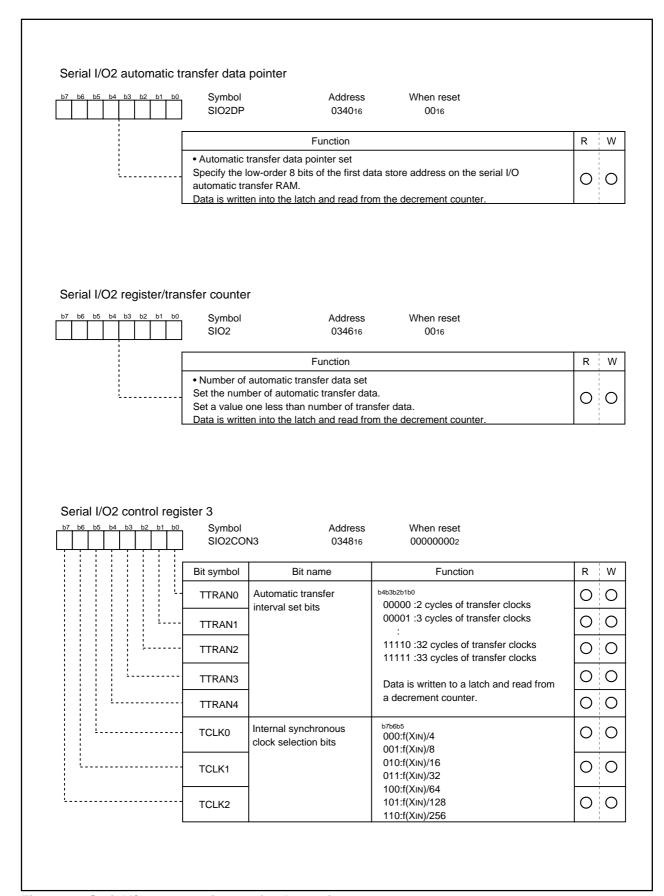

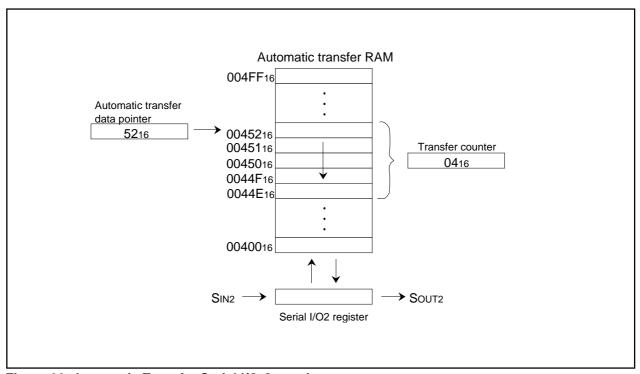

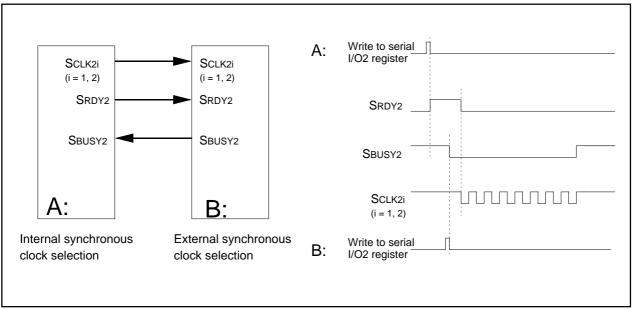

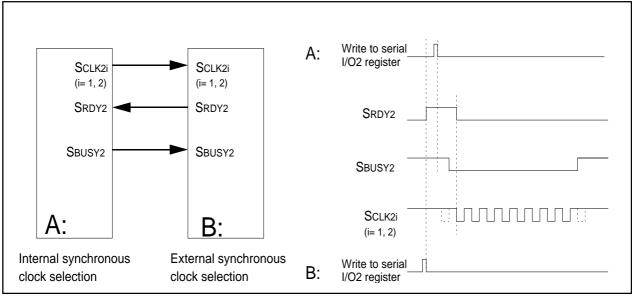

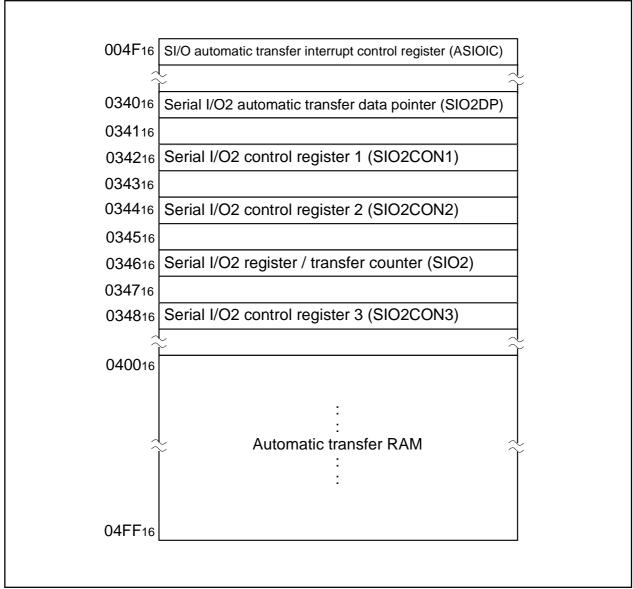

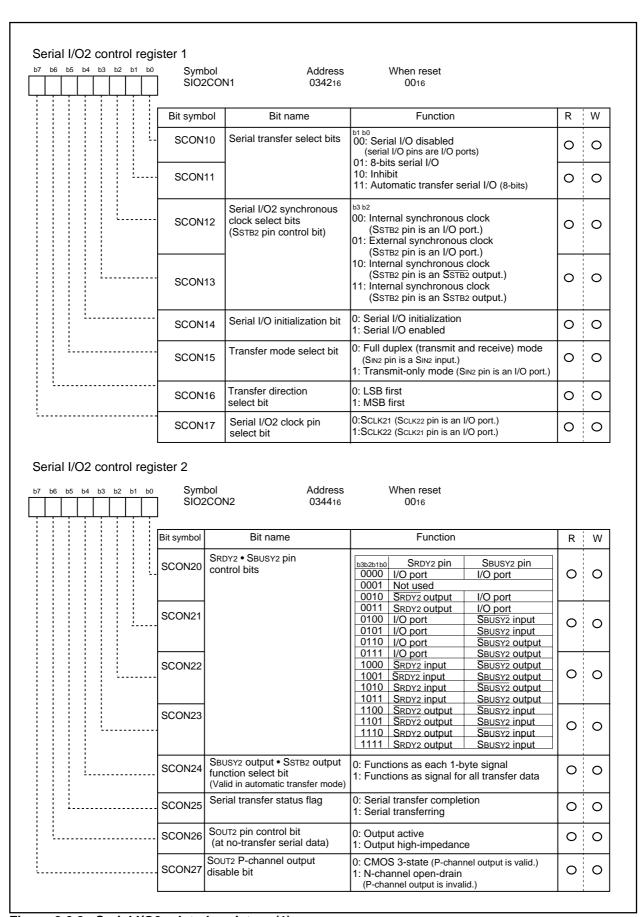

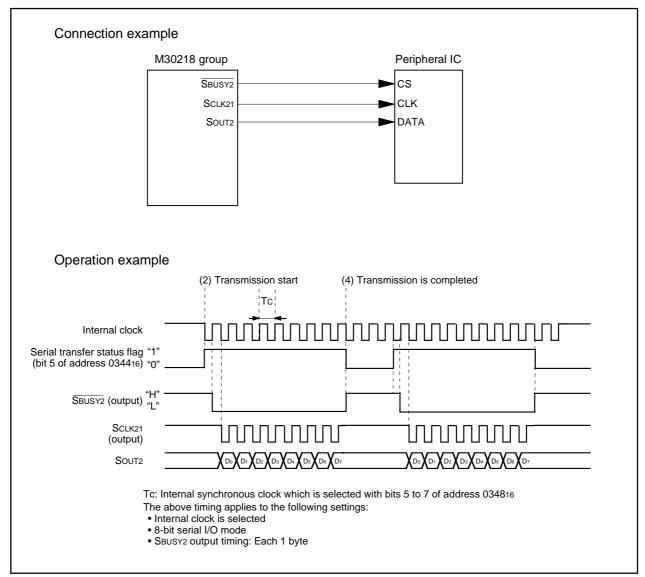

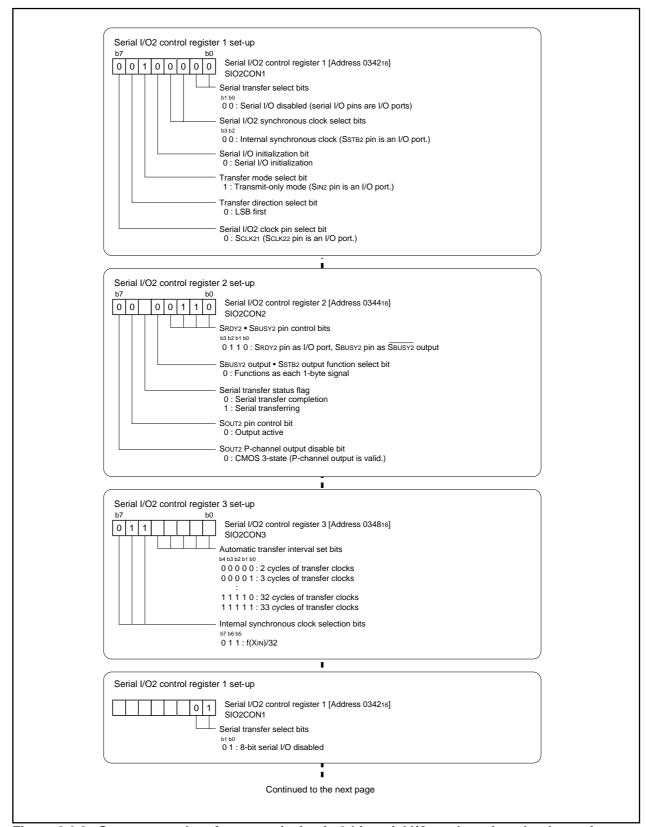

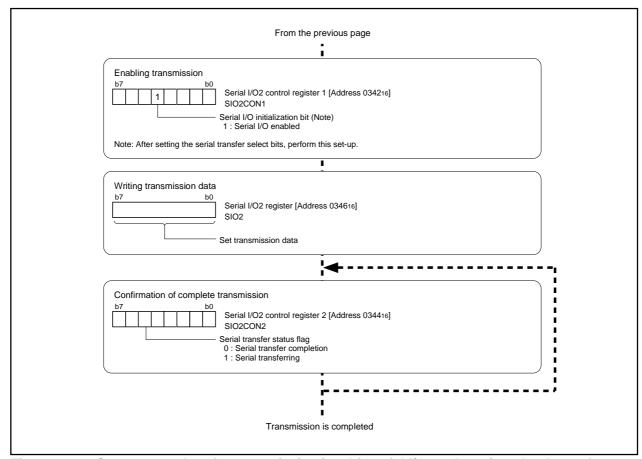

| 2.6 Serial I/O2                                                                                         | 262       |

| 2.6.1 Overview                                                                                          | 262       |

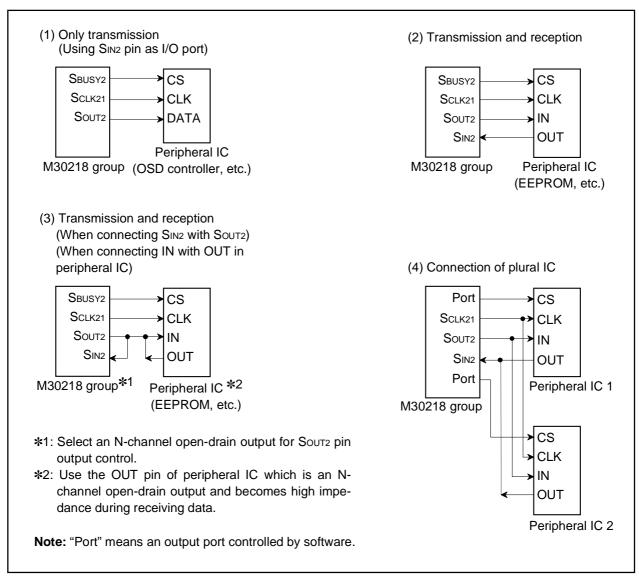

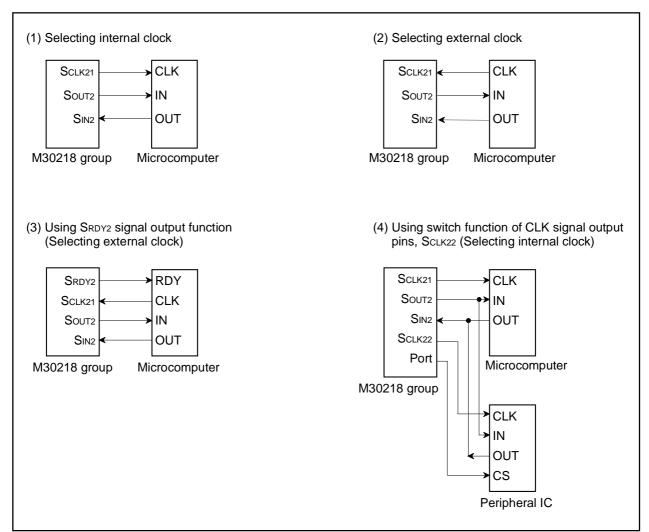

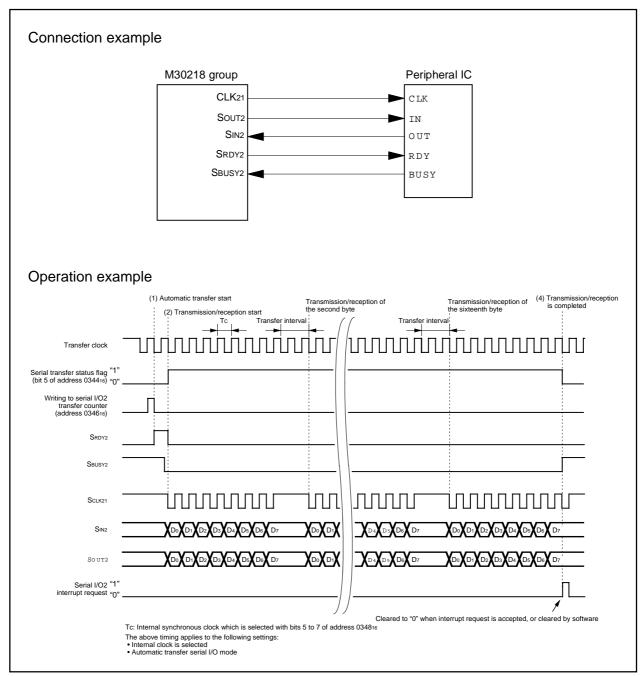

| 2.6.2 Serial I/O2 connection examples                                                                   | 267       |

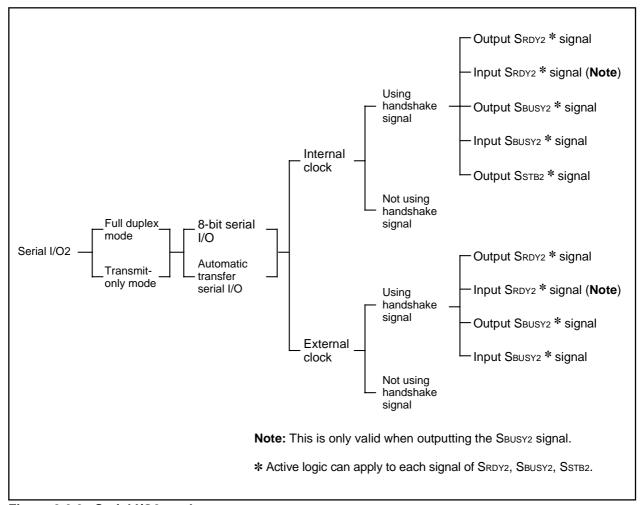

| 2.6.3 Serial I/O2 modes                                                                                 | 269       |

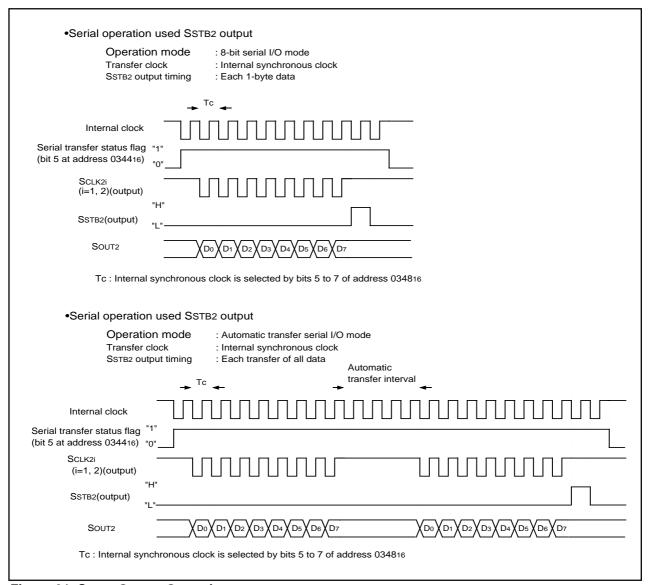

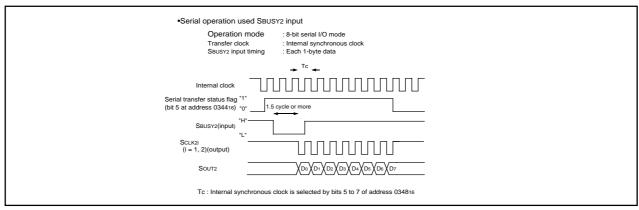

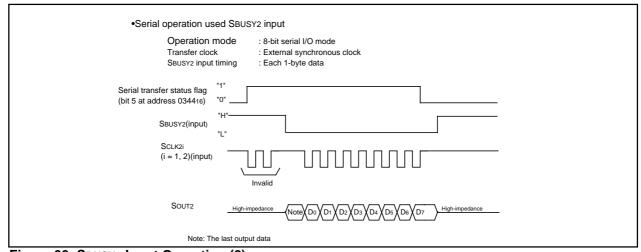

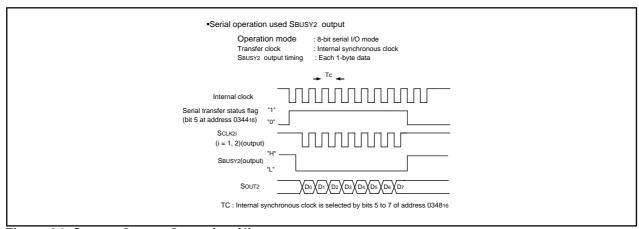

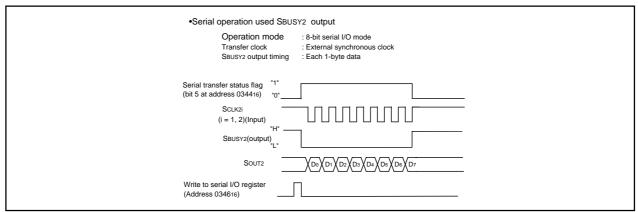

| 2.6.4 Serial I/O2 Operations (transmission in 8-bit serial I/O mode)                                    | 270       |

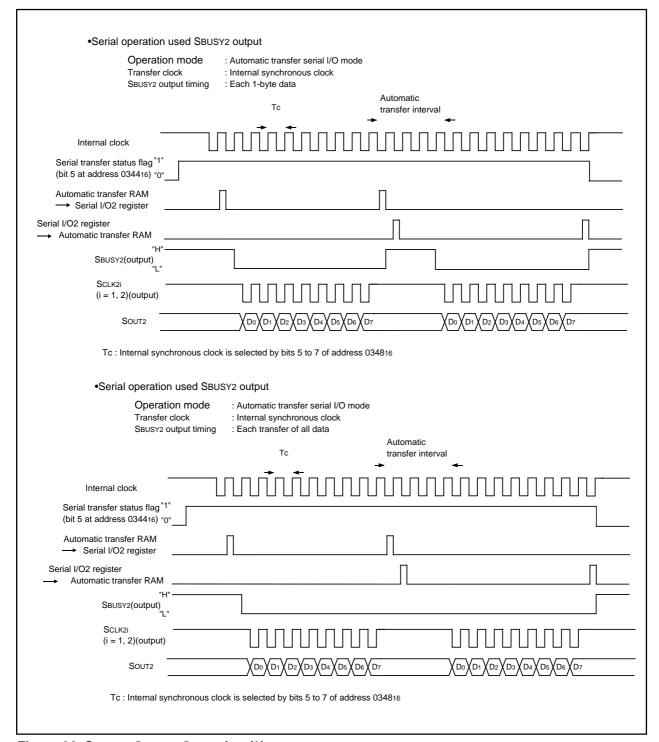

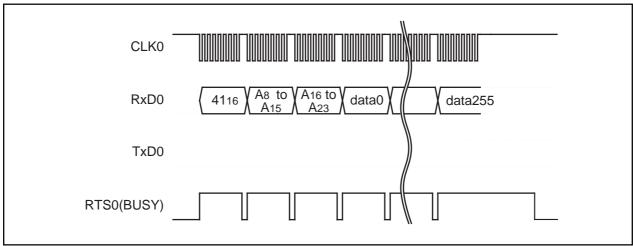

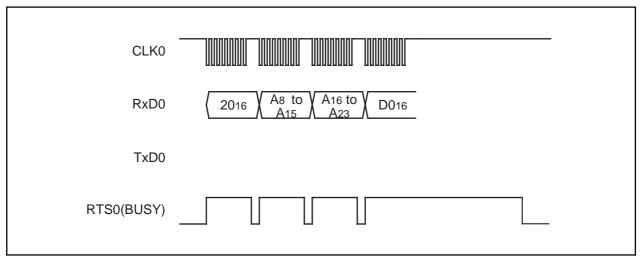

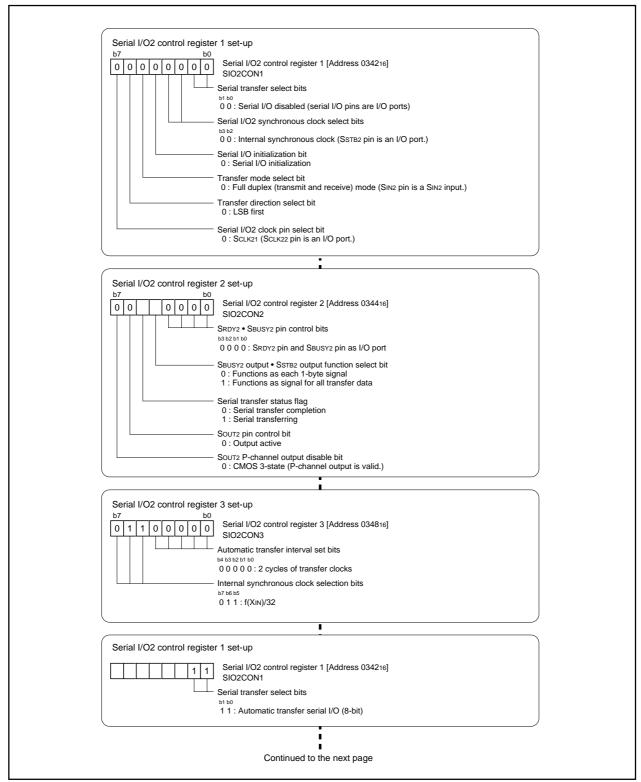

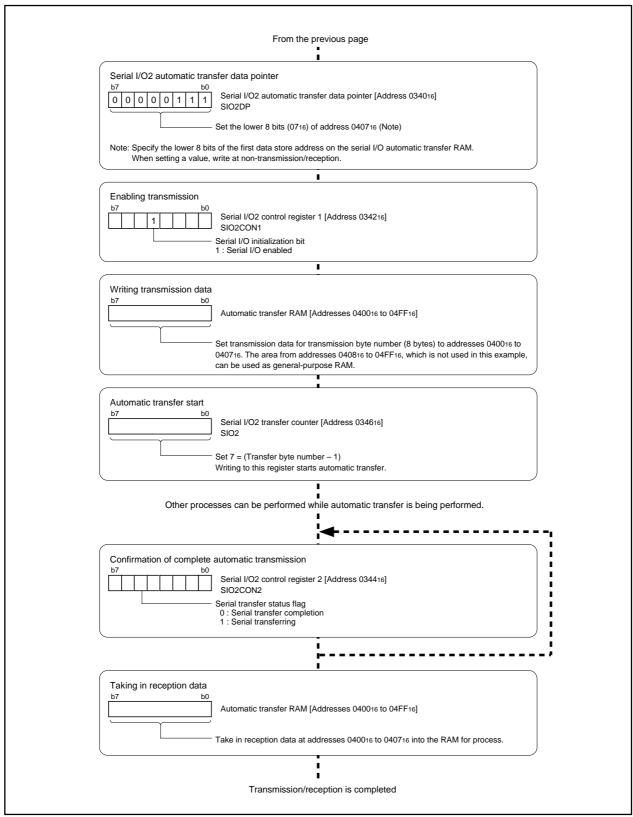

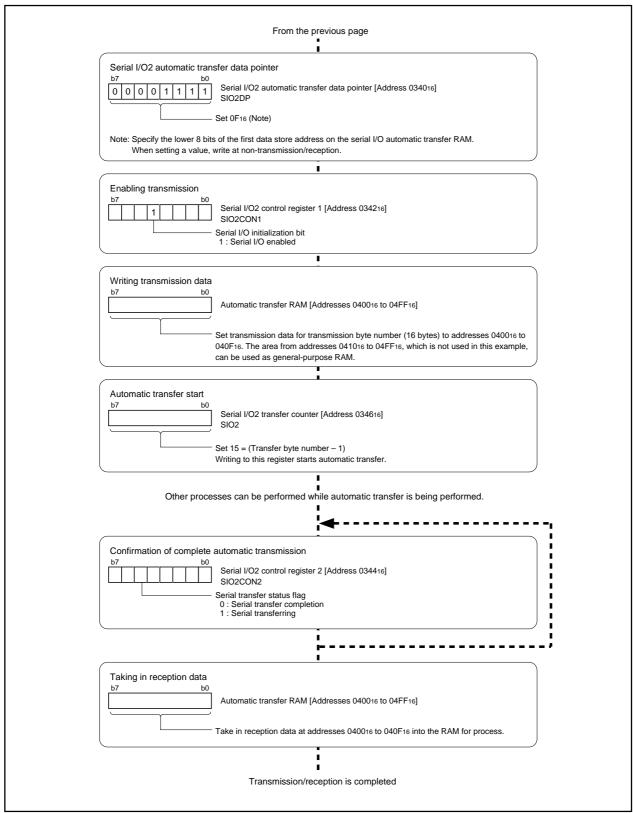

| 2.6.5 Serial I/O2 Operations (transmission/reception in automatic transfer serial I/O n                 | node) 274 |

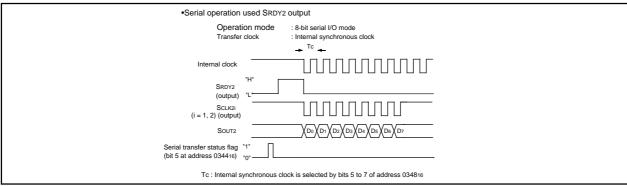

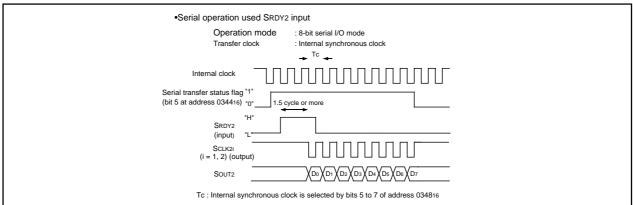

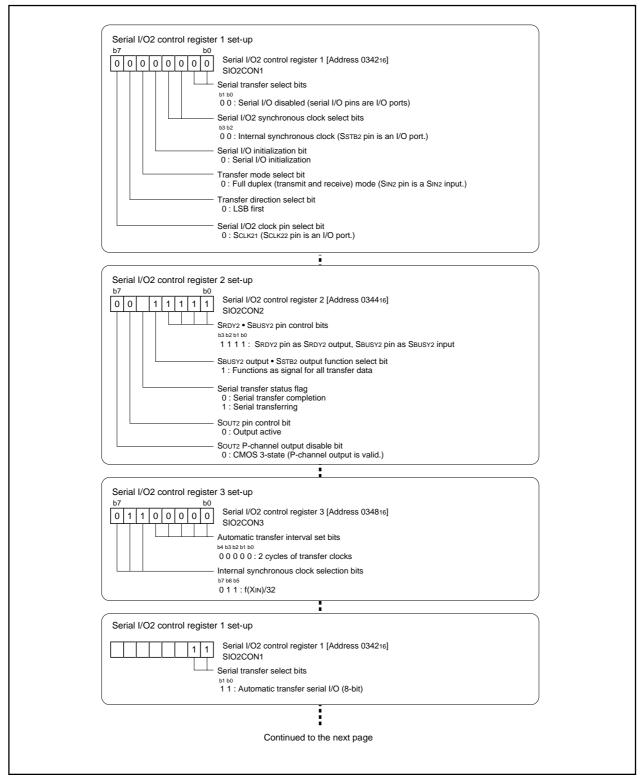

| 2.6.6 Serial I/O2 Operations (transmission/reception in automatic transfer serial I/O handshake signal) | _         |

| 2.6.7 Precautions for Serial I/O2                                                                       | 282       |

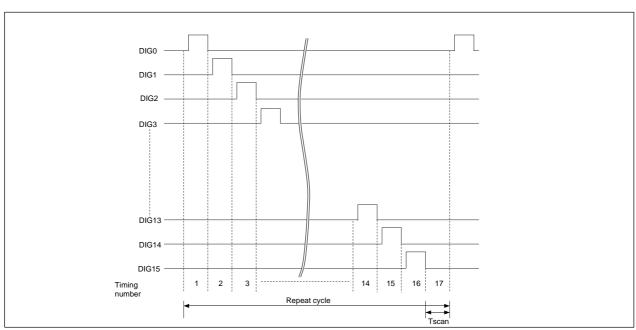

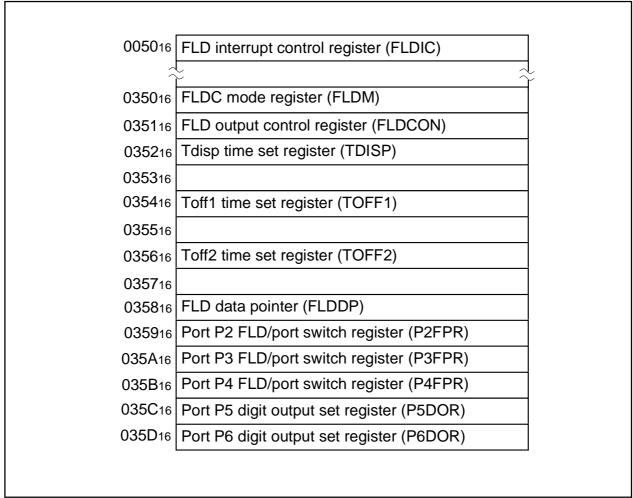

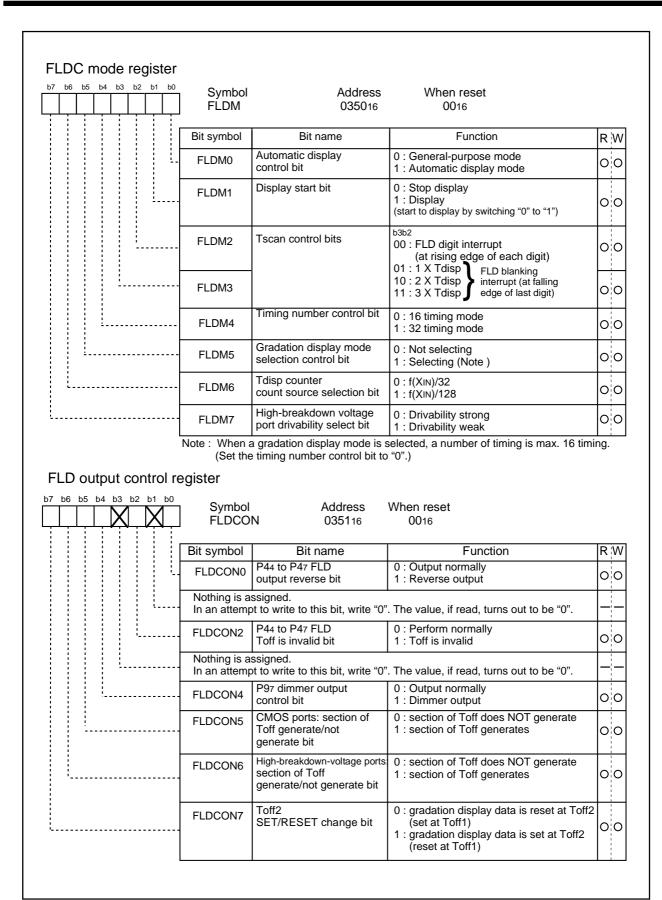

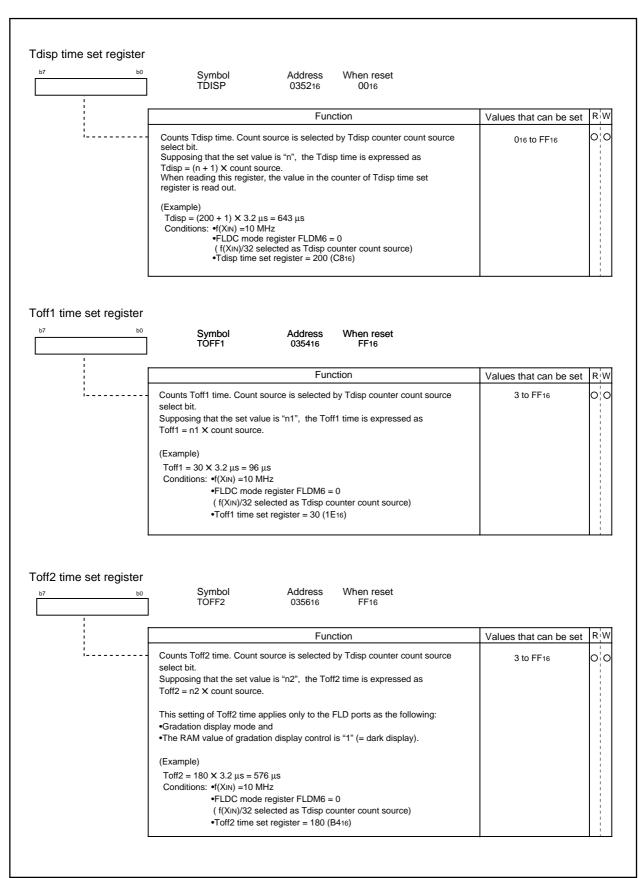

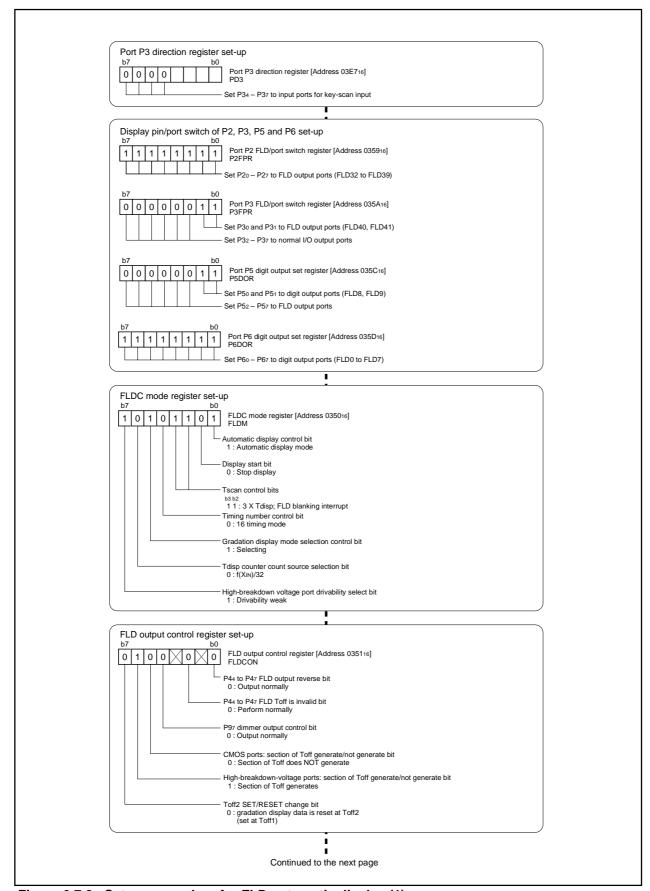

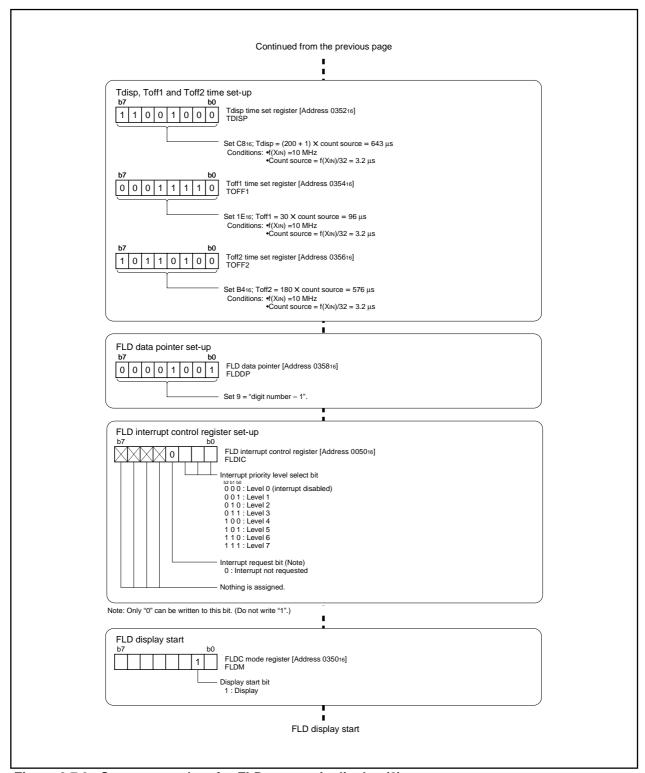

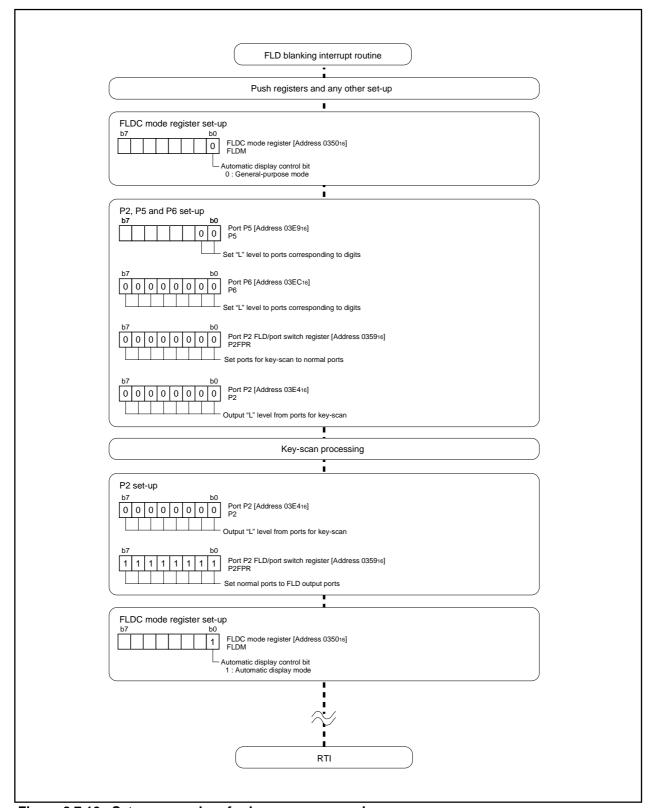

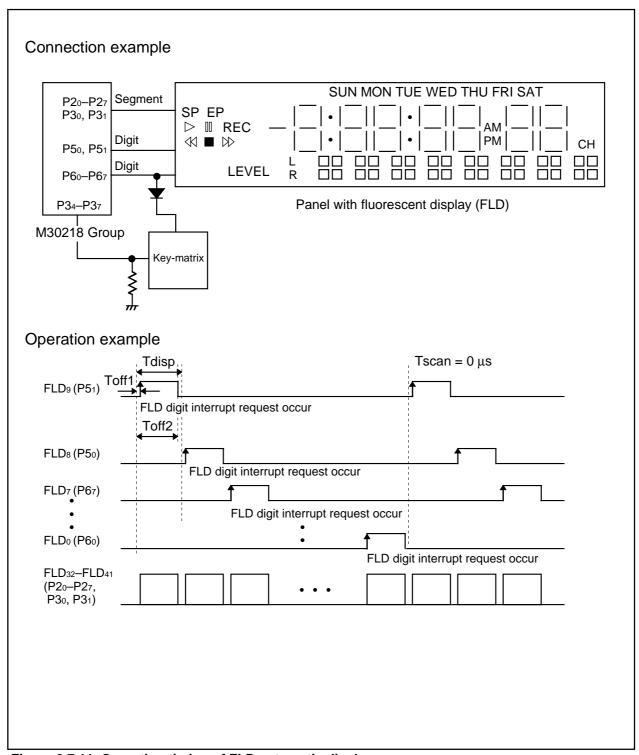

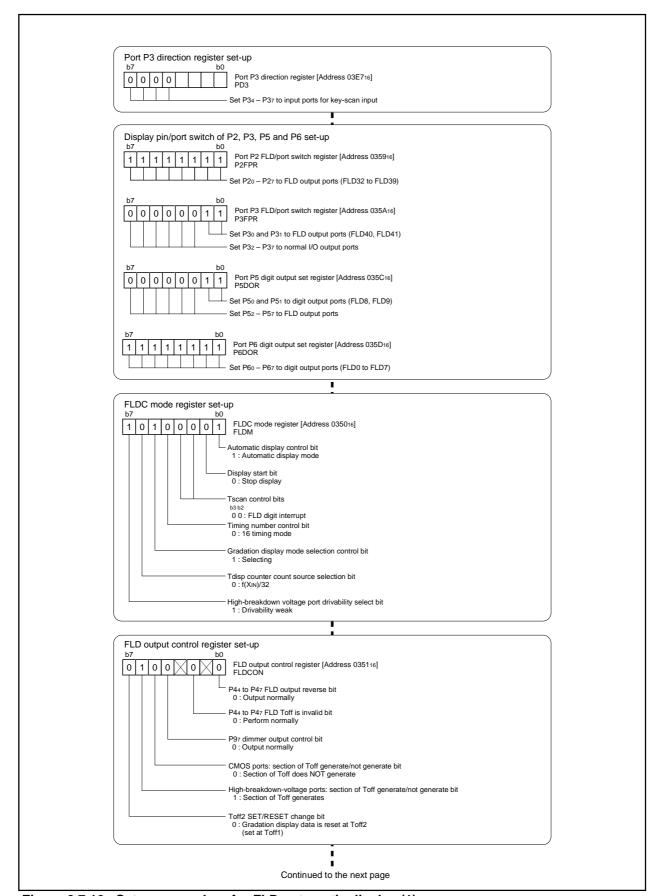

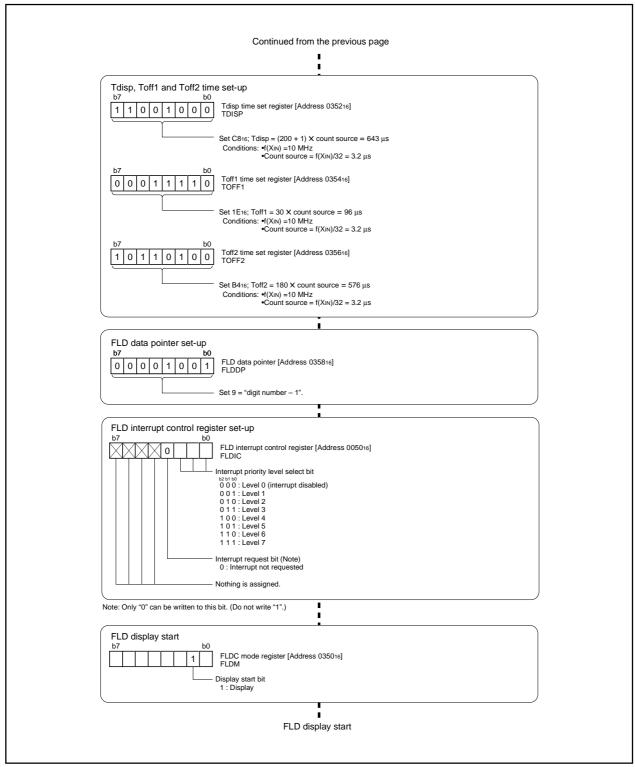

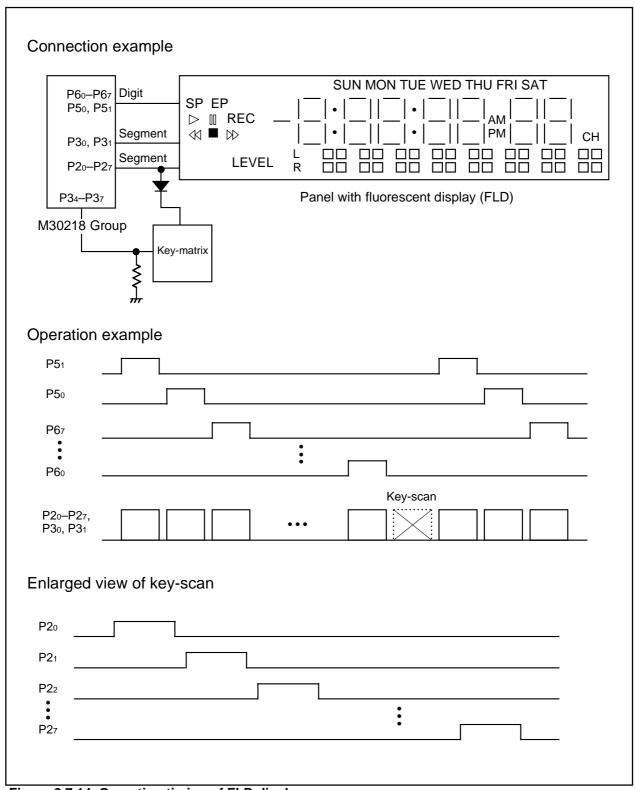

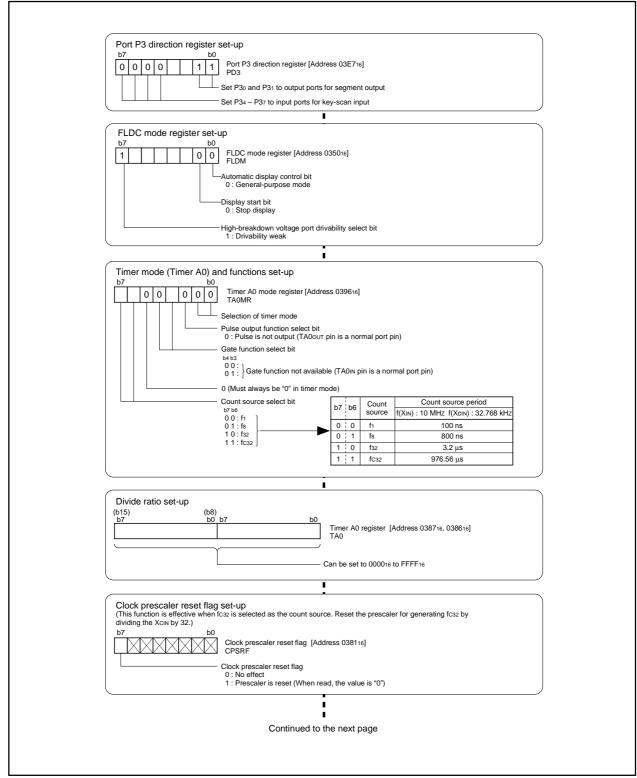

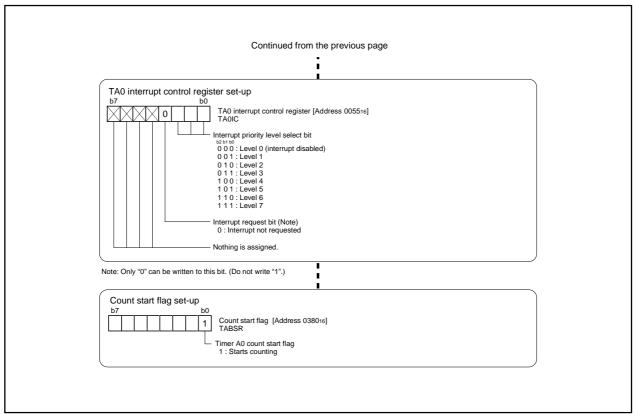

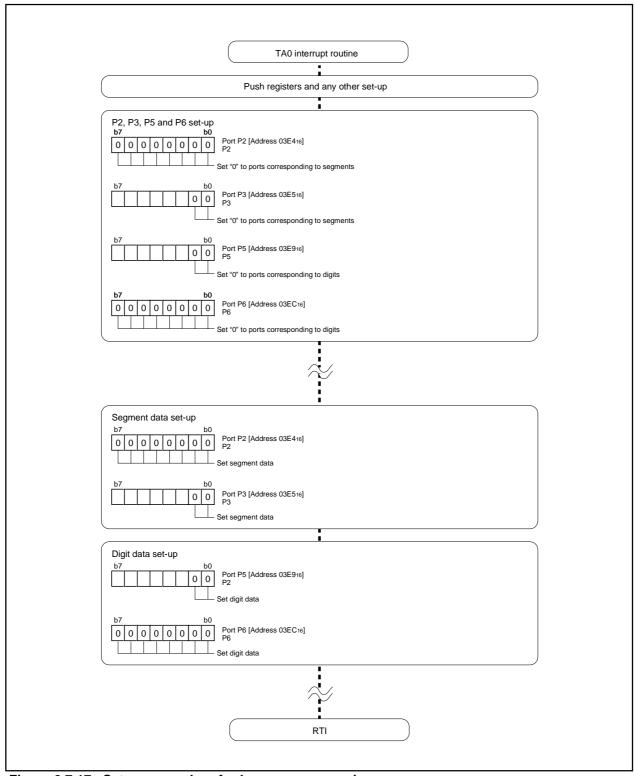

| 2.7 FLD (VFD) Controller                                                                                | 286       |

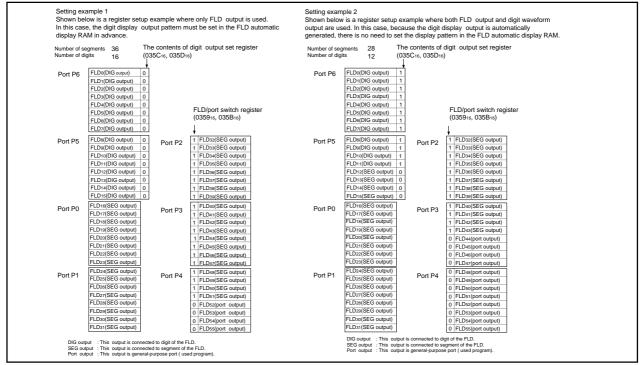

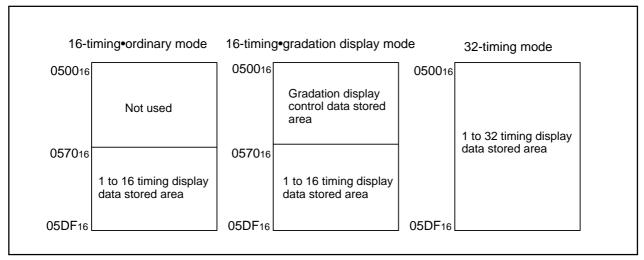

| 2.7.1 Overview                                                                                          | 286       |

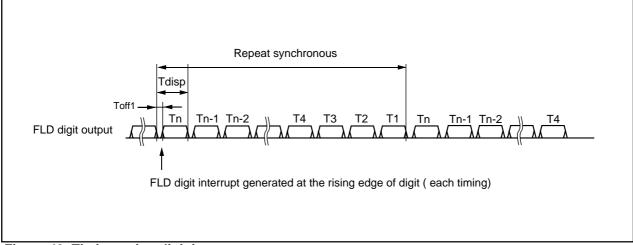

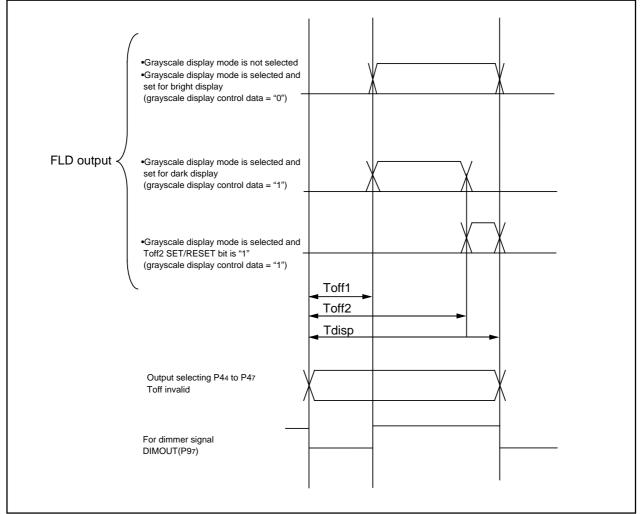

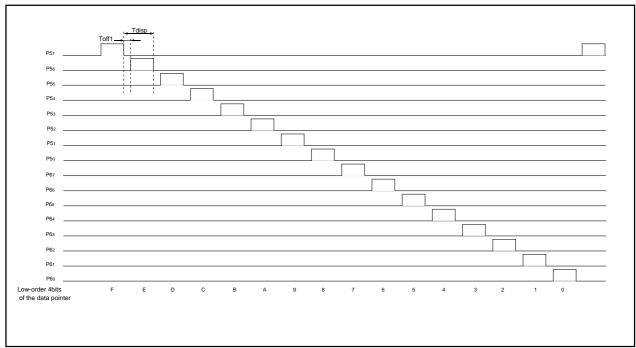

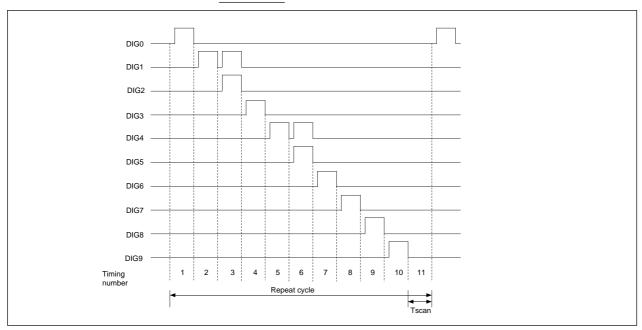

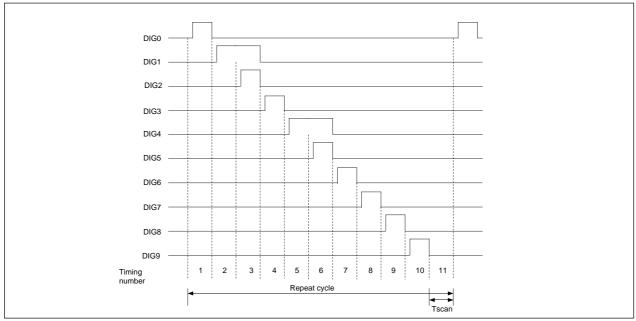

| 2.7.2 FLD operation (FLD automatic display and key-scan using segments)                                 | 296       |

| 2.7.3 FLD operation (FLD automatic display and key-scan using digits)                                   | 302       |

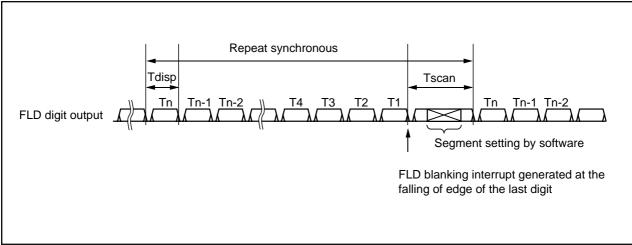

| 2.7.4 FLD operation (FLD display and key-scan using segment by software)                                | 306       |

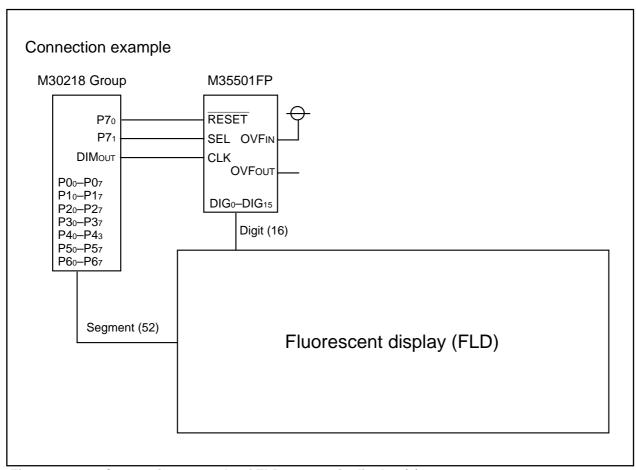

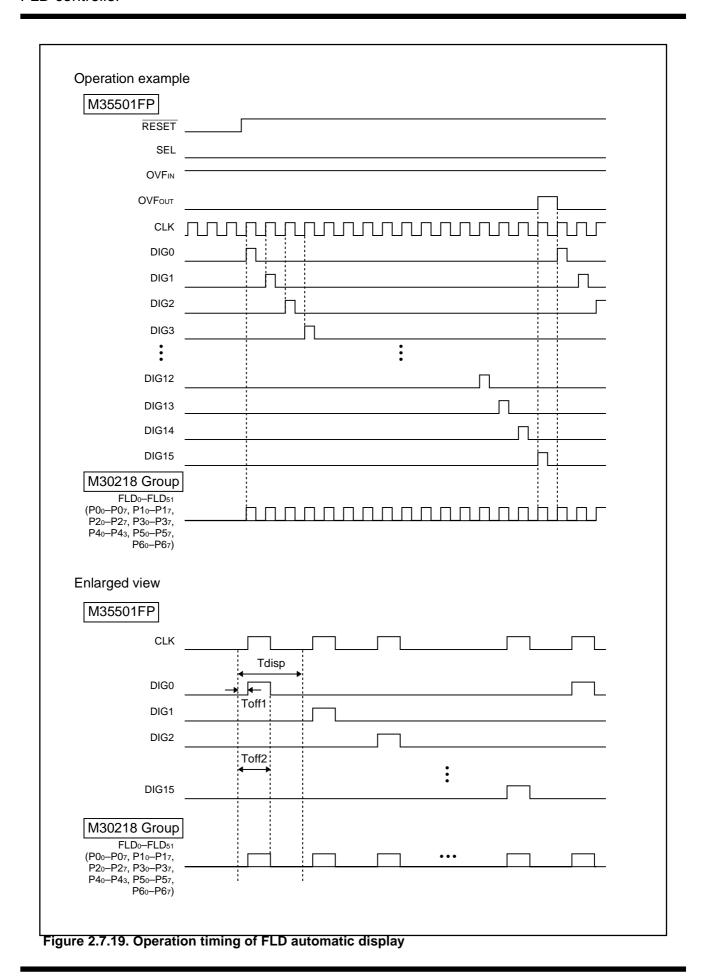

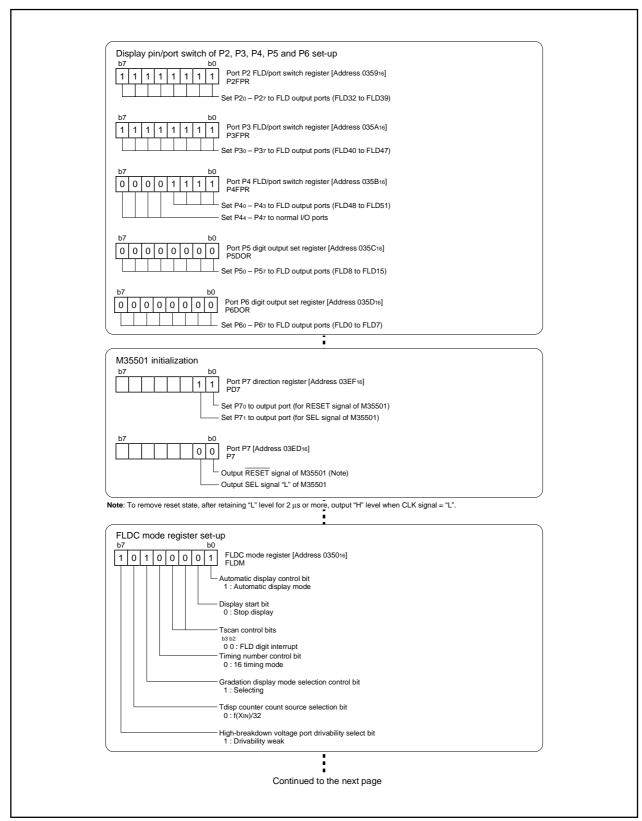

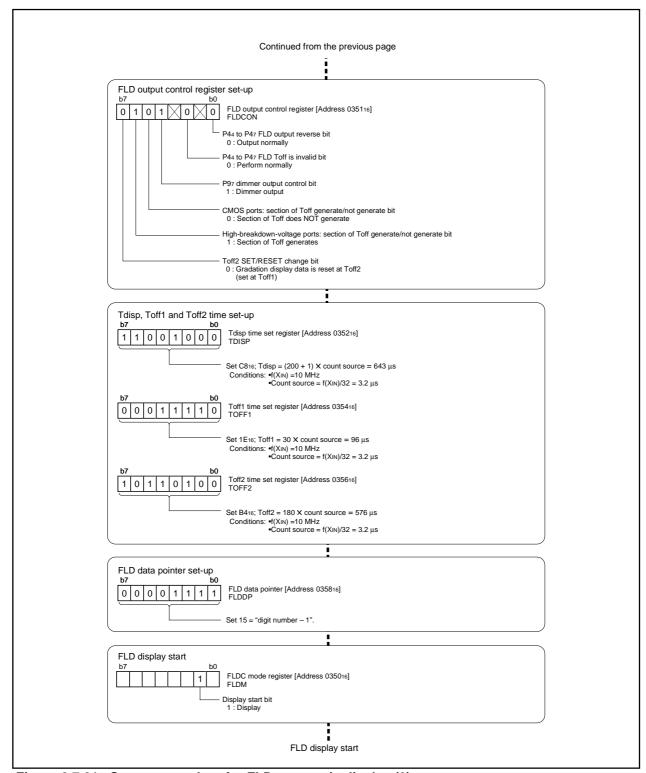

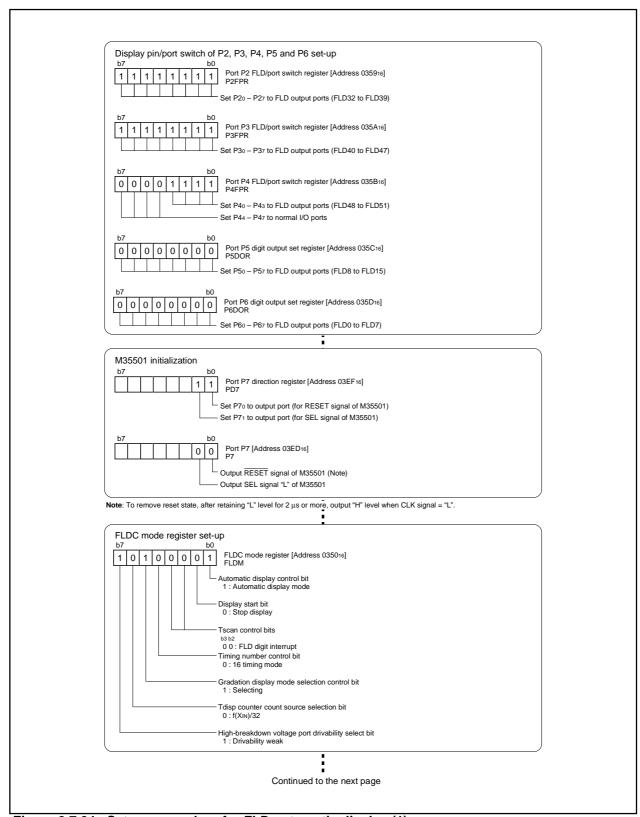

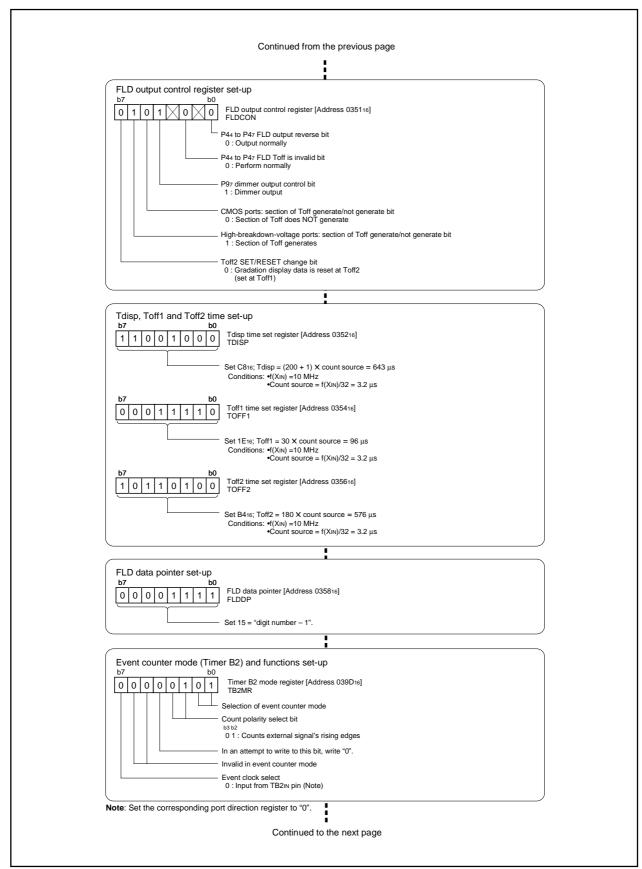

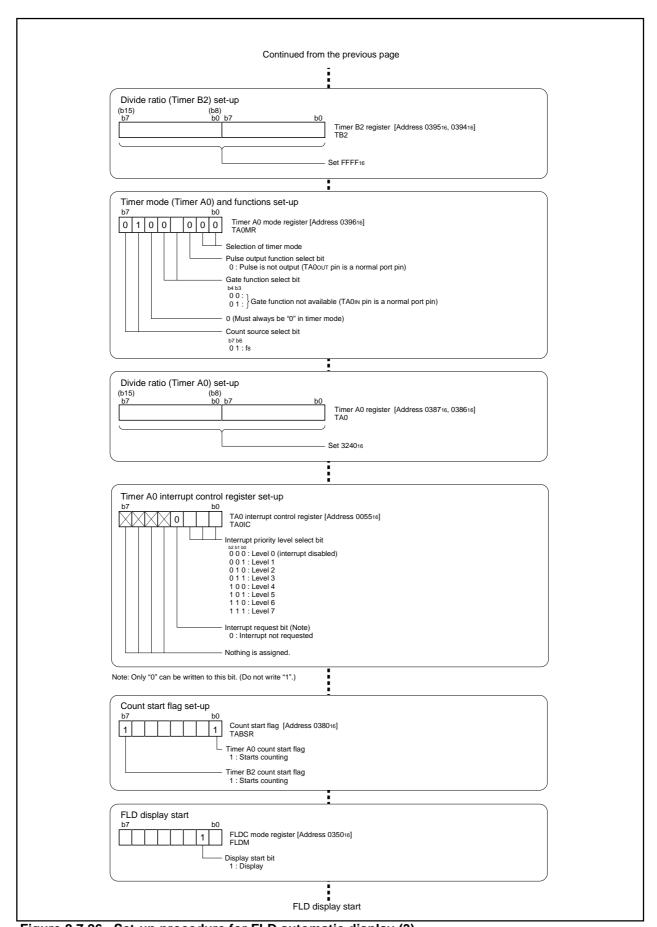

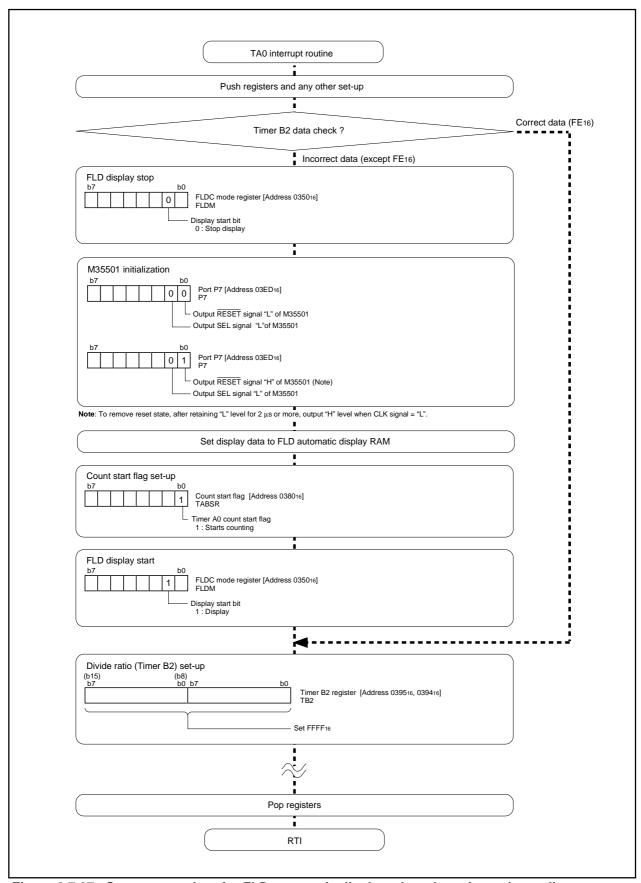

| 2.7.5 FLD operation (Display with digit expander M35501FP)                                              | 312       |

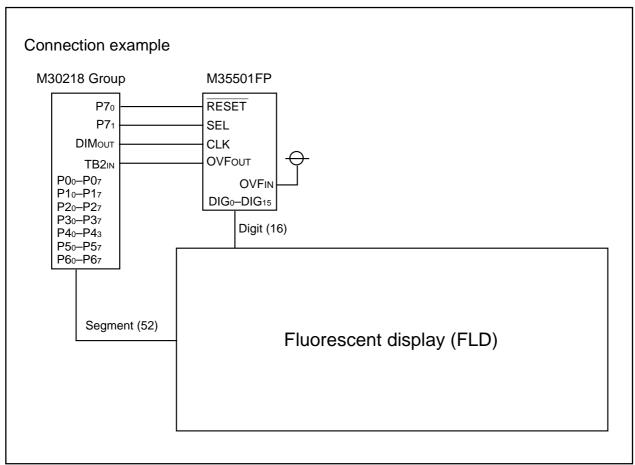

| 2.7.6 FLD operation (Display with digit expander M35501FP: column discrepancy)                          | 318       |

| 2.7.7 Precautions for FLD controller                                                                    | 325       |

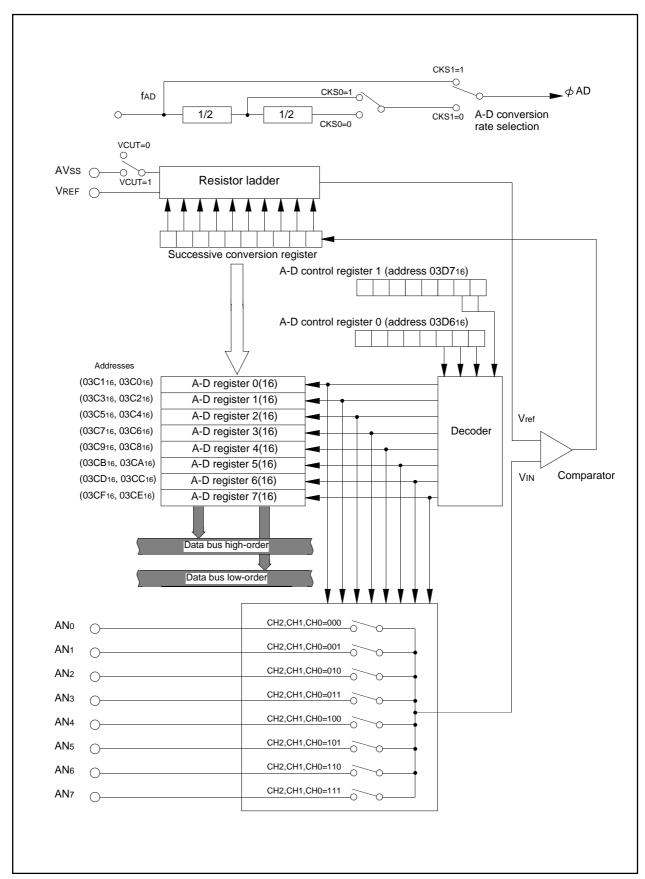

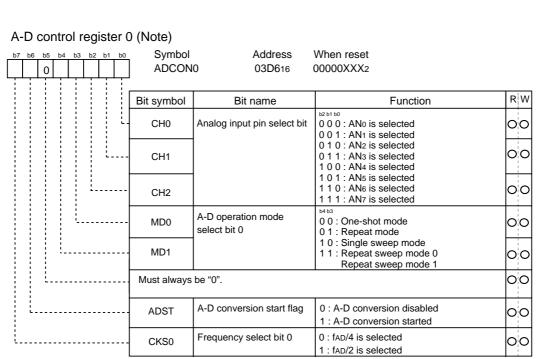

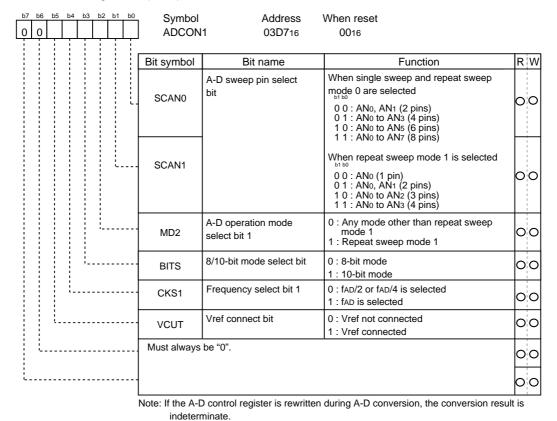

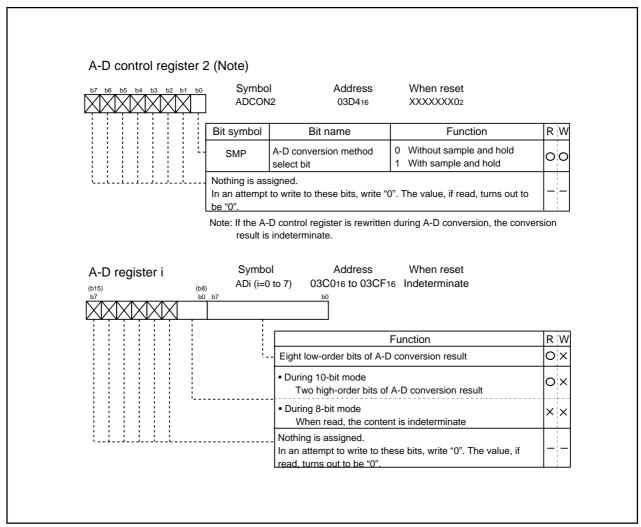

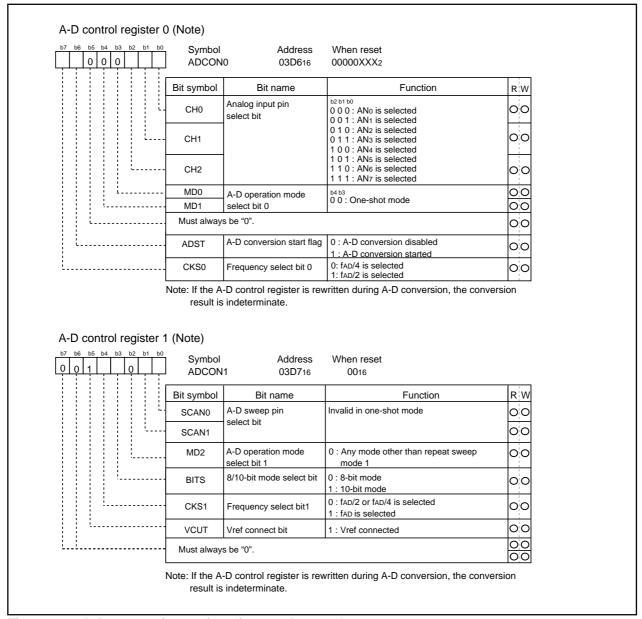

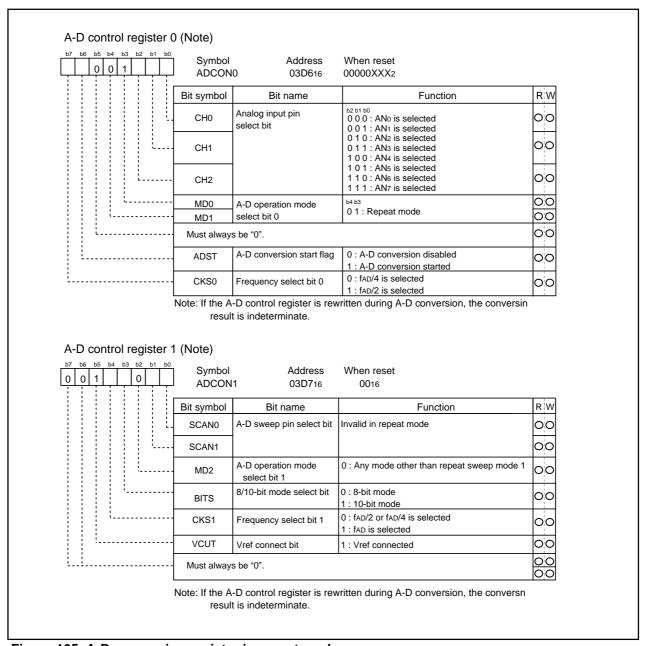

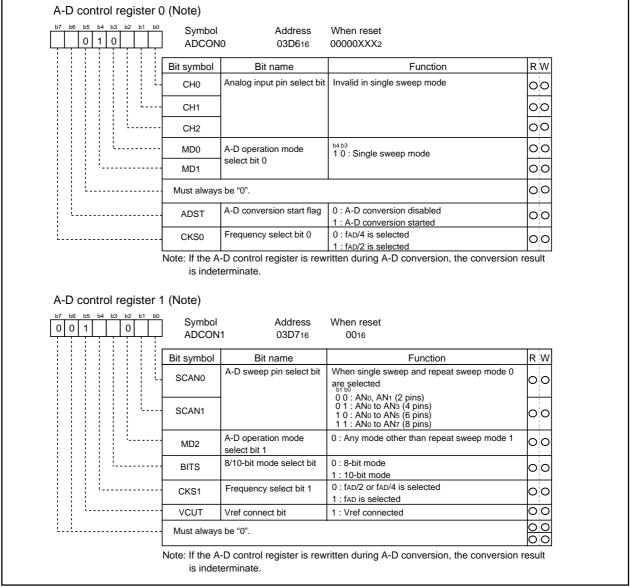

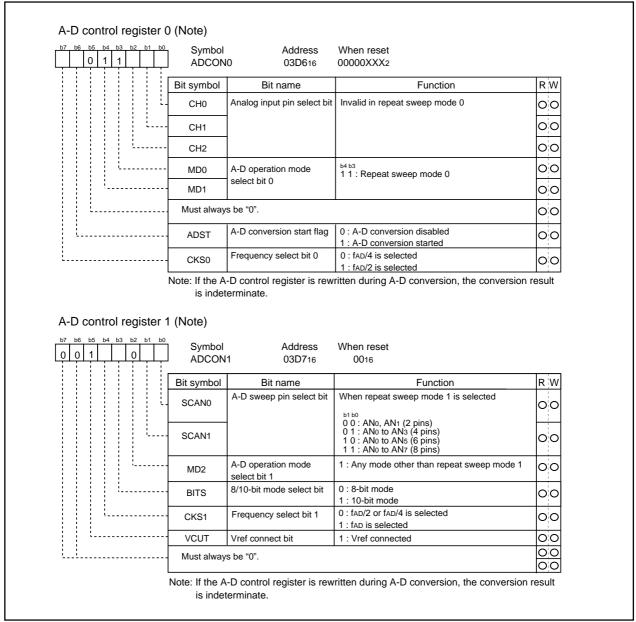

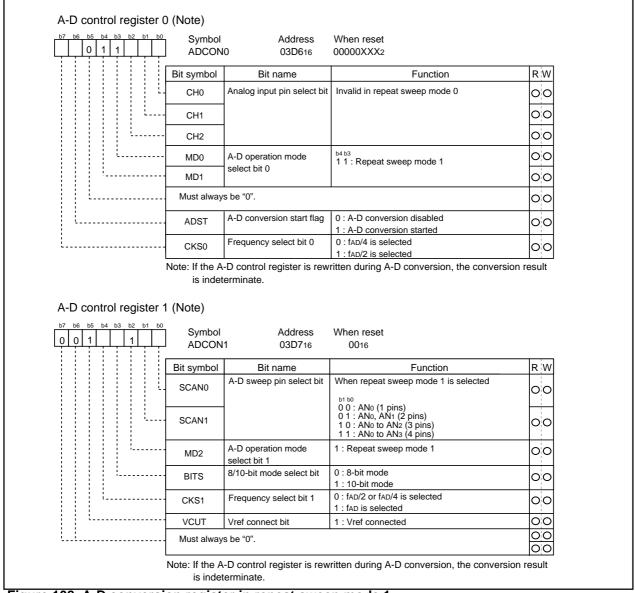

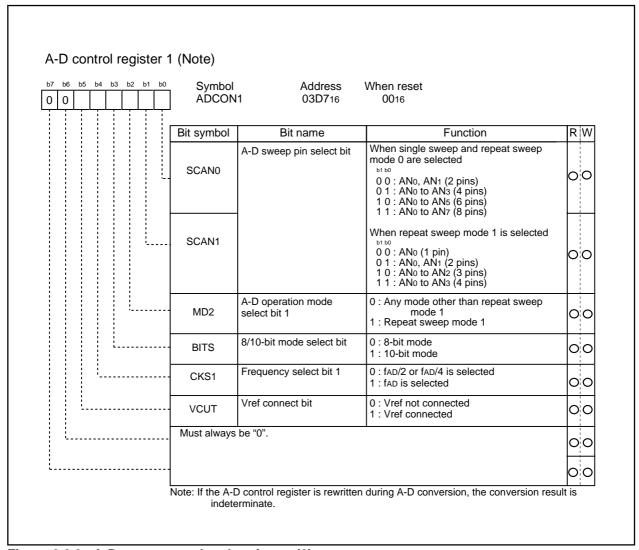

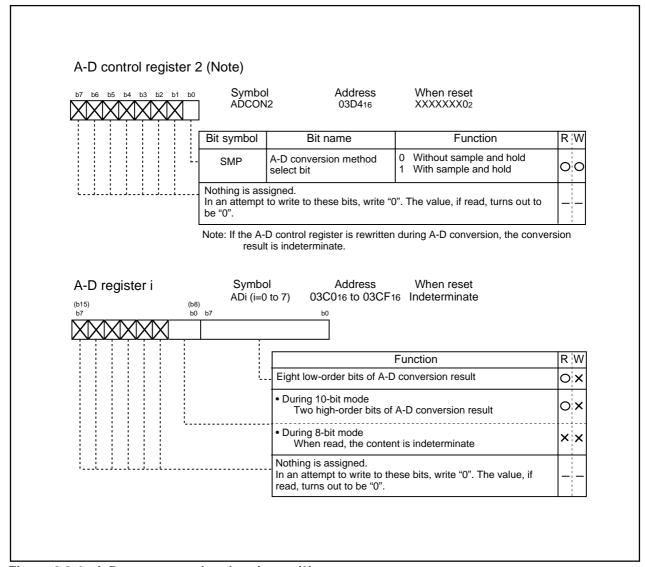

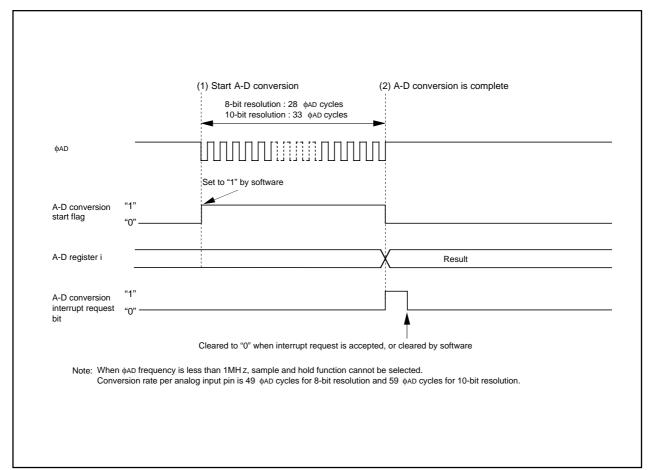

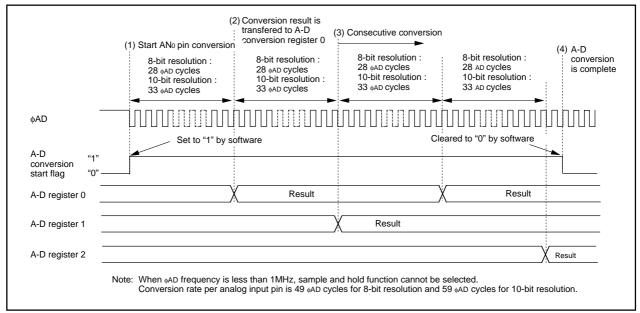

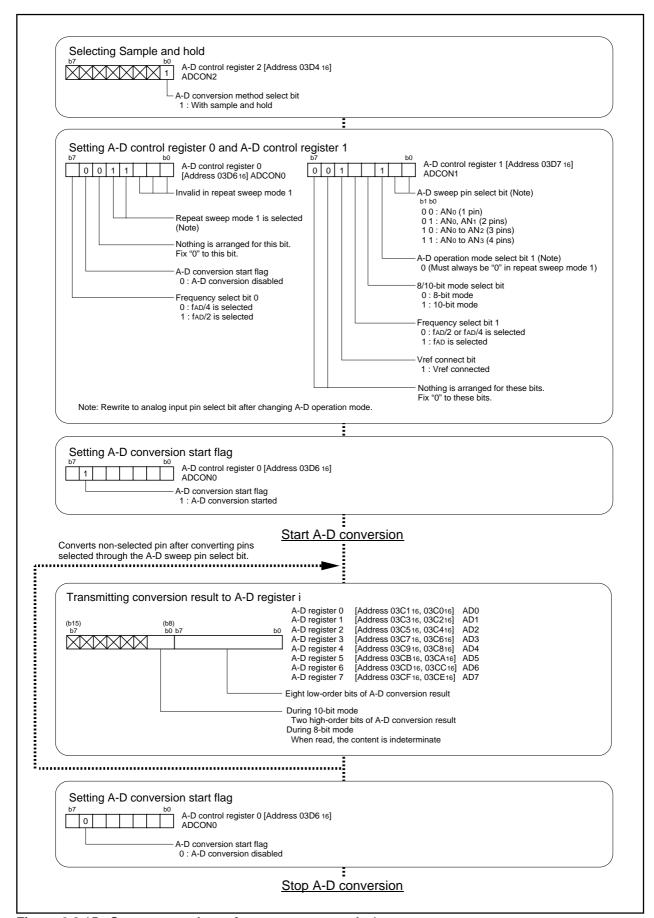

| 2.8 A-D Converter                                                                                       | 326       |

| 2.8.1 Overview                                                                                          | 326       |

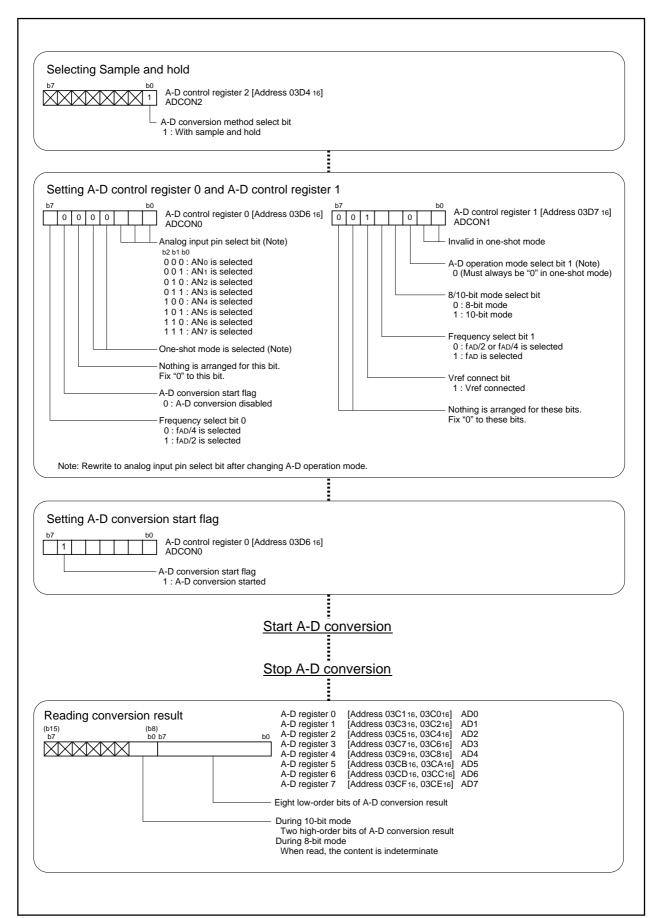

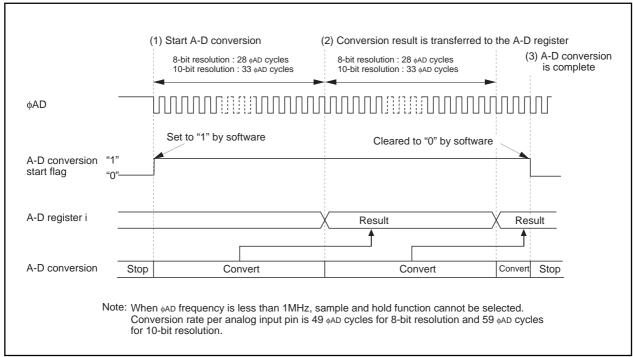

| 2.8.2 Operation of A-D converter (one-shot mode)                                                        | 332       |

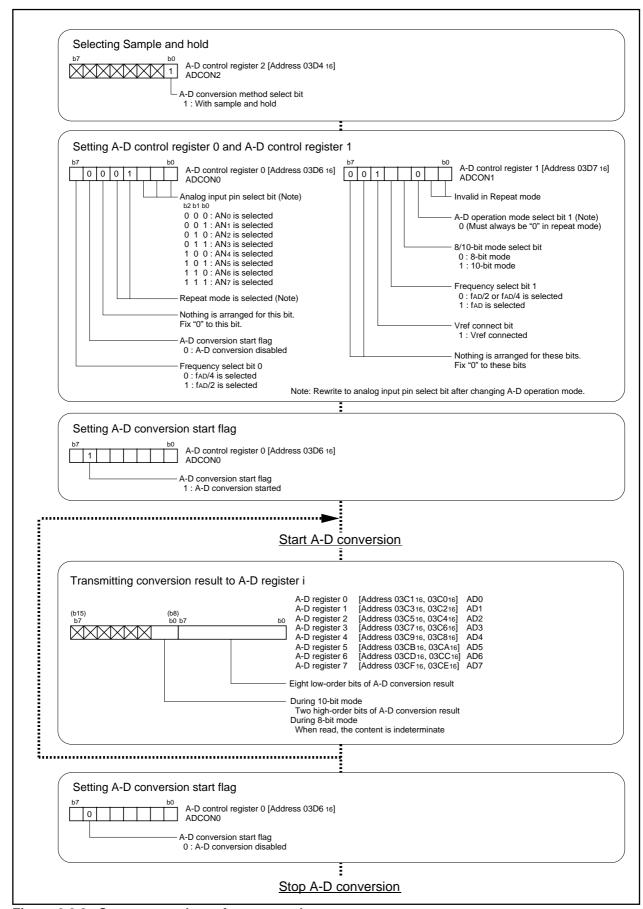

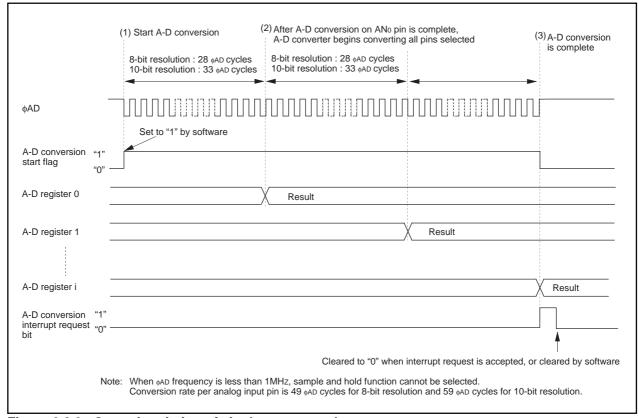

| 2.8.3 Operation of A-D Converter (in repeat mode)                                                       | 334       |

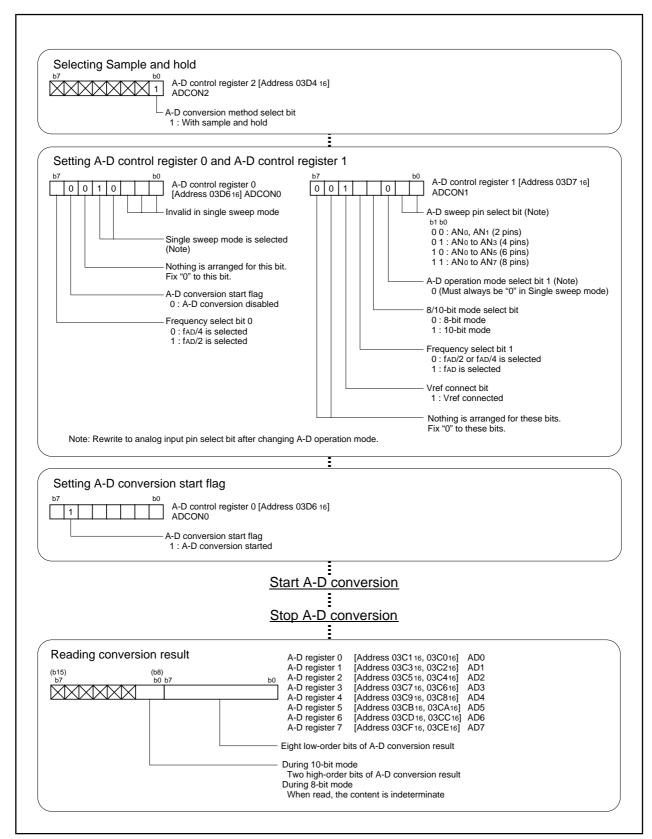

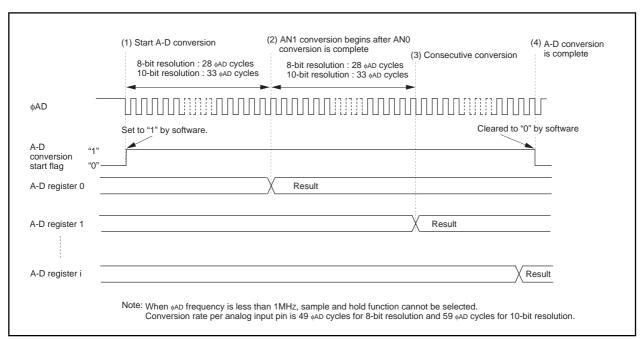

| 2.8.4 Operation of A-D Converter (in single sweep mode)                                                 | 336       |

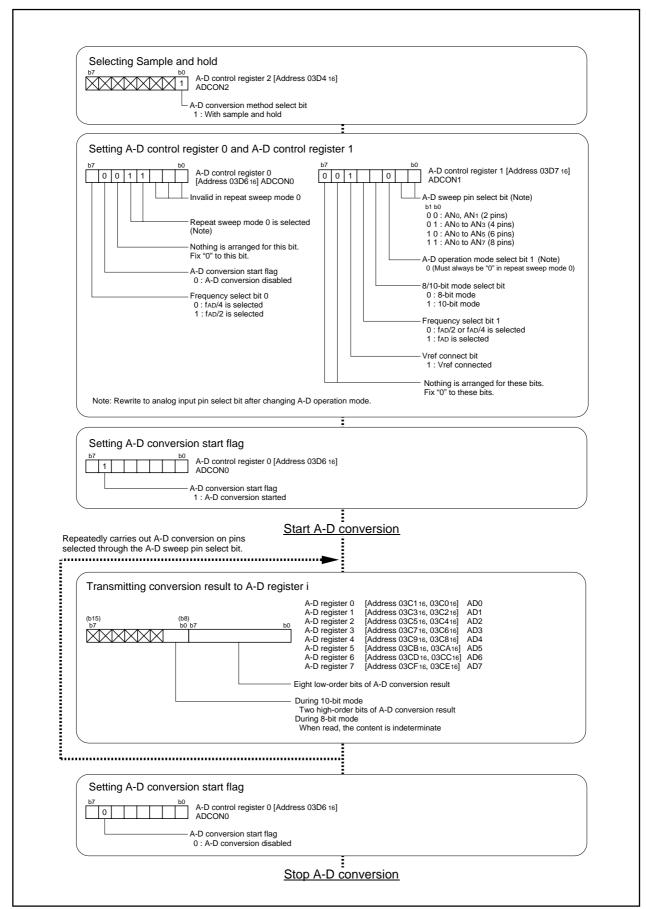

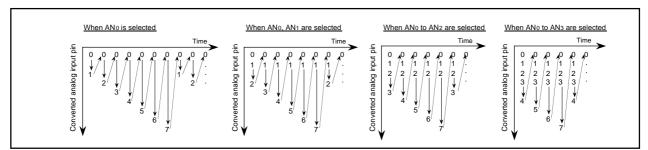

| 2.8.5 Operation of A-D Converter (in repeat sweep mode 0)                                               | 338       |

| 2.8.6 Operation of A-D Converter (in repeat sweep mode 1)                                               | 340       |

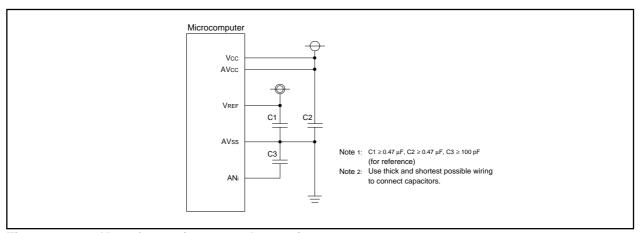

| 2.8.7 Precautions for A-D Converter                                                                     | 342       |

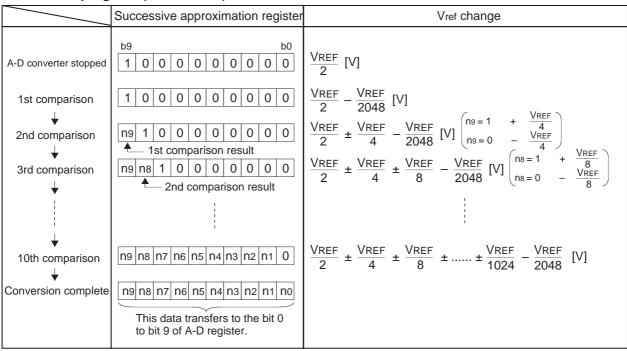

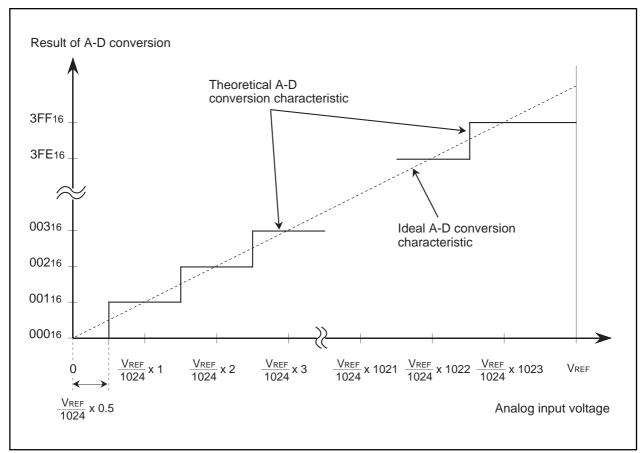

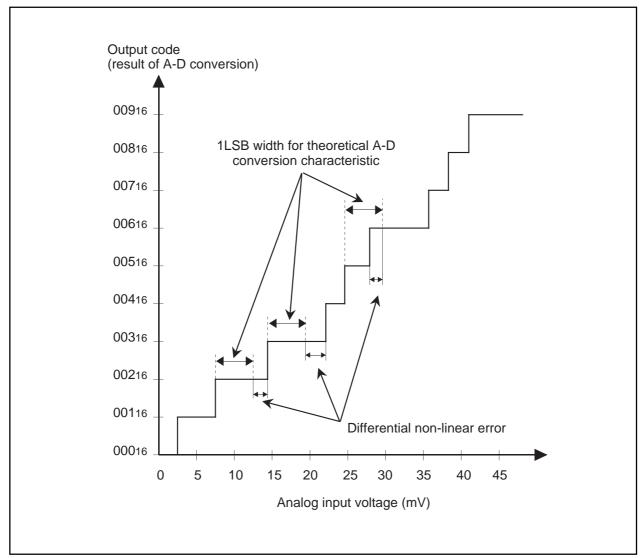

| 2.8.8 Method of A-D Conversion (10-bit mode)                                                            | 343       |

|                                                                                                         | 0.45      |

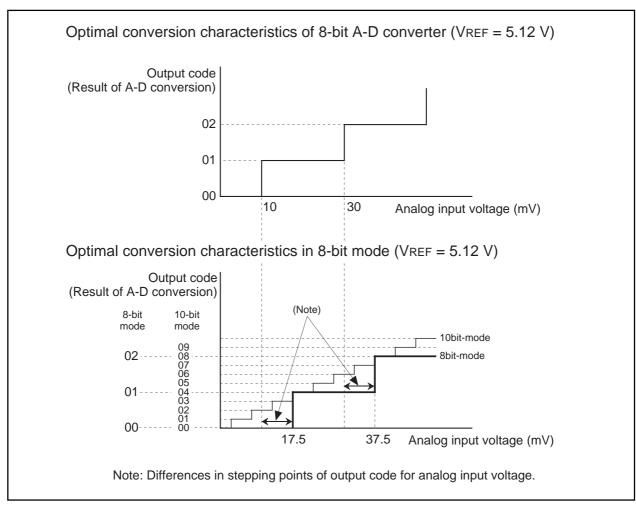

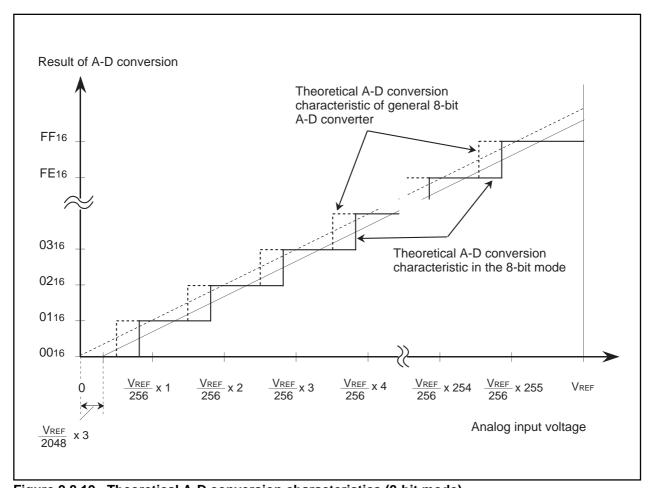

| 2.8.9 Method of A-D Conversion (8-bit mode)                                                             | 345       |

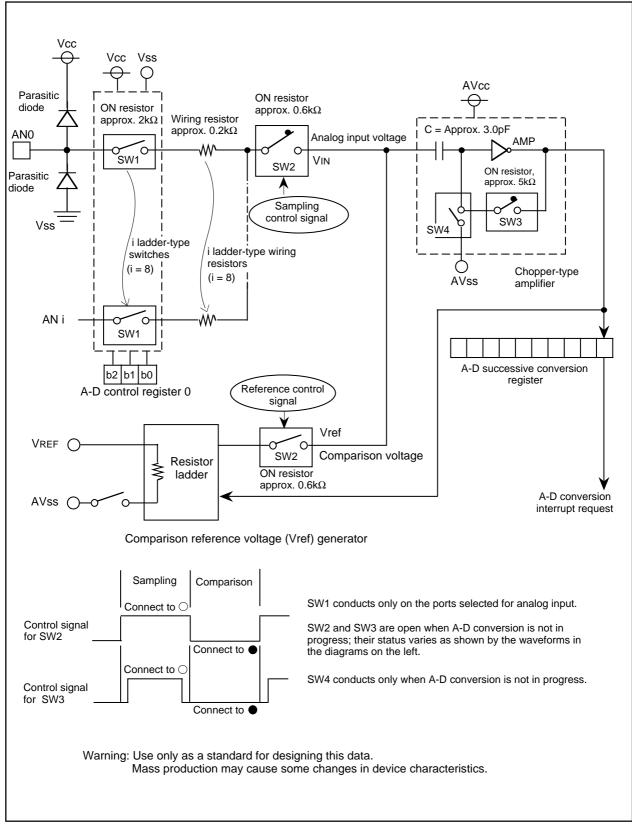

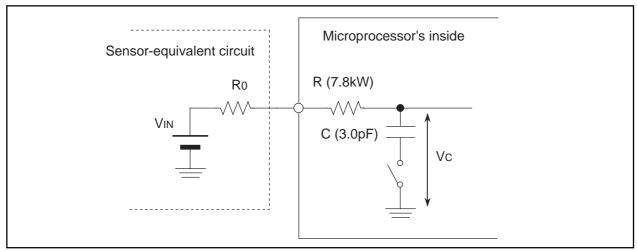

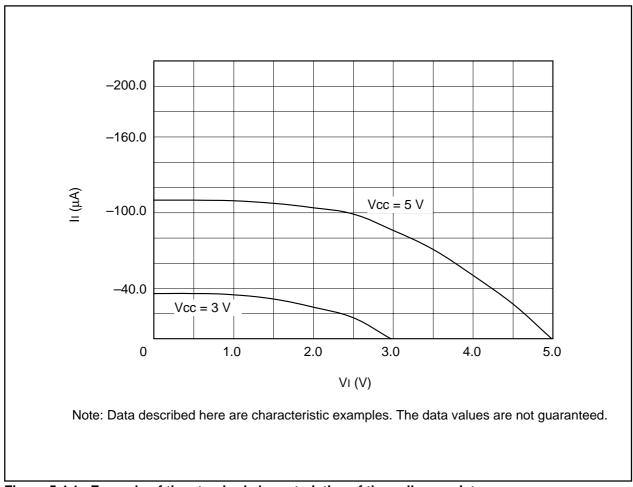

|   | 2.8.11 Internal Equivalent Circuit of Analog Input      | 349 |

|---|---------------------------------------------------------|-----|

|   | 2.8.12 Sensor's Output Impedance under A-D Conversion   | 350 |

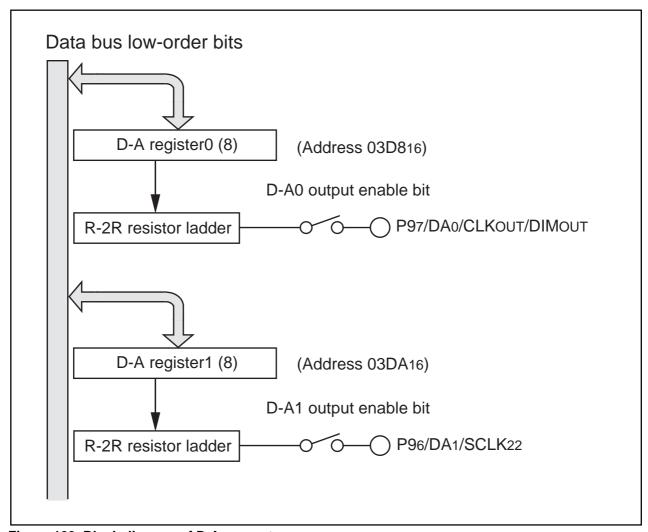

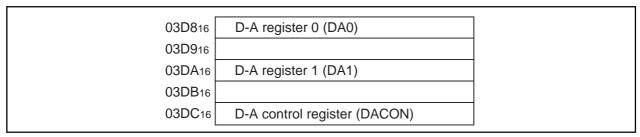

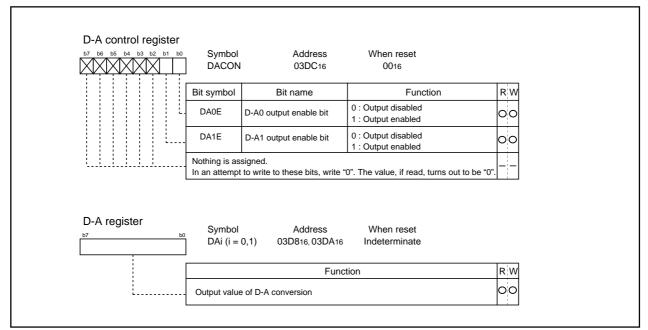

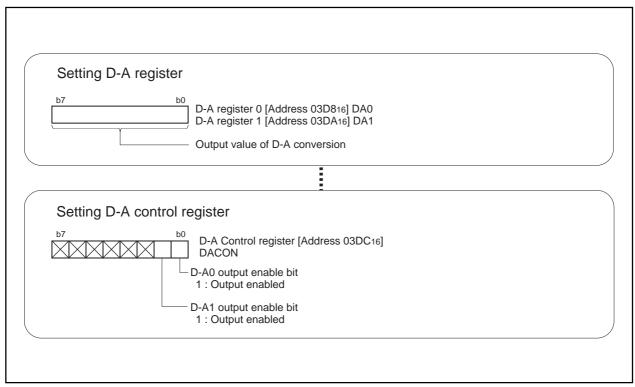

|   | 2.9 D-A Converter                                       | 352 |

|   | 2.9.1 Overview                                          | 352 |

|   | 2.9.2 D-A Converter Operation                           | 353 |

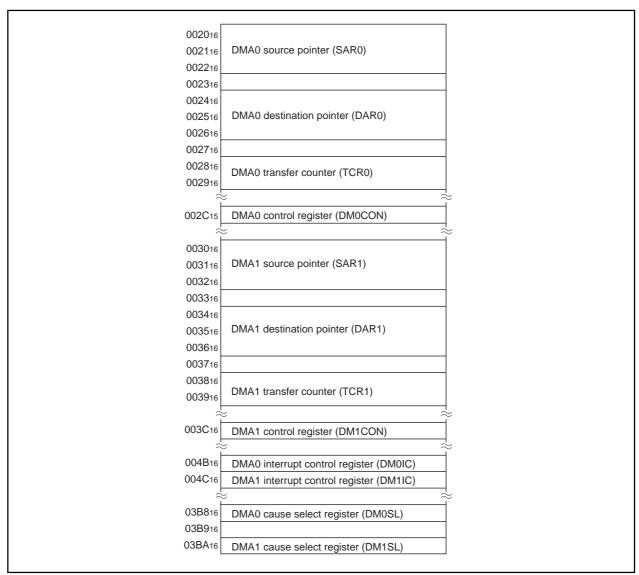

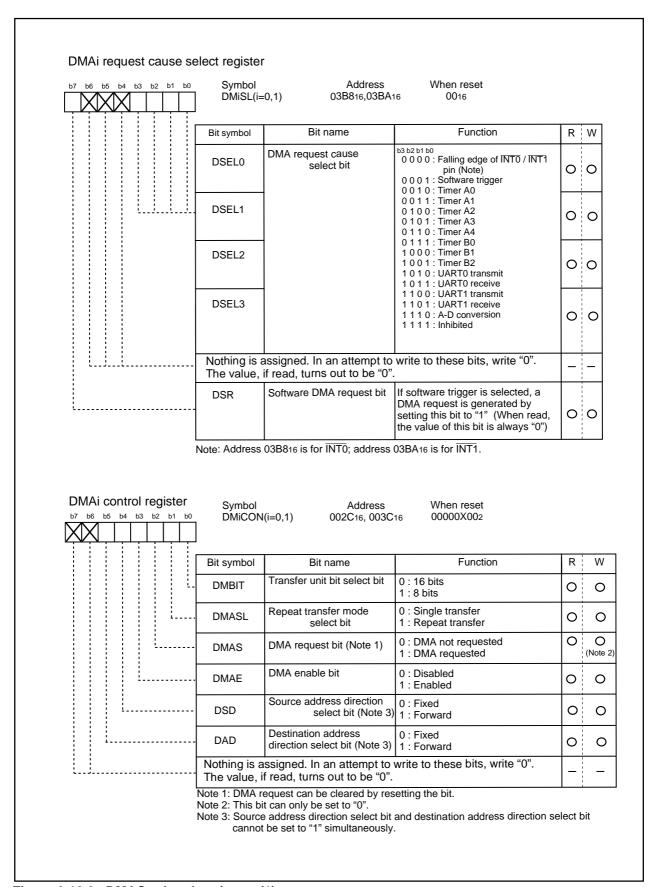

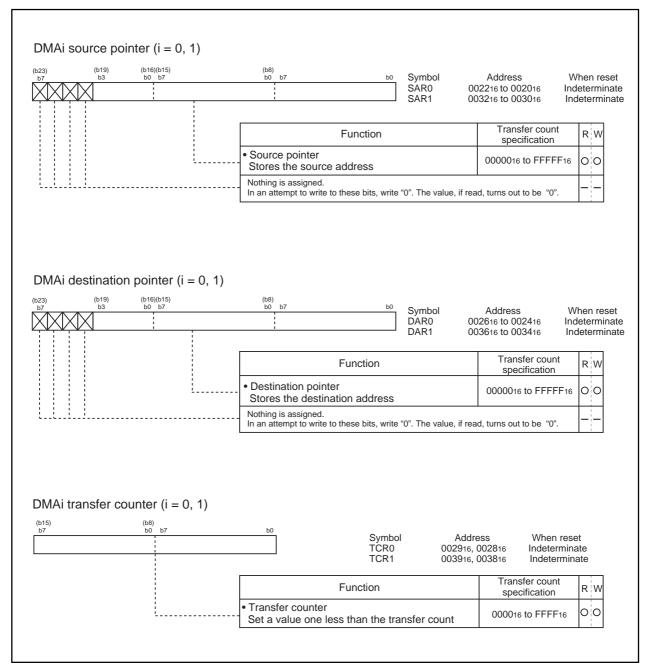

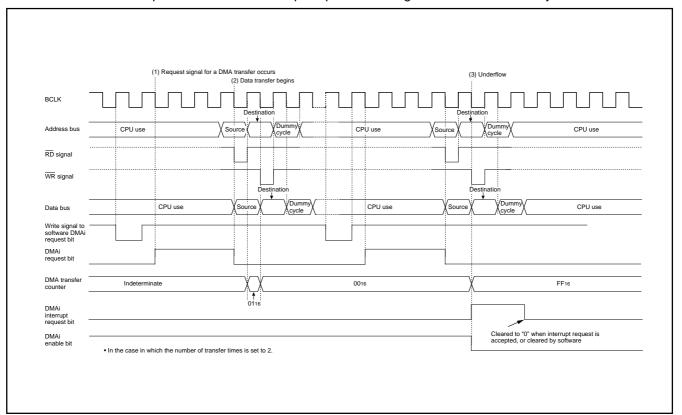

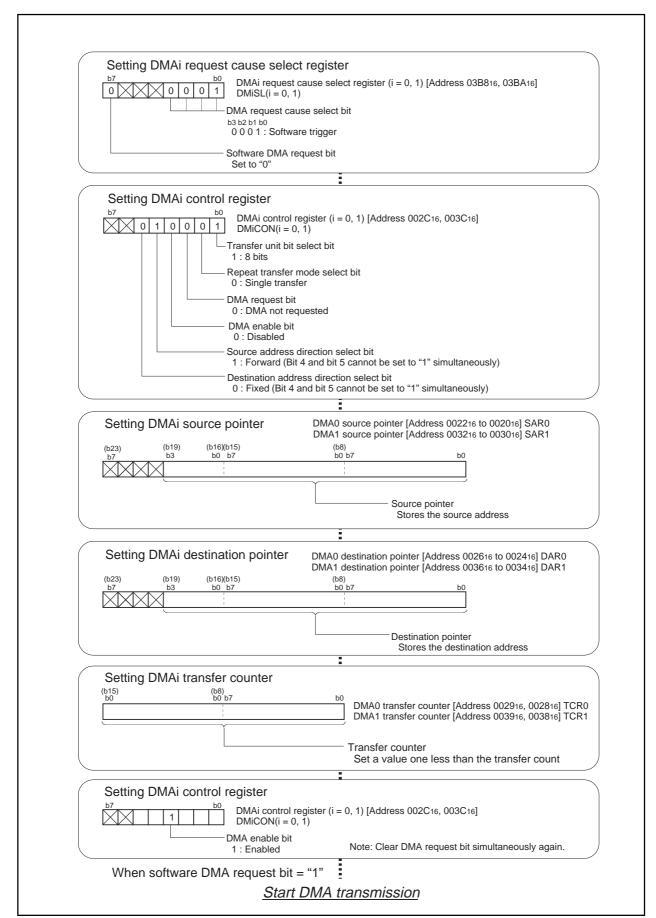

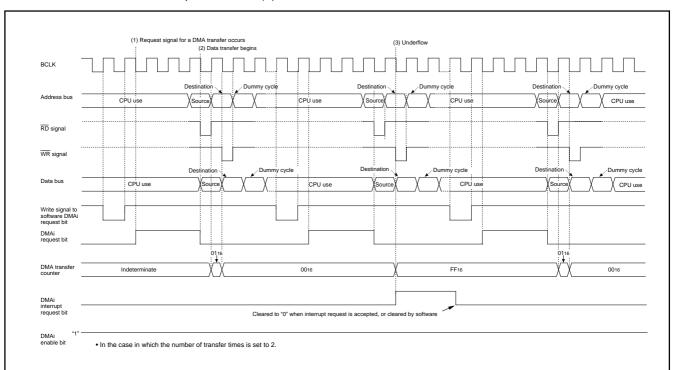

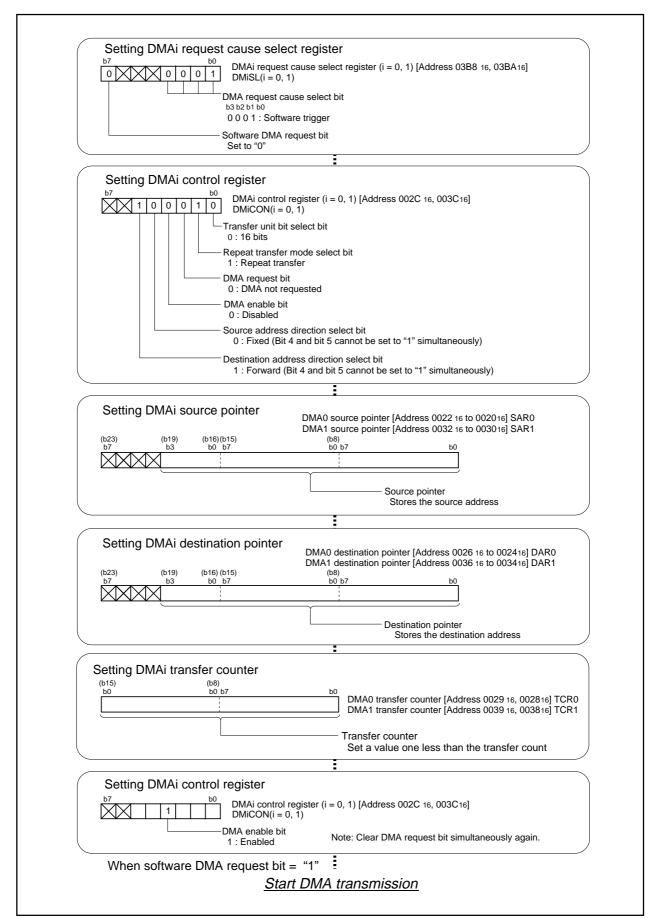

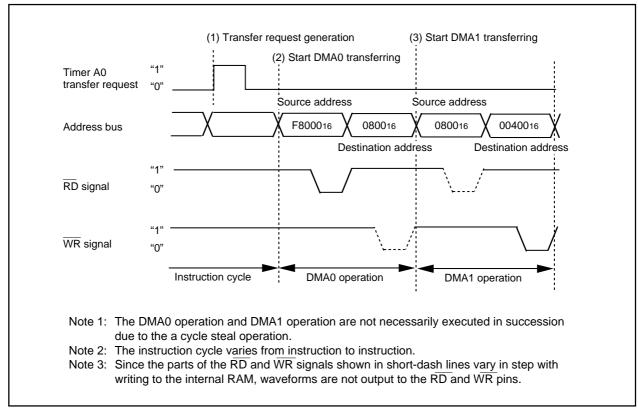

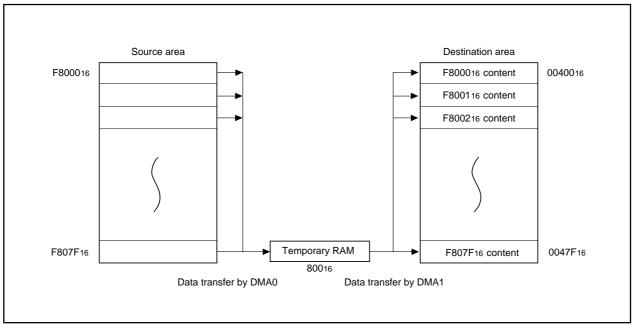

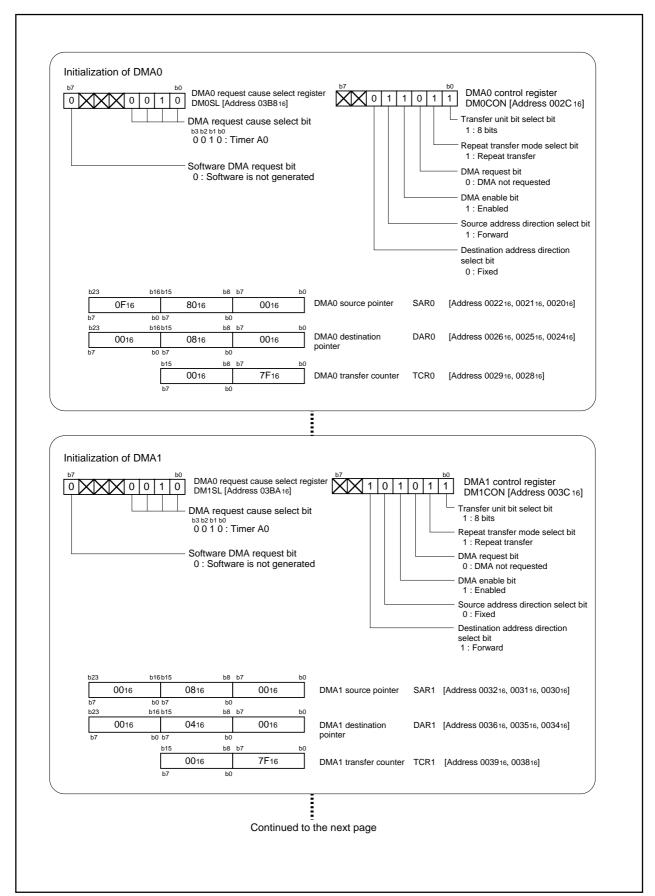

|   | 2.10 DMAC                                               | 354 |

|   | 2.10.1 Overview                                         | 354 |

|   | 2.10.2 Operation of DMAC (one-shot transfer mode)       | 358 |

|   | 2.10.3 Operation of DMAC (repeated transfer mode)       | 360 |

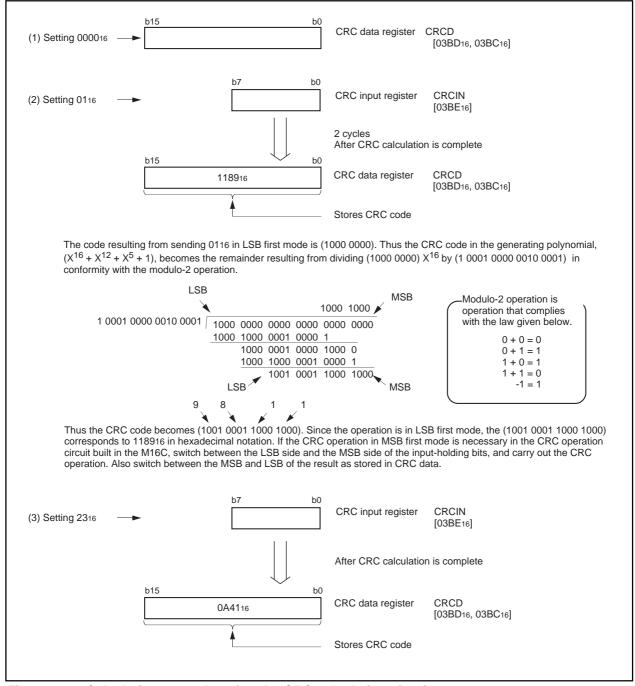

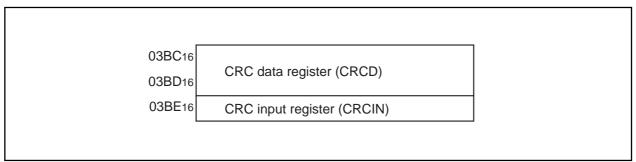

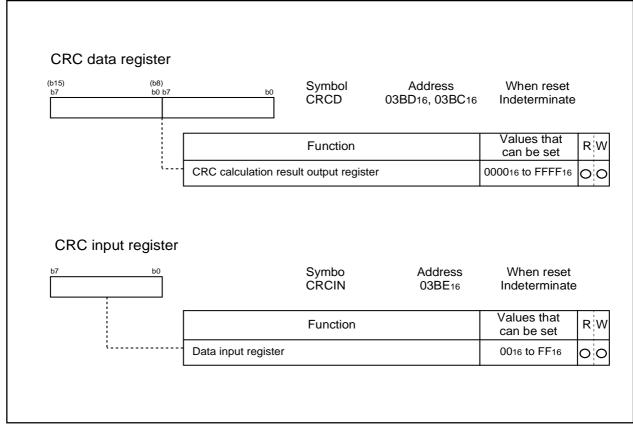

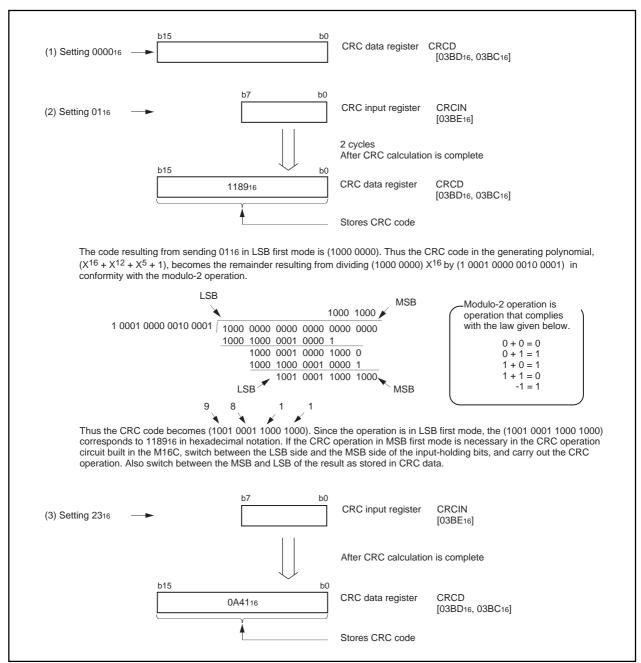

|   | 2.11 CRC Calculation Circuit                            | 362 |

|   | 2.11.1 Overview                                         | 362 |

|   | 2.11.2 Operation of CRC Calculation Circuit             | 363 |

|   | 2.12 Watchdog Timer                                     | 364 |

|   | 2.12.1 Overview                                         | 364 |

|   | 2.12.2 Operation of Watchdog Timer                      | 366 |

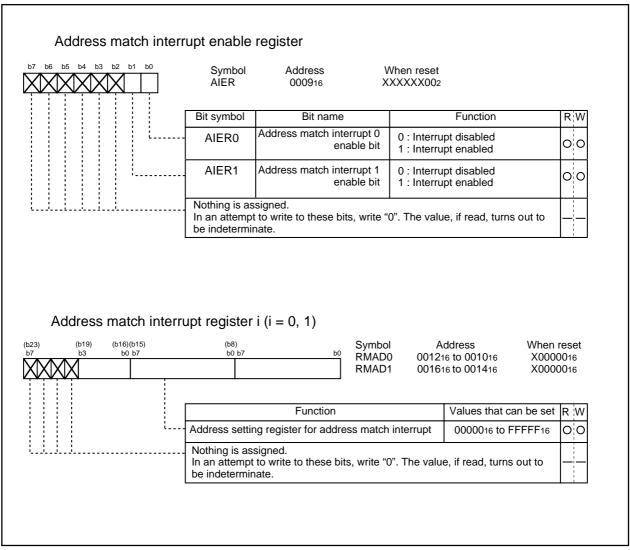

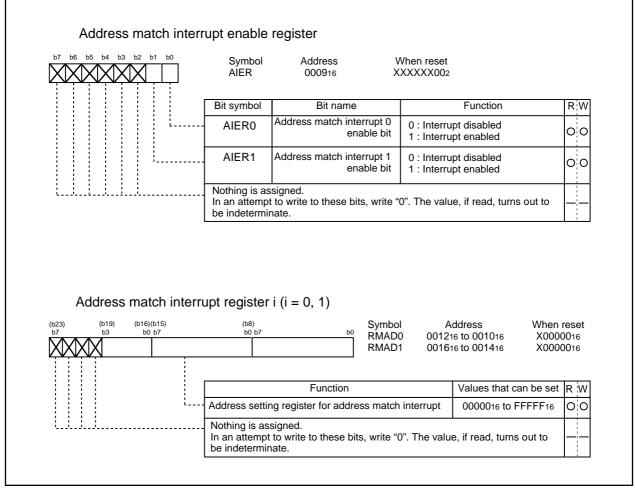

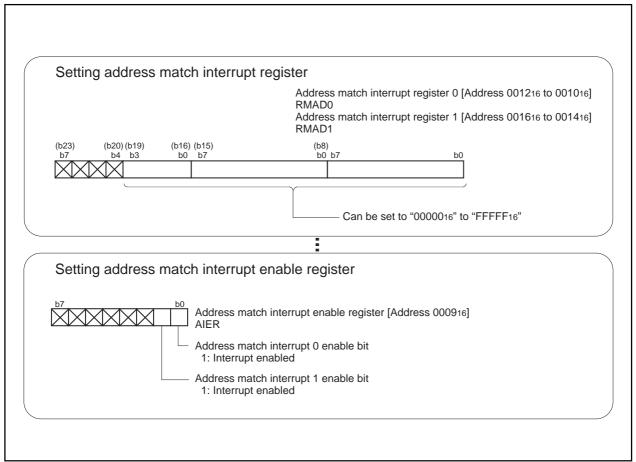

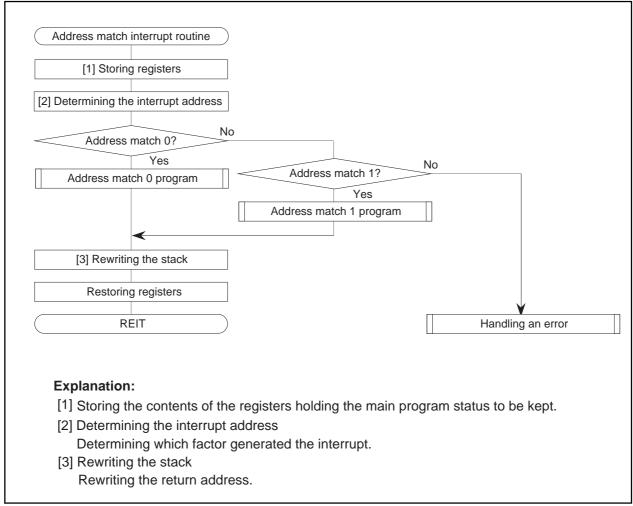

|   | 2.13 Address Match Interrupt                            | 368 |

|   | 2.13.1 Overview                                         | 368 |

|   | 2.13.2 Operation of Address Match Interrupt             | 370 |

|   | 2.14 Power Control                                      | 372 |

|   | 2.14.1 Overview                                         | 372 |

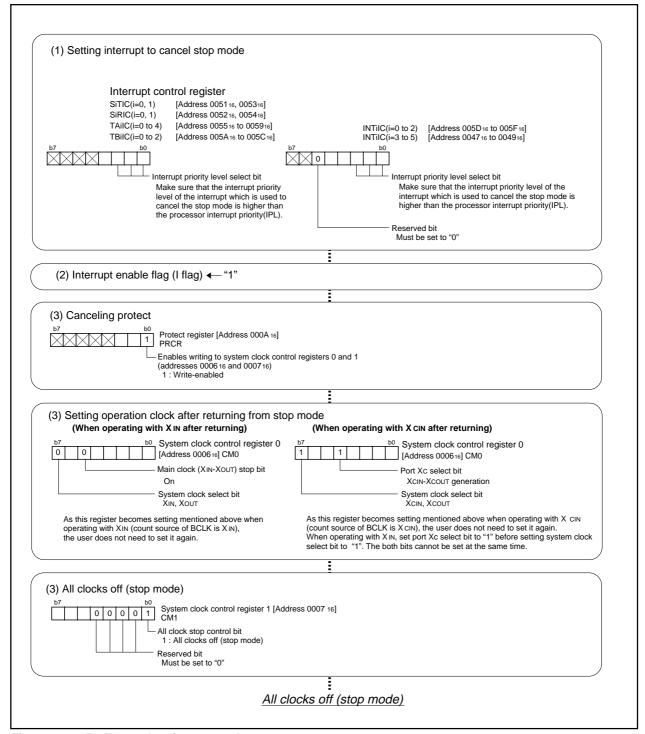

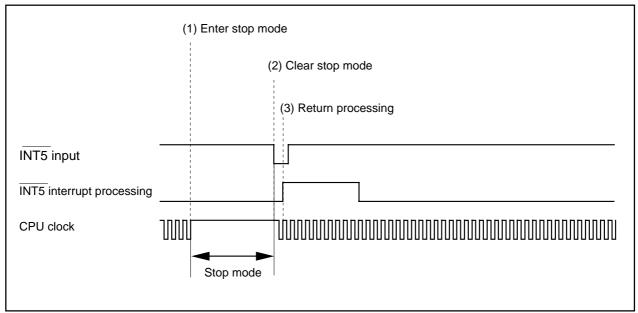

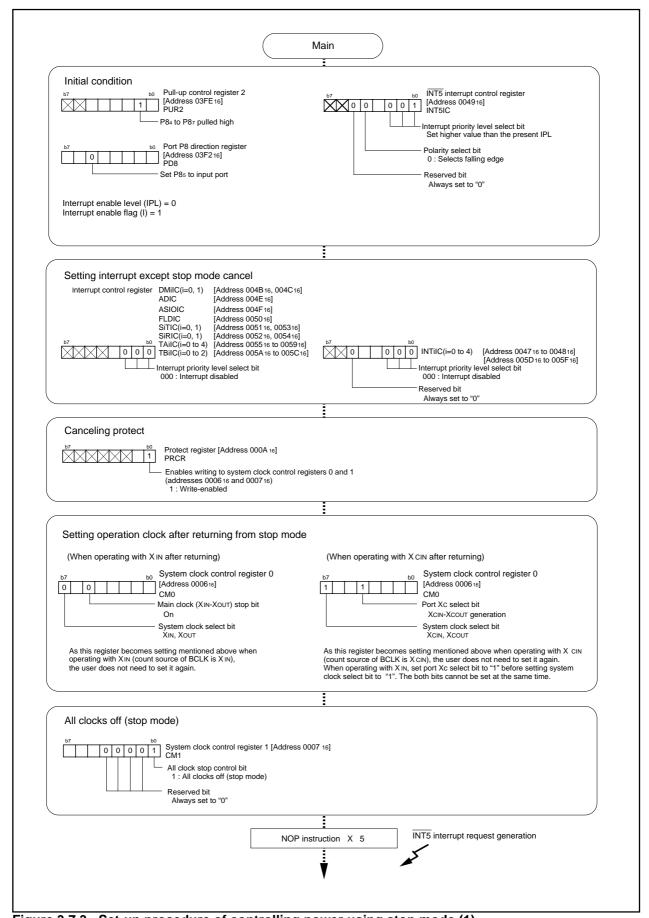

|   | 2.14.2 Stop Mode Set-Up                                 | 377 |

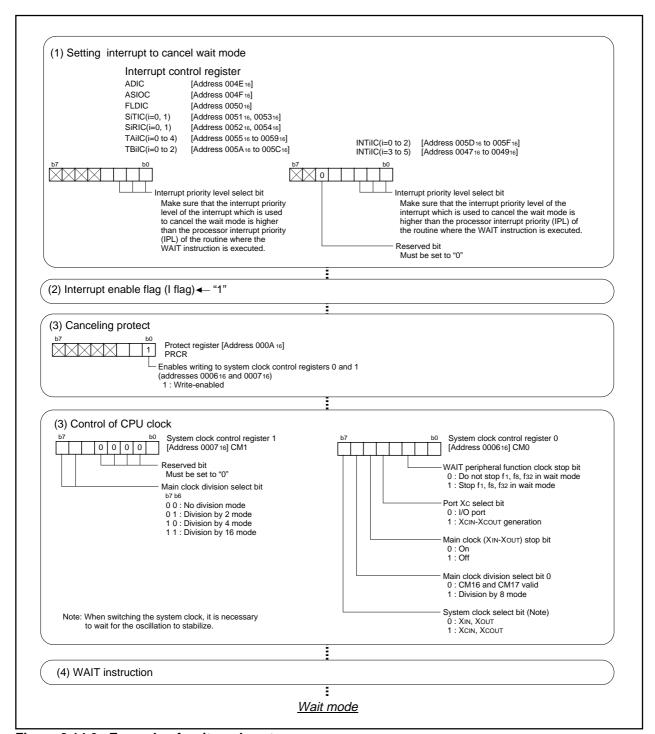

|   | 2.14.3 Wait Mode Set-Up                                 | 378 |

|   | 2.14.4 Precautions in Power Control                     | 379 |

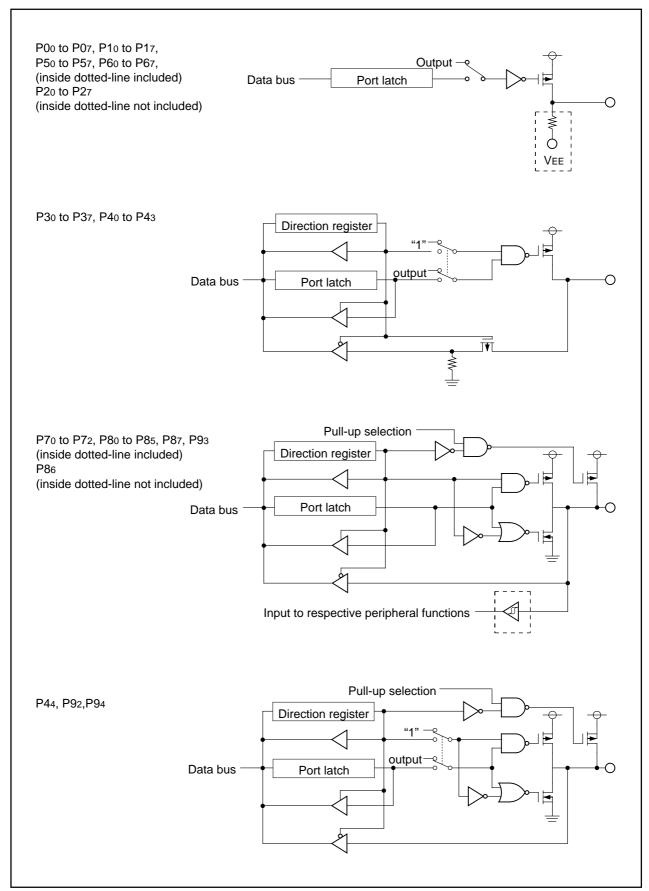

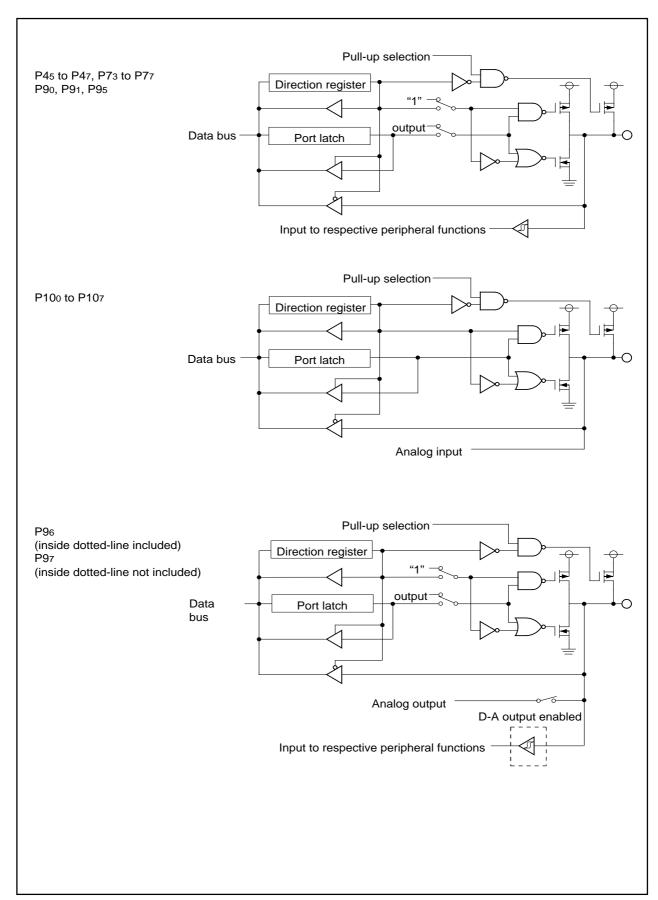

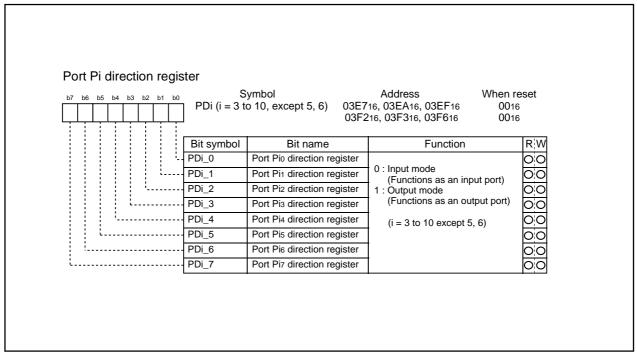

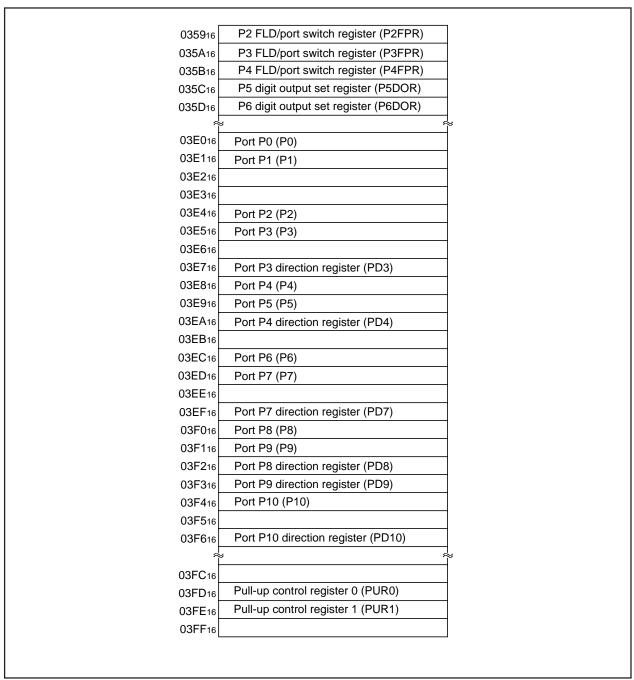

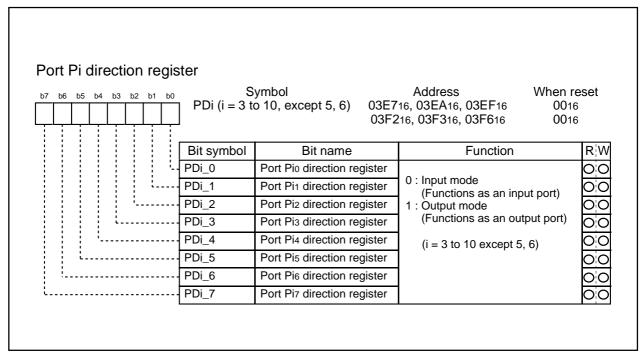

|   | 2.15 Programmable I/O Ports                             | 380 |

|   | 2.15.1 Overview                                         | 380 |

| ( | Chapter 3 Examples of Peripheral functions Applications |     |

|   | 3.1 Long-Period Timers                                  | 388 |

|   | 3.2 Variable-Period Variable-Duty PWM Output            | 392 |

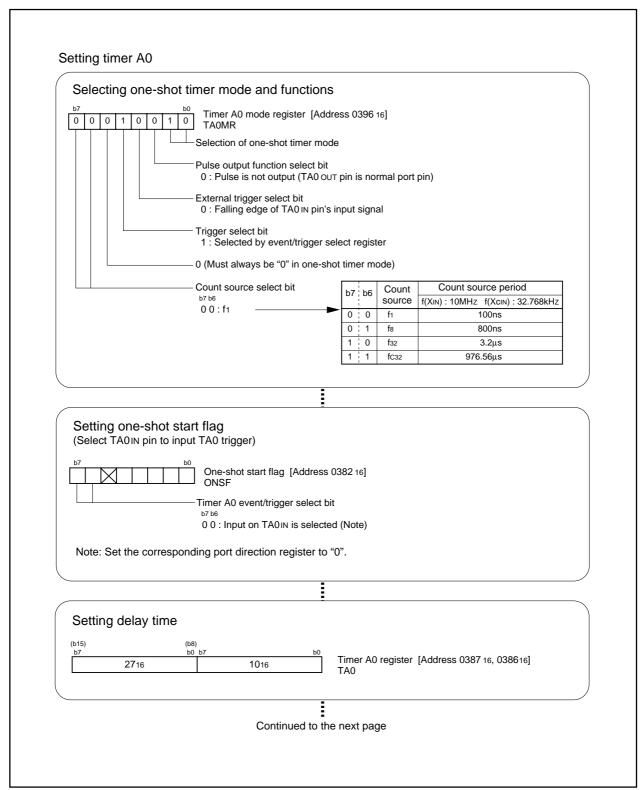

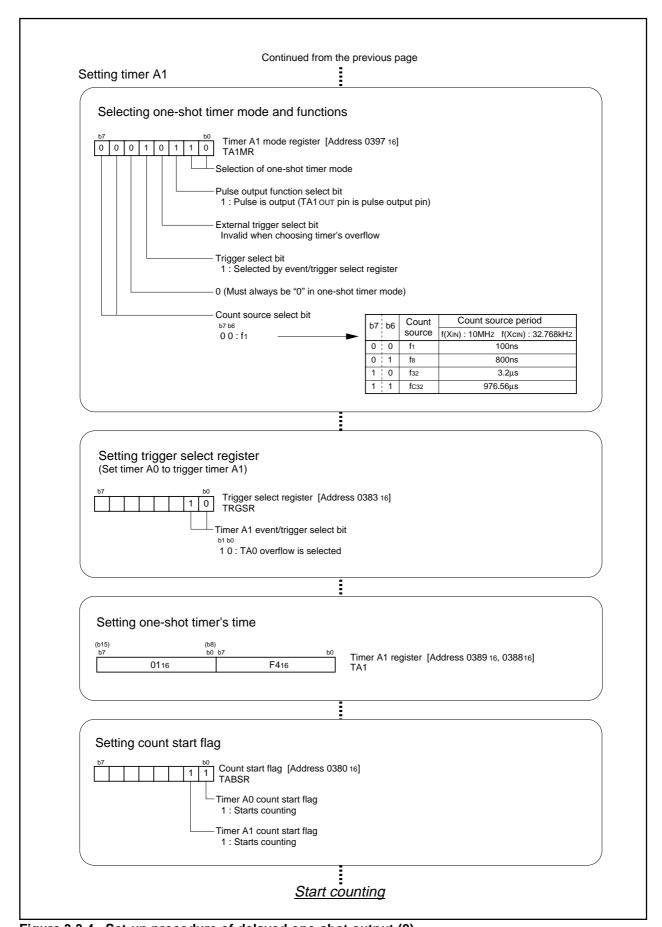

|   | 3.3 Delayed One-Shot Output                             | 396 |

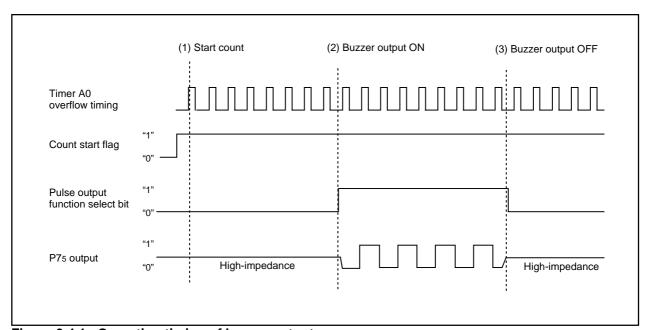

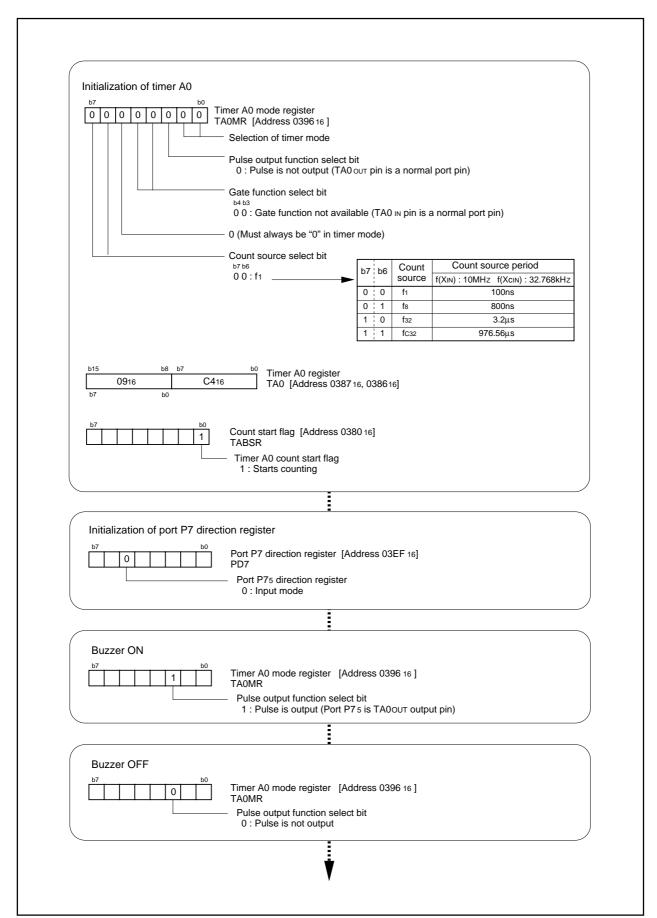

|   | 3.4 Buzzer Output                                       | 400 |

|   | 3.5 Solution for External Interrupt Pins Shortage       | 402 |

|   | 3.6 Memory to Memory DMA Transfer                       | 404 |

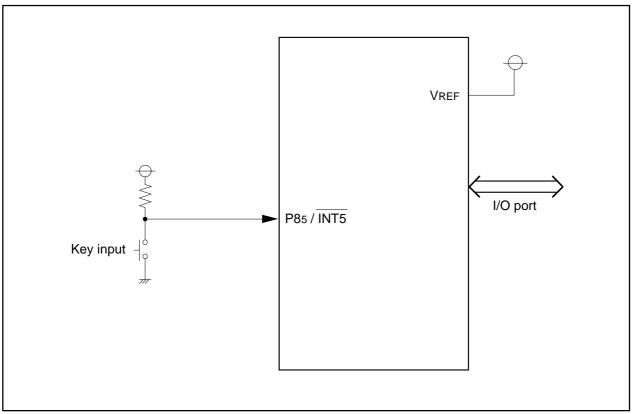

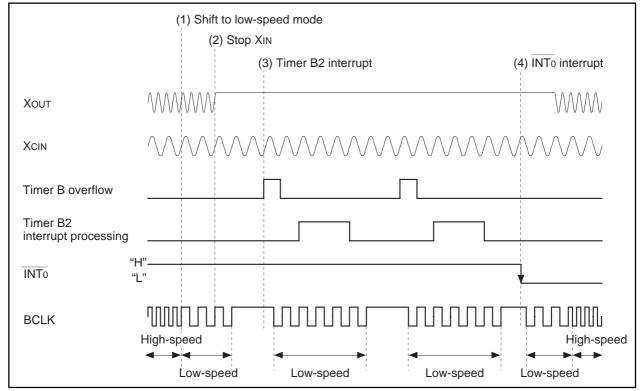

|   | 3.7 Controlling Power Using Stop Mode                   | 408 |

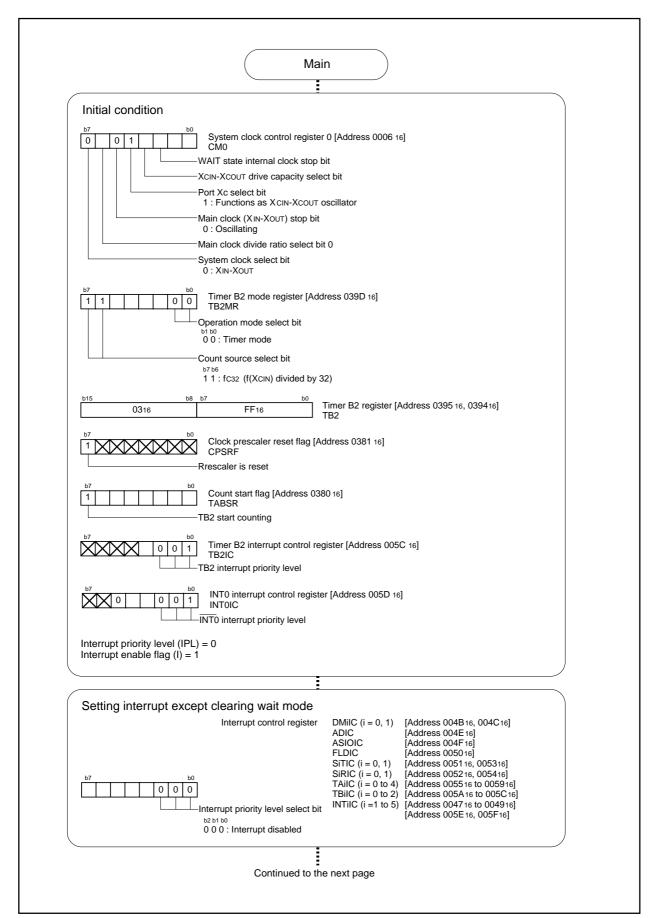

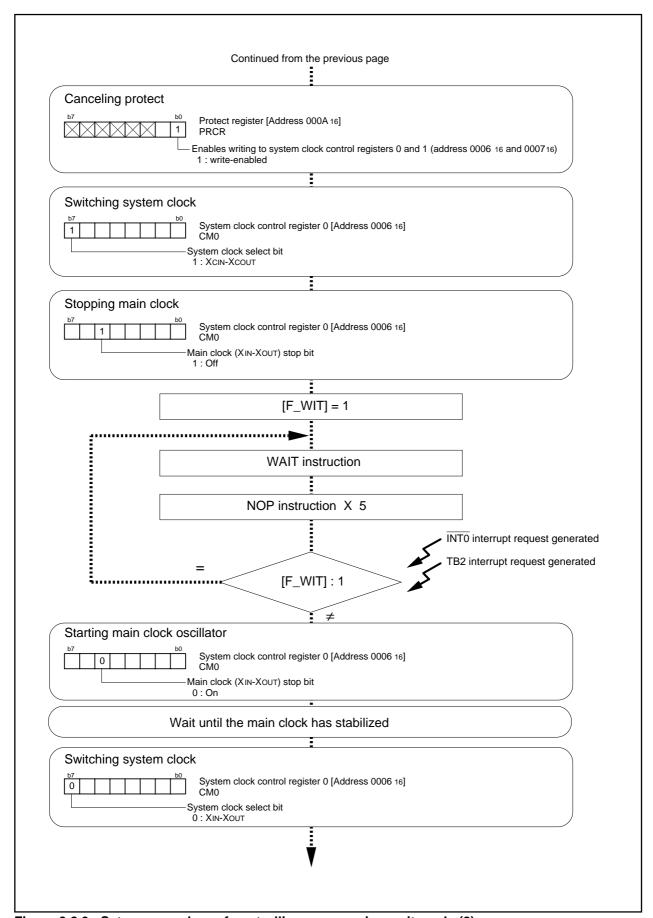

|   | 3.8 Controling Power Using Wait Mode                    | 412 |

## Chapter 4 Interrupt\_\_\_\_\_

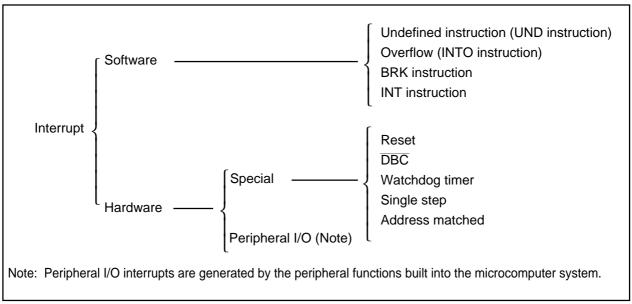

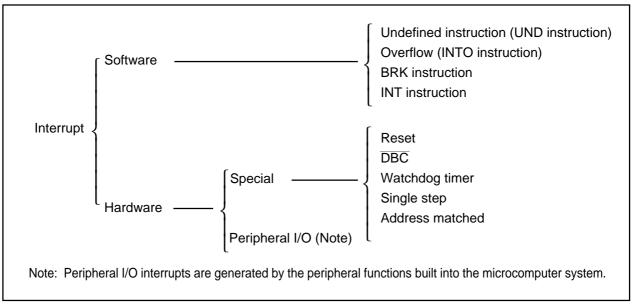

| 4.1 Overview of Interrupt                                                              | 408 |

|----------------------------------------------------------------------------------------|-----|

| 4.1.1 Type of Interrupts                                                               | 408 |

| 4.1.2 Software Interrupts                                                              | 409 |

| 4.1.3 Hardware Interrupts                                                              | 420 |

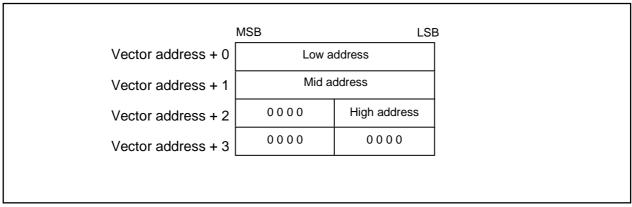

| 4.1.4 Interrupts and Interrupt Vector Tables                                           | 421 |

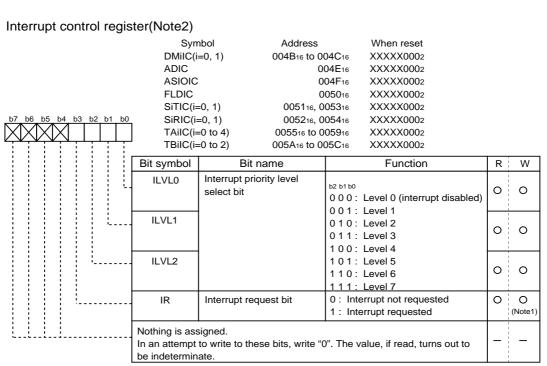

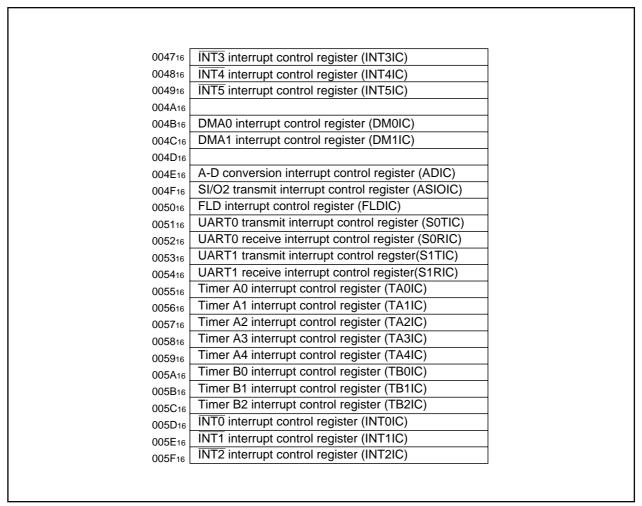

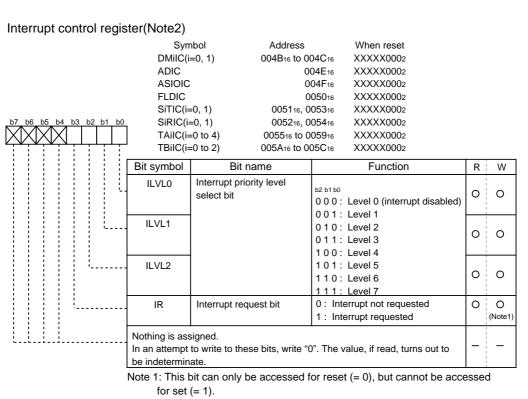

| 4.2 Interrupt Control                                                                  | 423 |

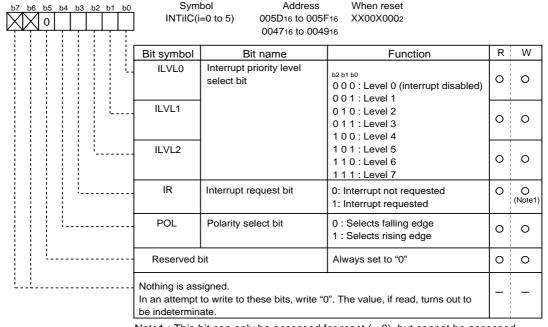

| 4.2.1 Interrupt Enable Flag                                                            | 425 |

| 4.2.2 Interrupt Request Bit                                                            | 425 |

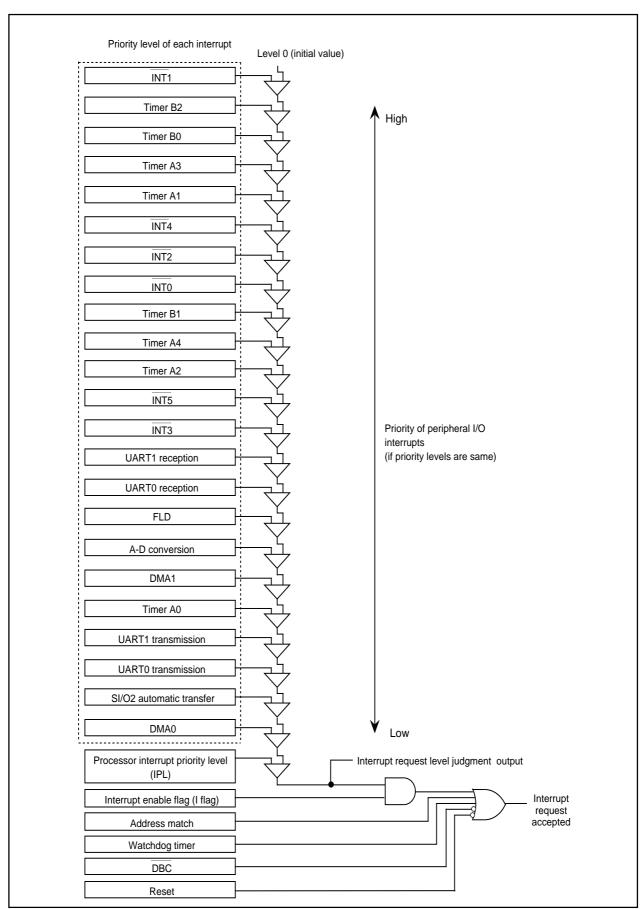

| 4.2.3 Interrupt Priority Level Select Bit and Processor Interrupt Priority Level (IPL) | 426 |

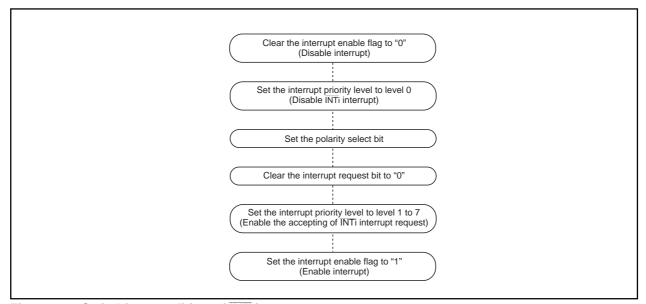

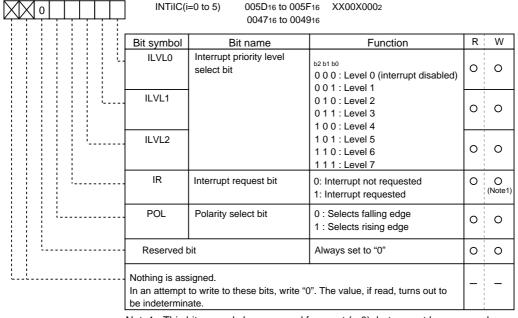

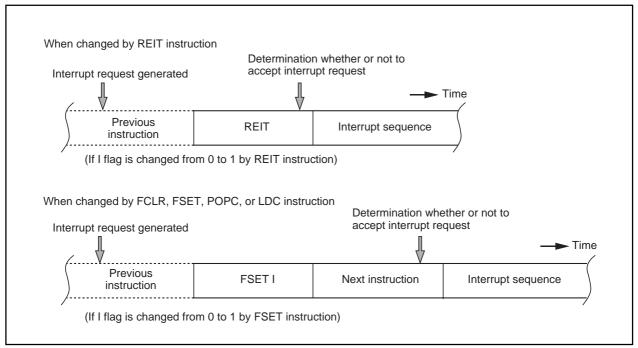

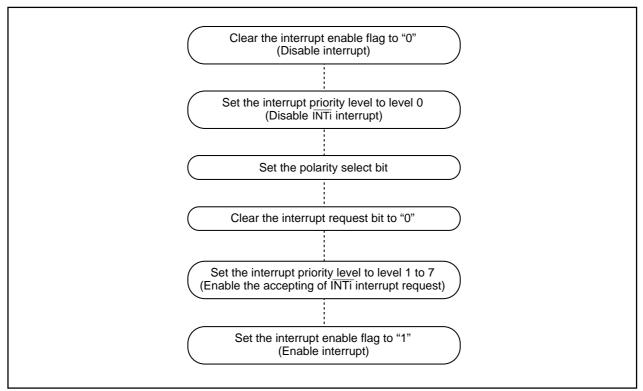

| 4.2.4 Rewrite the interrupt control register                                           | 427 |

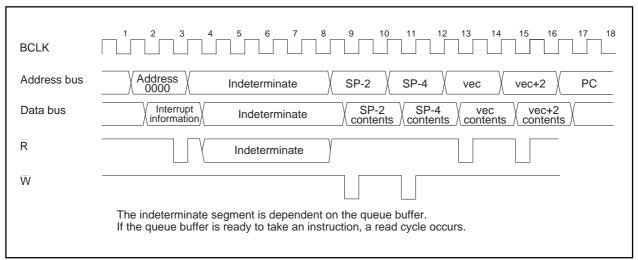

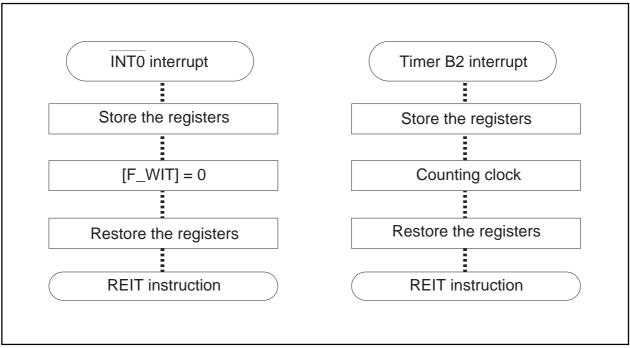

| 4.3 Interrupt Sequence                                                                 | 428 |

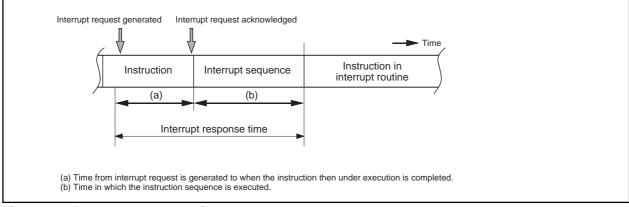

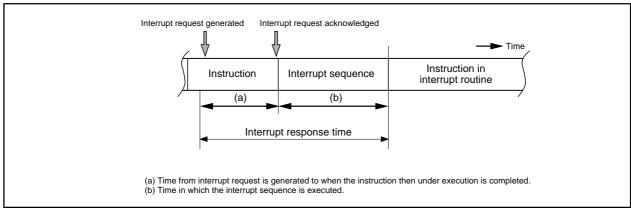

| 4.3.1 Interrupt Response Time                                                          | 428 |

| 4.3.2 Variation of IPL when Interrupt Request is Accepted                              | 429 |

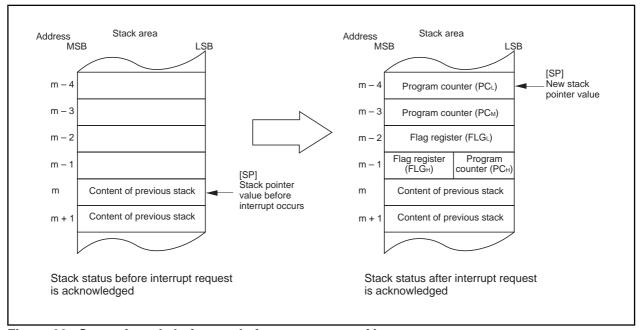

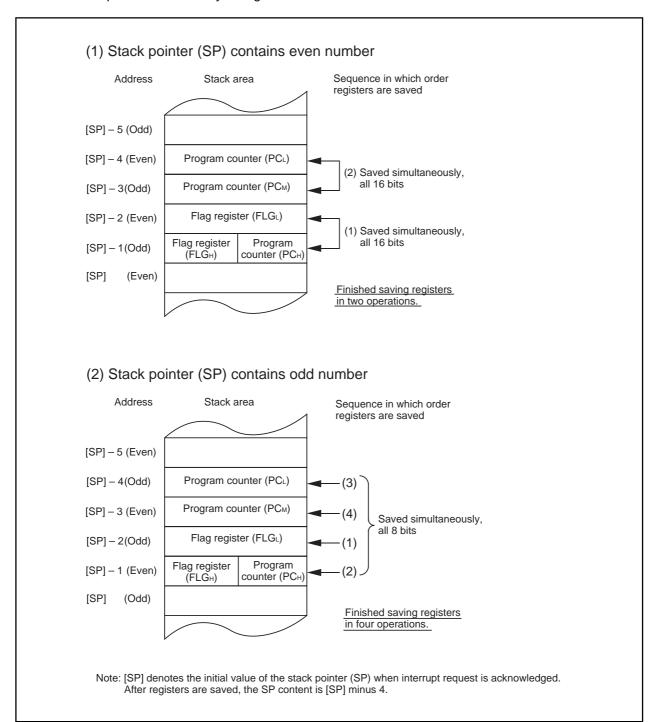

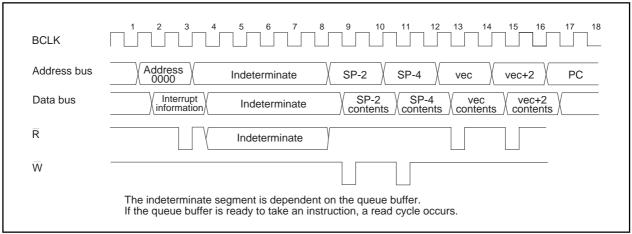

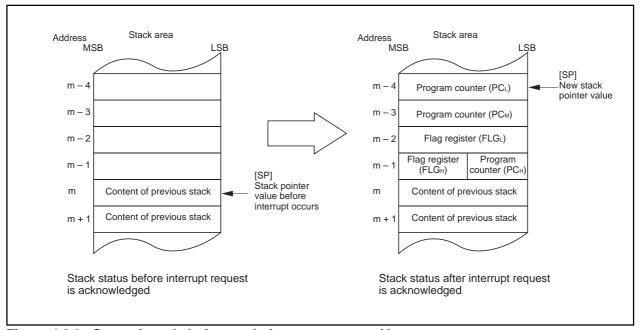

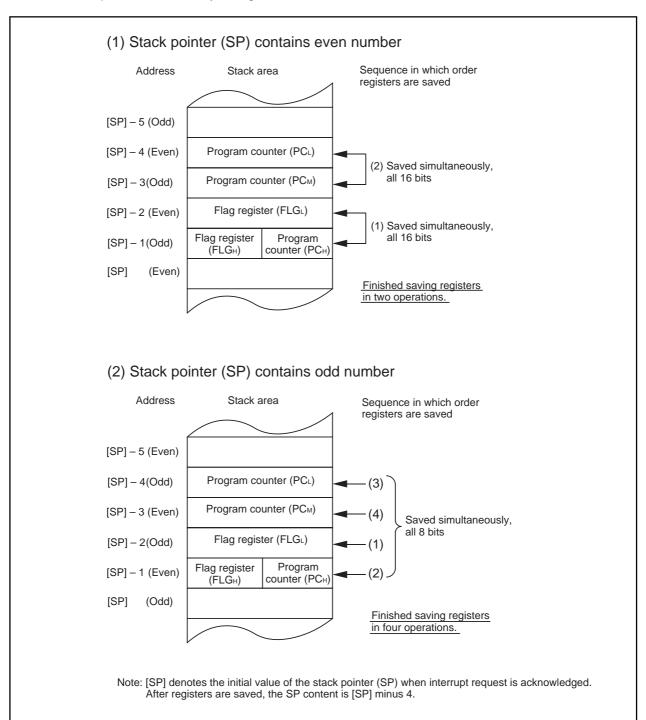

| 4.3.3 Saving Registers                                                                 | 430 |

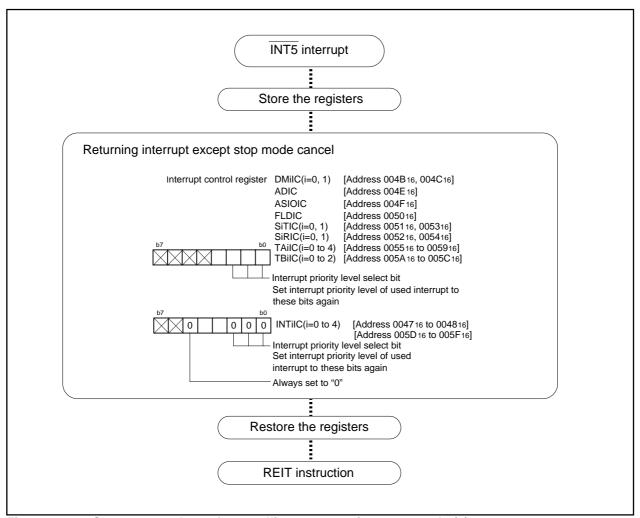

| 4.4 Returning from an Interrupt Routine                                                | 432 |

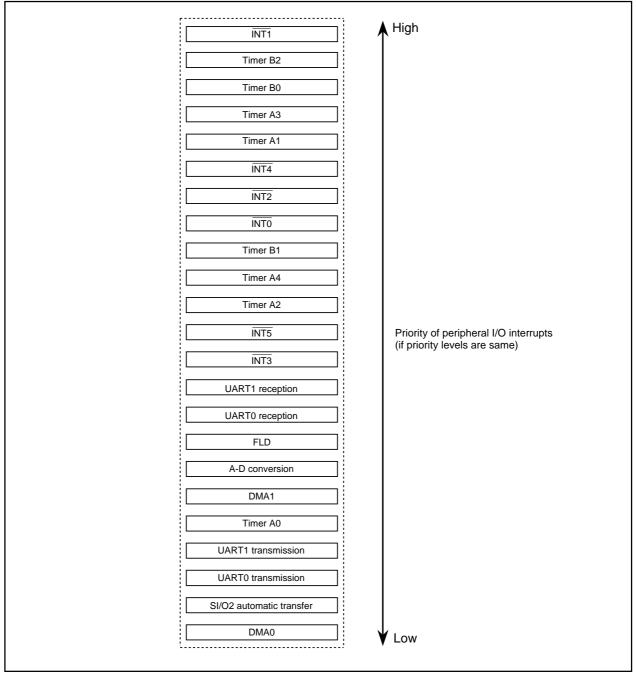

| 4.5 Interrupt Priority                                                                 | 432 |

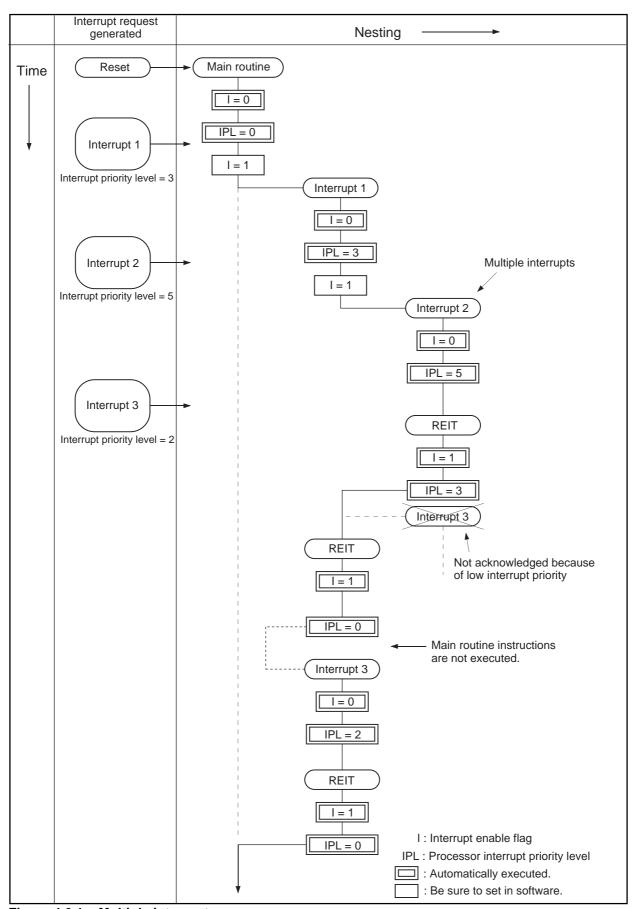

| 4.6 Multiple Interrupts                                                                | 434 |

| 4.7 Precautions for Interrupts                                                         | 436 |

| Chapter 5 Standard Characteristics                                                     |     |

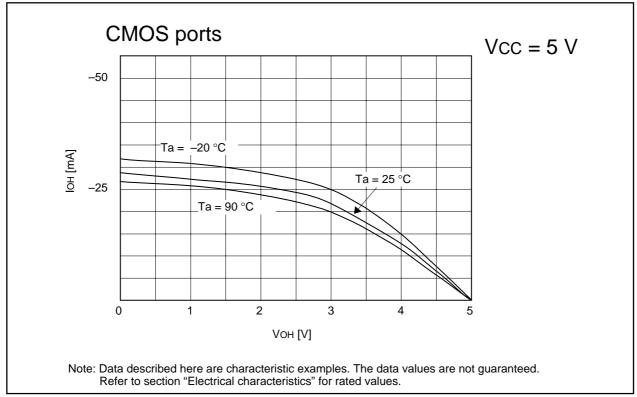

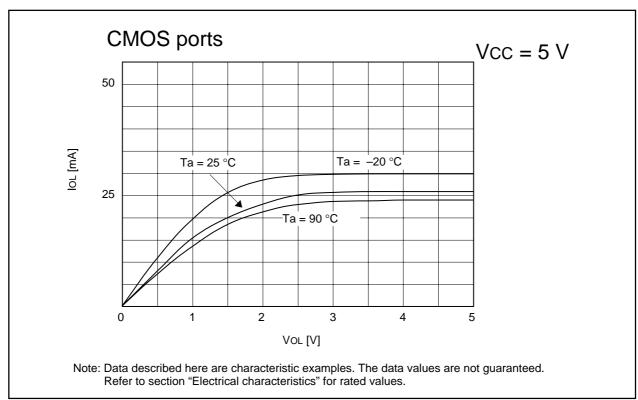

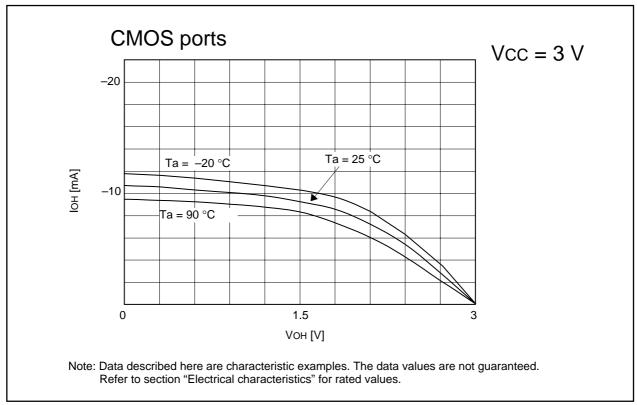

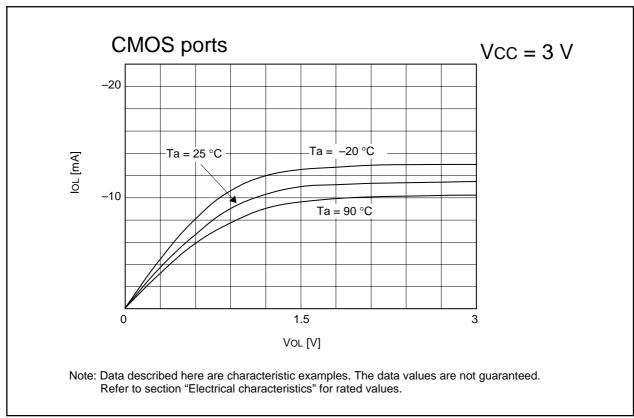

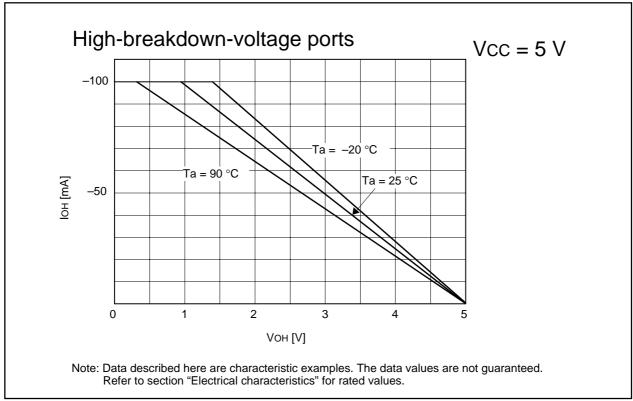

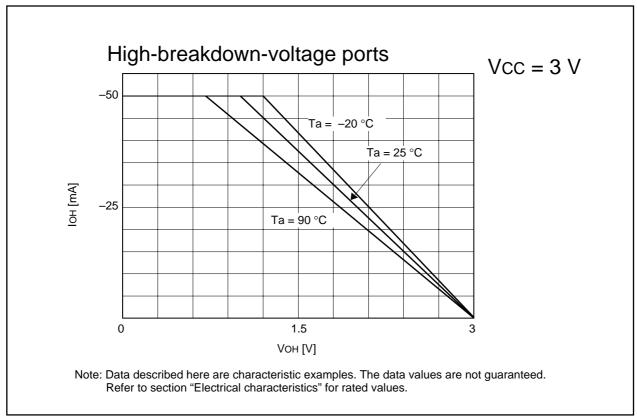

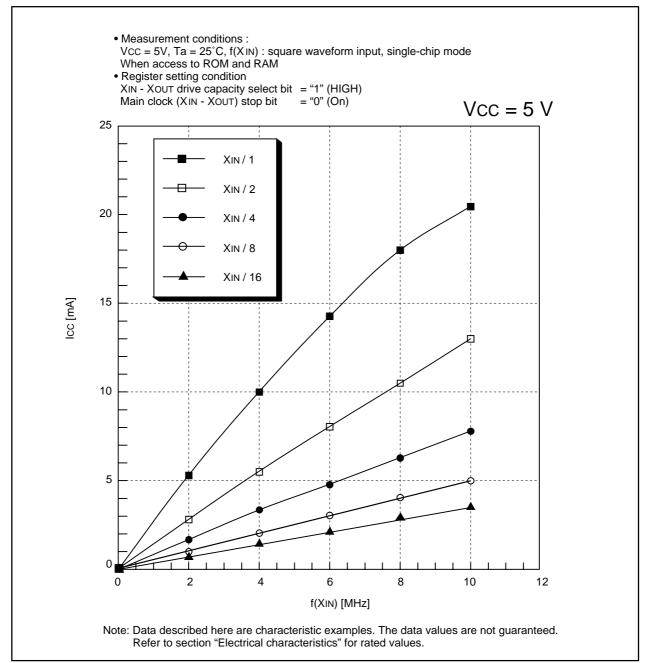

| 5.1 Standard DC Characteristics                                                        | 440 |

| 5.1.1 Standard Ports Characteristics                                                   | 440 |

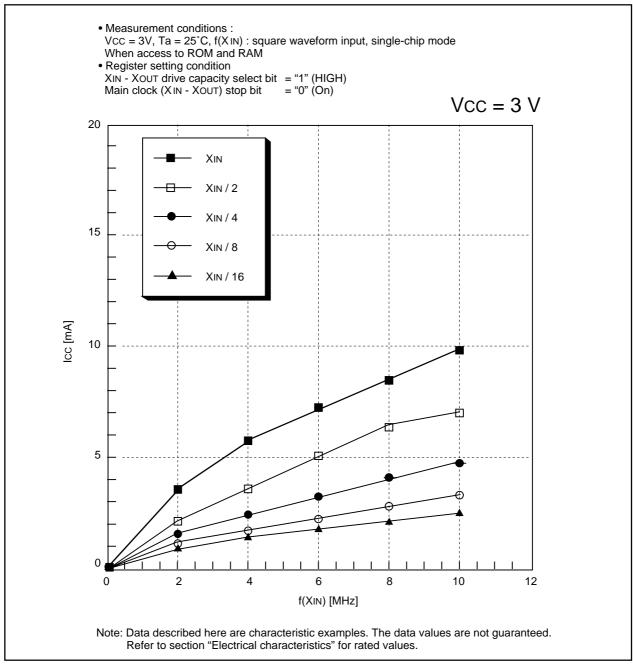

| 5.1.2 Characteristics of ICC-f(XIN)                                                    | 444 |

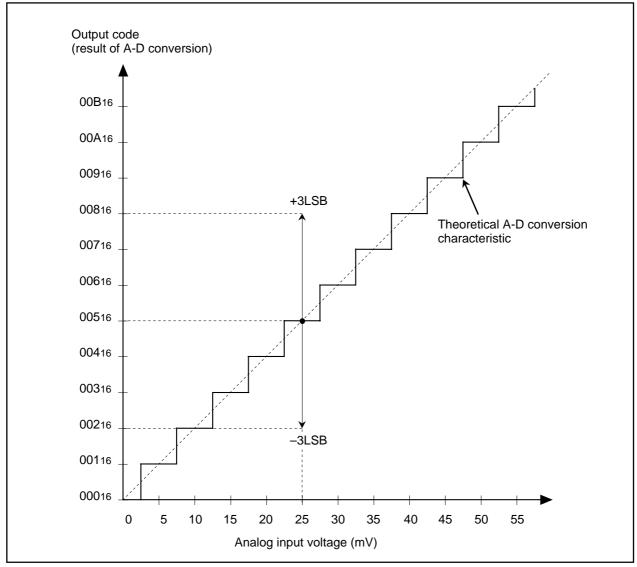

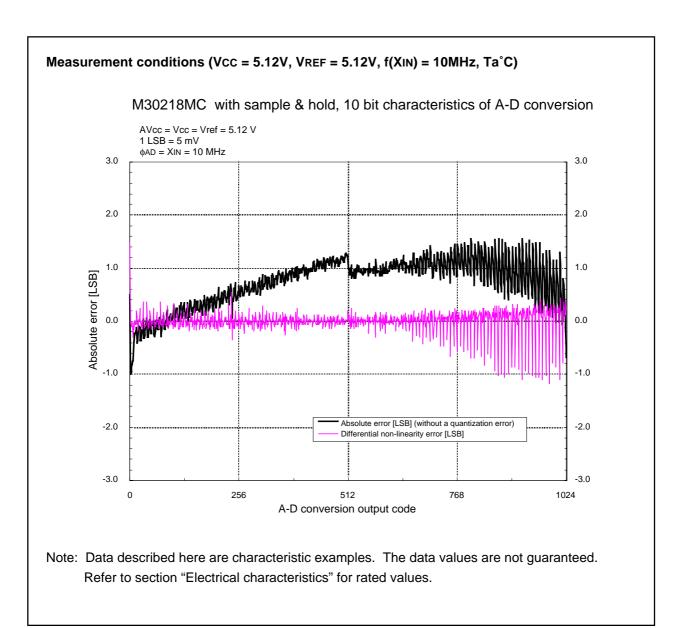

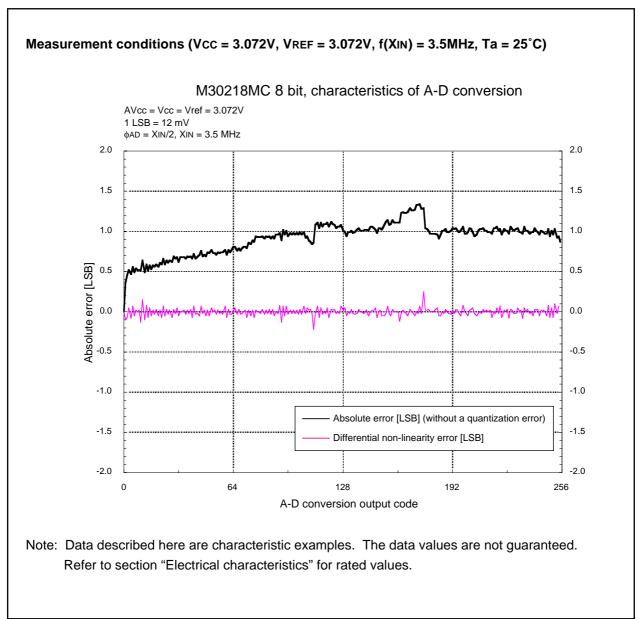

| 5.2 Standard Characteristics of A-D Converter                                          | 446 |

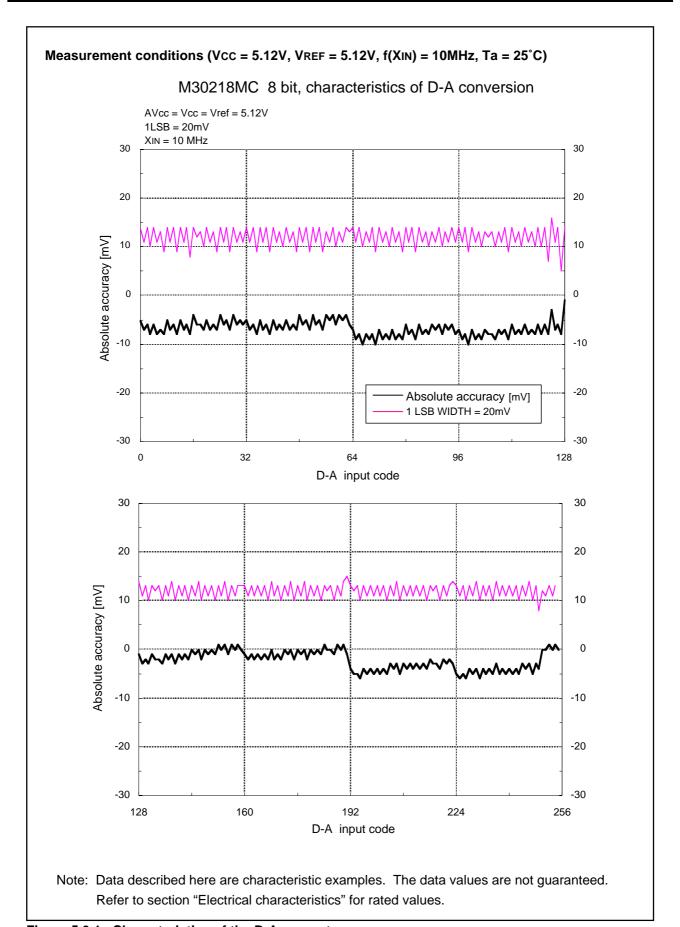

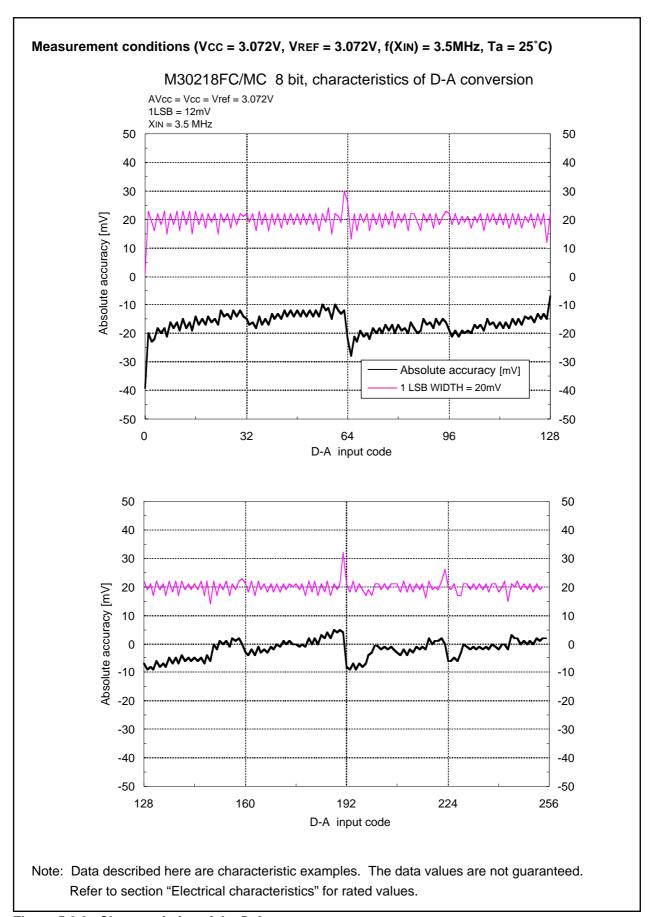

| 5.3 Standard Characteristics of D-A Converter                                          | 448 |

| 5.4 Standard Characteristics of Pull-Up Resistor                                       | 451 |

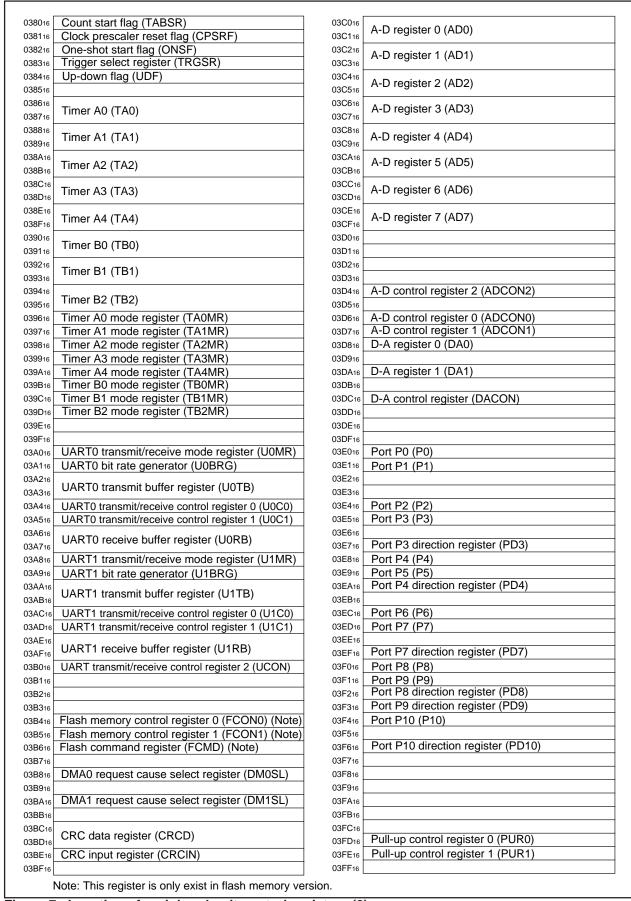

## Quick Reference to Pages Classified by Address

| Addres                                   | Register                                                                   | Page                                             |

|------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------|

| 000016                                   |                                                                            |                                                  |

| 000116                                   |                                                                            |                                                  |

| 000216                                   |                                                                            |                                                  |

| 000316                                   | Dunancia manda ya siatay 0 (DM0)                                           |                                                  |

| 000416                                   | Processor mode register 0 (PM0) Processor mode register 1(PM1)             | 18                                               |

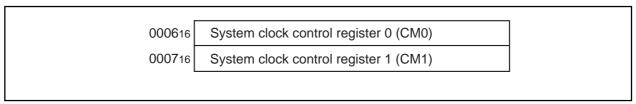

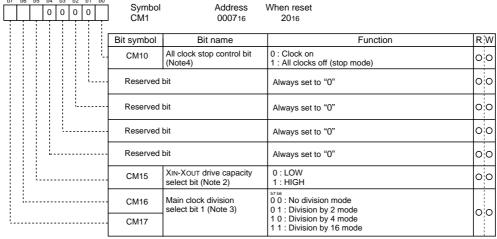

| 000616                                   | System clock control register 0 (CM0)                                      |                                                  |

| 000716                                   | System clock control register 0 (CM0)                                      | 22                                               |

| 000816                                   | Cyclem clock control register 1 (CW1)                                      |                                                  |

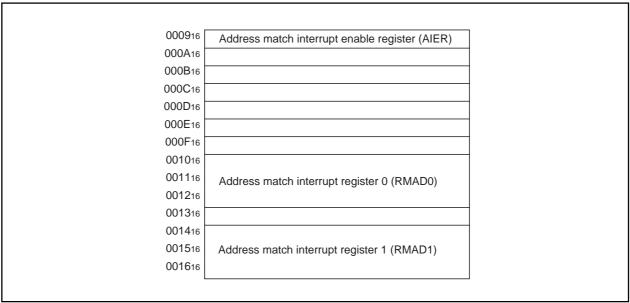

| 000916                                   | Address match interrupt enable register (AIER)                             | 43                                               |

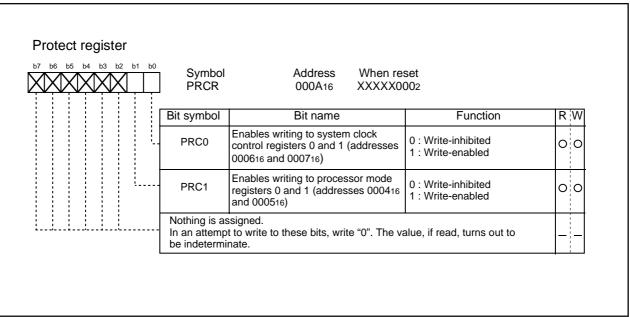

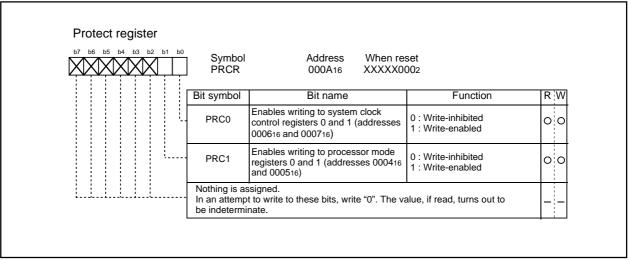

| 000A16                                   | Protect register (PRCR)                                                    | 27                                               |

| 000B16                                   |                                                                            |                                                  |

| 000C16                                   |                                                                            | .                                                |

| 000D16<br>000E16                         | IN ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) (                                   |                                                  |

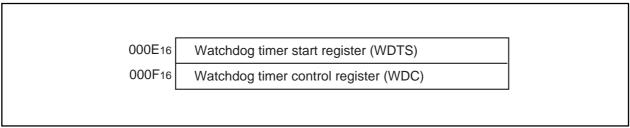

| 000E16                                   | Watchdog timer start register (WDTS) Watchdog timer control register (WDC) | 47                                               |

| 001016                                   | watchdog timer control register (WDC)                                      |                                                  |

| 001116                                   | Address match interrupt register 0 (RMAD0)                                 | 43                                               |

| 001216                                   | radios materialitical perception of (Nin 120)                              | 73                                               |

| 001316                                   |                                                                            |                                                  |

| 001416                                   |                                                                            |                                                  |

| 001516                                   | Address match interrupt register 1 (RMAD1)                                 | 43                                               |

| 001616                                   |                                                                            |                                                  |

| 001716                                   |                                                                            | .                                                |

| 001916                                   |                                                                            | .                                                |

| 001A <sub>16</sub>                       |                                                                            | -                                                |

| 001B <sub>16</sub>                       |                                                                            |                                                  |

| 001C <sub>16</sub>                       |                                                                            | 1                                                |

| 001D <sub>16</sub>                       |                                                                            |                                                  |

| 001E <sub>16</sub>                       |                                                                            |                                                  |

| 001F <sub>16</sub>                       |                                                                            |                                                  |

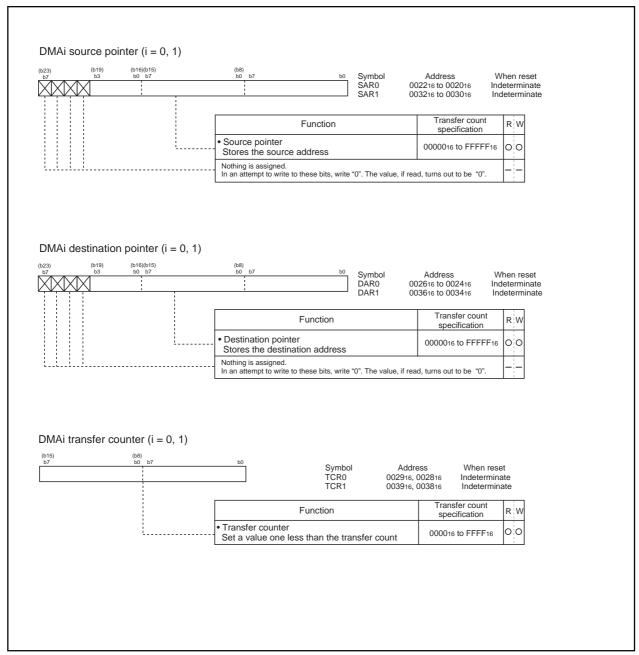

| 002016<br>002116                         | DMA0 source pointer (SAR0)                                                 | 51                                               |

| 002116                                   | Divine dedice pointer (extre)                                              | "                                                |

| 002316                                   |                                                                            |                                                  |

| 002416                                   |                                                                            |                                                  |

| 002516                                   | DMA0 destination pointer (DAR0)                                            | 51                                               |

| 002616                                   |                                                                            |                                                  |

| 002716                                   |                                                                            |                                                  |

| 002816<br>002916                         | DMA0 transfer counter (TCR0)                                               | 51                                               |

| 002916<br>002A16                         |                                                                            |                                                  |

| 002B16                                   |                                                                            |                                                  |

| 002C16                                   | DMA0 control register (DM0CON)                                             | 50                                               |

| 002D16                                   |                                                                            |                                                  |

| 002E16                                   |                                                                            |                                                  |

| 002F16                                   |                                                                            |                                                  |

| 003016                                   | DMA1 source pointer (SAR1)                                                 | 51                                               |

| 0031 <sub>16</sub><br>0032 <sub>16</sub> | Divirti Source politici (Oniti)                                            | "                                                |

| 003216                                   |                                                                            | <del>                                     </del> |

| 003316                                   |                                                                            |                                                  |

| 003516                                   | DMA1 destination pointer (DAR1)                                            | 51                                               |

| 003616                                   |                                                                            |                                                  |

| 003716                                   |                                                                            |                                                  |

| 003816                                   | DMA1 transfer counter (TCR1)                                               | 51                                               |

| 003916                                   |                                                                            | ļ .                                              |

| 003A <sub>16</sub>                       |                                                                            |                                                  |

| 003C16                                   | DMA1 control register (DM1CON)                                             | 50                                               |

| 003D16                                   | DWW TO CONTROL TO GISTER (DIVITO OIV)                                      | 30                                               |

| 003E16                                   |                                                                            |                                                  |

| 003F <sub>16</sub>                       |                                                                            | 1                                                |

|                                          |                                                                            |                                                  |

| Addres                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ss Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Pag                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| 004016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                         |

| 0041 <sub>16</sub><br>0042 <sub>16</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                         |

| 004216                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                         |

| 004416                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                         |

| 004516                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                         |

| 004616                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                         |

| 004716                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | INT3 interrupt control register (INT3IC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                         |

| 004816                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | INT4 interrupt control register (INT4IC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 34                                                      |

| 004916                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | INT5 interrupt control register (INT5IC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                         |

| 004A16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                         |

| 004B16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DMA0 interrupt control register (DM0IC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34                                                      |

| 004C16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DMA1 interrupt control register (DM1IC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34                                                      |

| 004D16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                         |

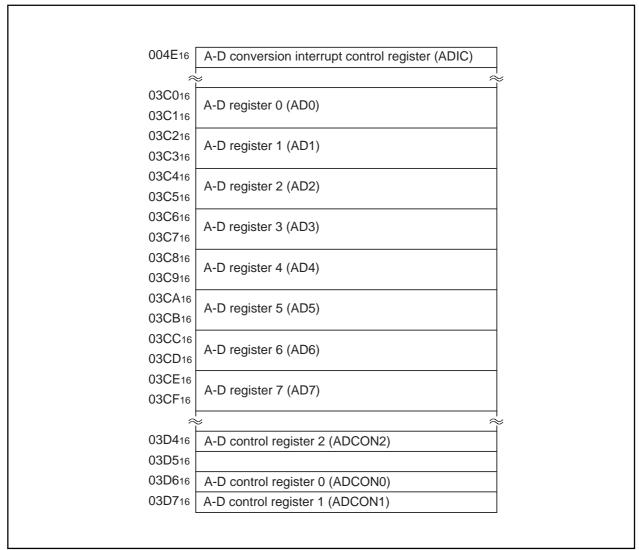

| 004E16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A-D conversion interrupt control register (ADIC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                         |

| 004F16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SI/O2 automatic transfer interrupt control register (ASIOIC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                         |

| 005016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | FLD interrupt control register (FLDIC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                         |

| 005116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | UARTO transmit interrupt control register (S0TIC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                         |

| 005216                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | UARTO receive interrupt control register (SORIC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                         |