**TENTATIVE**

TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# TC90A60U

# DATA SLICE IC FOR VIDEO MULTIPLEX BROADCAST RECEIVER

TC90A60U is an IC for capturing Japan teletext and data broadcast (also EIA-516) signals superposed on video signals. Its main functions include sync separation, equalization, data and sampling clock generation, and error correction.

When connected in parallel to a microcontroller, the IC allows data capturing with a relatively small part count.

#### **FEATURES**

- Digital regeneration of Japan eletext and data broadcast (also EIA-516) data using a built-in AD converter

- Equalization using a 13-tap transversal filter (equalization range : -0.5~1.5 μs)

- Buffer memory which accommodate 8 data packets

- Error correction circuit

- Framing code detection

- Sync separator circuit

- Parallel interface (8 bits for data, 4 bits for address and 3 bits for control)

- 3.3 V single power supply

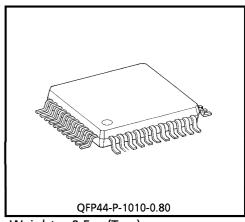

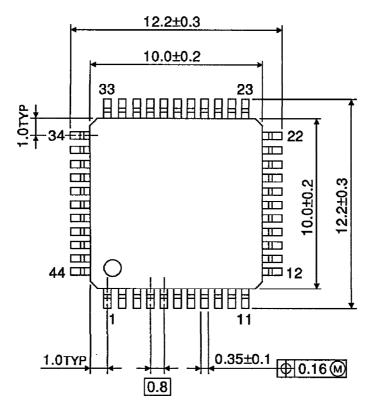

Weight: 0.5 g (Typ.)

# **PIN ASSIGNMENT**

**BLOCK DIAGRAM**

TC90A60U - 3

#### **OVERVIEW OF TC90A60U INTERNAL BLOCKS**

#### 1. AD Converter

TC90A60U incorporates a 6-bit serial high-speed AD converter, which converts composite video signals superposed with Japan teletext signals.

(Sampling frequency: 16/5 fsc = 11.454545 MHz)

# 2. System Clock Oscillator

A crystal oscillator is used to generate clocks such as sampling clock for the AD Converter.

(Oscillation frequency: 32/5 fsc = 22.909088 MHz)

#### 3. Data regeneration and equalization

Video multiplex signals are sampled and converted in the AD converter.

The data is equalized using the built-in 13-tap transversal filter so as to recognize 0 or 1 correctly. The equalization range is  $-0.5 \sim +1.5 \,\mu s$ .

#### 4. Data capture

Equalized multiplex data on lines  $10 \text{ H} \sim 16 \text{ H}$  and 21 H (any lines within  $10 \text{ H} \sim 25 \text{ H}$  can be selected using the Control Register) are captured into the buffer memory which accommodates 8 data packets.

A single packet consists of 35 bytes.

#### 5. Sync Separator

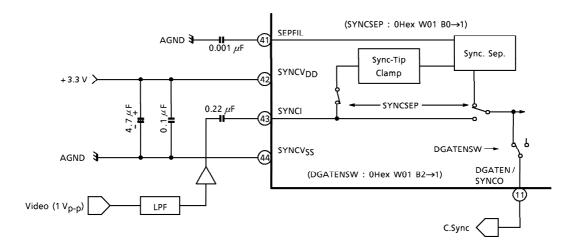

The sync separator separates composite sync signals from the luminance signals which are removed of color signal in the LPF external to the IC.

#### 6. Microcontroller Interface

TC90A60U incorporates a parallel interface to allow connection to a microcontroller.

# 7. Monitors and control pins

TC90A60U incorporates pins for monitoring internal operation and controlling external components.

ATTN : Outputs video attenuator control signals.

Also used for monitoring system clock (22.9 MHz).

DGATEN/SYNCO: Used for monitoring sync separation circuit output signals or data capture timing.

PIO [2~0] : Used as general-purpose input/output pins.

For details of each block, please refer to functional description.

# • PIN DESCRIPTION

|              | PIN No. | PIN NAME          | 1/0 | FUNCTION                                                              | INPUT                 | OUTPUT          |

|--------------|---------|-------------------|-----|-----------------------------------------------------------------------|-----------------------|-----------------|

|              | 1       | ADREF1            |     | ADC reference pin<br>(Connected to GND via a<br>capacitor)            |                       |                 |

|              | 2       | AV <sub>DD</sub>  |     | Analog V <sub>DD</sub> pin for ADC                                    | 1.1 V <sub>p-p</sub>  |                 |

| 0 0          | 3       | VIN               | ı   | Analog input pin for ADC (Dynamic input range: 1.1 V <sub>p-p</sub> ) |                       |                 |

| <del> </del> | 4       | AVSS              |     | Analog GND pin for ADC                                                |                       |                 |

|              | 5       | ADREF2            |     | ADC reference pin<br>(Connected to GND via a<br>capacitor)            |                       |                 |

|              | 6       | ADBIAS            |     | ADC bias pin<br>(Connected to GND via a<br>capacitor)                 |                       |                 |

|              | 9       | RESET             | ı   | System reset pin (Active Low)                                         | 5 V withstand voltage |                 |

|              | 10      | ATTN              | 0   | Video attenuator output pin (Active LOW)                              |                       | V <sub>DD</sub> |

| g            | 11      | DGATEN /<br>SYNCO | 0   | Teletext signals removing gate signal output pin (default setting)    |                       | V <sub>DD</sub> |

| [ <u>:</u> [ |         |                   | 0   | Sync separation signal output pin                                     |                       | $V_{DD}$        |

| Testing      | 12      | TESTO             | ı   | Test input pin 0 (Fix to HIGH in normal operation)                    |                       |                 |

|              | 13      | TEST1             | I   | Test input pin 1 (Fix to HIGH in normal operation)                    |                       |                 |

|              | 14      | TEST2             | ı   | Test input pin 2 (Fix to HIGH in normal operation)                    |                       |                 |

|              | 16      | DV <sub>DD2</sub> |     | Digital V <sub>DD</sub>                                               |                       |                 |

| tion         | 17      | OSCSI             | ı   | System clock oscillation circuit input                                |                       |                 |

| Oscillation  | 18      | oscso             | 0   | System clock oscillation circuit input (32 / 5 fsc)                   |                       |                 |

|              | 19      | DV <sub>SS2</sub> |     | Digital GND                                                           |                       |                 |

|                                     | PIN No. | PIN NAME            | 1/0 | FUNCTION                                                                                                   | INPUT                   | OUTPUT                      |

|-------------------------------------|---------|---------------------|-----|------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------------|

|                                     | 7       | DV <sub>DD1</sub>   |     | Digital V <sub>DD</sub>                                                                                    |                         |                             |

|                                     | 8       | DV <sub>SS1</sub>   |     | Digital GND                                                                                                |                         |                             |

|                                     | 15      | INT                 | 0   | Interrupt signal output pin (open-drain buffer)                                                            |                         | 5 V<br>withstand<br>voltage |

|                                     | 20      | RD                  | ı   | Read enable signal input pin (Active Low)                                                                  | 5 V withstand voltage   |                             |

| U                                   | 21      | RD/WR               | I   | Write enable signal input pin (Active Low)                                                                 | 5 V withstand voltage   |                             |

| ogi                                 | 22      | CS                  | I   | Chip select input pin (Active Low)                                                                         | 5 V withstand voltage   |                             |

| <u> </u>                            | 23      | ADR0                | - 1 | Address Bus 0 control                                                                                      | 5 V withstand voltage   |                             |

| a)                                  | 24      | ADR1                |     | Address Bus 1 control                                                                                      | 5 V withstand voltage   |                             |

| Microcontroller Interface and Logic | 25      | ADR2                | T   | Address Bus 2 contro                                                                                       | 5 V withstand voltage   |                             |

| rfa                                 | 26      | ADR3                | ı   | Address Bus 3 control                                                                                      | 5 V withstand voltage   |                             |

| nte                                 | 27      | DV <sub>DD3</sub>   |     | Digital V <sub>DD</sub>                                                                                    |                         |                             |

| <del>-</del>                        | 28      | D0                  | 1/0 | Data Bus 0                                                                                                 | 5 V withstand voltage   | $V_{DD}$                    |

| le l                                | 29      | D1                  | 1/0 | Data Bus 1                                                                                                 | 5 V withstand voltage   | $V_{DD}$                    |

| l S                                 | 30      | D2                  | 1/0 | Data Bus 2                                                                                                 | 5 V withstand voltage   | $V_{DD}$                    |

| Į į                                 | 31      | D3                  | 1/0 | Data Bus 3                                                                                                 | 5 V withstand voltage   | $V_{DD}$                    |

| Į                                   | 32      | D4                  | 1/0 | Data Bus 4                                                                                                 | 5 V withstand voltage   | $V_{DD}$                    |

| Ĭĕ                                  | 33      | D5                  | 1/0 | Data Bus 5                                                                                                 | 5 V withstand voltage   | $V_{DD}$                    |

|                                     | 34      | D6                  | 1/0 | Data Bus 6                                                                                                 | 5 V withstand voltage   | $V_{DD}$                    |

|                                     | 35      | D7                  | 1/0 | Data Bus 7                                                                                                 | 5 V withstand voltage   | $V_{DD}$                    |

|                                     | 36      | DV <sub>SS3</sub>   |     | Digital GND                                                                                                |                         |                             |

|                                     | 37      | PIO0                | 1/0 | General-purpose input/output pin 0 (input pin by default)                                                  | 5 V withstand voltage   | v <sub>DD</sub>             |

|                                     | 38      | PIO1                | 1/0 | General-purpose input/output pin 1 (input pin by default)                                                  | 5 V withstand voltage   | v <sub>DD</sub>             |

|                                     | 39      | PIO2                | 1/0 | General-purpose input/output pin 2 (input pin by default)                                                  | 5 V withstand voltage   | v <sub>DD</sub>             |

|                                     | 40      | DV <sub>DD4</sub>   |     | Digital V <sub>DD</sub>                                                                                    |                         |                             |

| ıtion                               | 41      | SEPFIL              |     | Sync separation filter pin<br>(Connected to GND via a<br>capacitor)                                        |                         |                             |

| Sync Separation                     | 42      | SYNCV <sub>DD</sub> |     | Analog V <sub>DD</sub> for sync separator<br>Composite sync signal (C.Sync)<br>input pin (default setting) | 3.3 V withstand voltage |                             |

| Sync                                | 43      | SYNCI               | ı   | Sync separation luminance signal input pin                                                                 | 1 V <sub>p-p</sub>      |                             |

|                                     | 44      | SYNCVSS             |     | Analog GND for sync separation                                                                             |                         |                             |

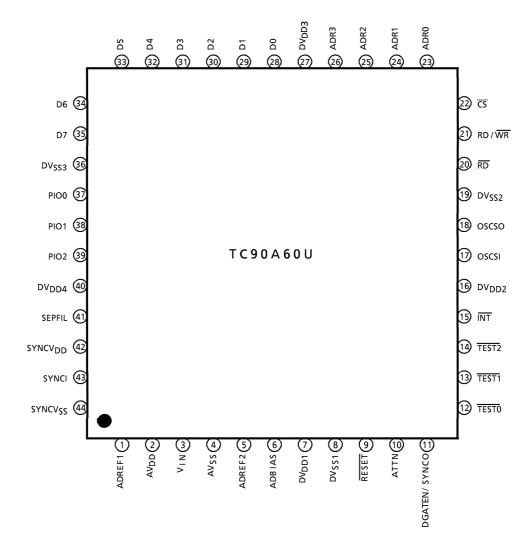

# **MAXIMUM RATINGS** (Ta = 25°C)

| PARAMETER            | SYMBOL           | RATING                     | UNIT |

|----------------------|------------------|----------------------------|------|

| Power Supply Voltage | $V_{DD}$         | Vss~Vss + 4.5              | V    |

| Input Voltage        | V <sub>IN1</sub> | -0.3~V <sub>DD</sub> + 0.3 | >    |

| Input voitage        | $v_{IN2}$        | −0.3~5.5 (Note 1)          | >    |

| Power Dissipation    | PD               | 520 (Note 2)               | mW   |

| Storage Temperature  | T <sub>stg</sub> | <b>-</b> 55∼125            | °C   |

(Note 1) : Applicable to ADR [3 $\sim$ 0], D [7 $\sim$ 0] CS, RD, RD/WR, PIO [2 $\sim$ 0] RESET

(Note 2): When the device is used in an ambient temperature of 25 °C or higher, the rated

value should be calculated by decrementing 5.20 mW per 1 °C.

# RECOMMENDED OPERATING CONDITIONS

| PARAMETER             | SYMBOL           | MIN  | TYP. | MAX      | UNIT |

|-----------------------|------------------|------|------|----------|------|

| Power Supply Voltage  | $V_{DD}$         | 3.0  | 3.3  | 3.6      | V    |

| Input Voltage         | $v_{IN}$         | 0    |      | $V_{DD}$ | ٧    |

| Operating Temperature | V <sub>opr</sub> | - 20 | _    | 75       | °C   |

#### PRECAUTIONS

- Do not apply voltage to any pin or pins while the power supply to the IC is off.

- D [7~0], PIO [2~0] should not be pulled up to 5 V. These pins are used both for input and output: their input withstand voltage is 5 V and their HIGH output voltage is V<sub>DD</sub> (3.3 V). Pulling these pins up to 5 V results in unstable operation.

Pulling-up I/O pins with 5-V withstand voltage

|           |       |      | 3                        |

|-----------|-------|------|--------------------------|

| PIN       | PUL   | L-UP | RECOMMENDED RESISTANCE   |

| FIIN      | 3.3 V | 5 V  | RECOMMENDED RESISTANCE   |

| ADR [3~0] | 0     | 0    | 3.3 k $\Omega$ or higher |

| CS        | 0     | 0    | 3.3 k $\Omega$ or higher |

| RD        | 0     | 0    | 3.3 k $\Omega$ or higher |

| RD/WR     | 0     | 0    | 3.3 k $\Omega$ or higher |

| RESET     | 0     | 0    | 3.3 k $\Omega$ or higher |

| D [7~0]   | 0     | ×    | 3.3 k $\Omega$ or higher |

| PIO [2~0] | Ó     | ×    | 3.3 k $\Omega$ or higher |

I/O REGISTERS

1. Write Registers

| PIN STATE | TATE |              |                                                |          |       |        |       |        |        |                                                                                                                                                               |         |

|-----------|------|--------------|------------------------------------------------|----------|-------|--------|-------|--------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| RD/       | ADR  | SYM.         | FUNCTION                                       | SW NAME  | 87 86 | B5     | B4 B3 | 3 B2   | 818    | B0 REMARKS                                                                                                                                                    | INITIAL |

| Ş         | 0Hex | ,<br>00<br>M | OHex W00 Selects capture line.                 | ZDIP     | 0     | 0      | 0     | 0      | 0      | 0 Bits B7~B0 corresponds to line buffers 7~0, respectively. 1: Captures 0: Does not capture.                                                                  | 00Hex   |

| Š         | 0Hex | W0           | 0Hex W01 Selects C.Sync input mode.            | SYNCSEP  |       |        |       |        | H      | 0 0 : C.Sync Input Mode 1 : Internal Sync Separation Mode                                                                                                     | 0       |

|           |      |              | Selects C.Sync input signal polarity.          | SYNCPOL  |       |        |       |        | 0      | 0 : Negative 1 : Positive                                                                                                                                     | 0       |

|           |      |              | Selects DGATEN (Pin 11) output signal.         | DGATENSW |       |        |       | 0      |        | 0 : DGATEN (capture timing monitor) 1 : SYNCO (sync signal monitor)                                                                                           | 0       |

|           |      |              | Selects sync separation level.                 | SEPLEV   |       |        | 0     |        |        | Selects slice level for the internal sync separation circuit. (Refer to 1.7.)                                                                                 | 0       |

|           |      |              | Selects error correction mode.                 | BESTC    |       |        | 0     |        |        | 0 : Carries out BEST correction. 1 : Does not carry out BEST correction.                                                                                      | 0       |

|           |      |              | Selects INT signal deassertion mode.           | INTSW    | 0     |        |       |        |        | 1 : Automatically deasserts INT signal approximately 260 ns after its occurrence.                                                                             | 0       |

|           |      |              | Selects ATTN (Pin 10) output signal.           | ATTNSW   | 0     |        |       |        |        | 0 : ATTN 1: System clock monitor                                                                                                                              | 0       |

|           |      |              |                                                |          |       | 0      |       |        |        | This bit must be fixed to 0.                                                                                                                                  |         |

| WR        | 0Hex | W02          | 0Hex W02 Selects framing code protection mode. | FC1STN   |       |        | l     |        | H      | 0 0 : Only the framing code detected first is valid. 1 : All framing codes are valid.                                                                         | 0       |

|           |      |              | Selects framing code regeneration mode.        | FCH0GO   |       |        |       |        | 0      | 0 : Framing code real-time generation mode 1 : Framing code consecutive regeneration mode                                                                     | 0       |

|           |      |              | Selects fixed / variable capture line.         | VARLN    |       |        | 0     |        |        | 0 : 10H∼16H and 21H (fixed) 1 : Variable                                                                                                                      | 0       |

|           |      |              |                                                |          | 0     | 0      | 0     | 0      |        | These bits must be fixed to 0.                                                                                                                                | 0       |

| W         | ОНех |              | W03 Selects Line 0/Line 1 capture.             | LINE01   | ri    | Line 1 | H     | Ľį     | Line 0 | Selects the line to be captured into the buffer using the corresponding four bits.                                                                            | 10Hex   |

| N<br>R    | OHex | W04          | 0Hex W04 Selects Line 2/Line 3 capture.        | LINE23   | Lir   | Line 3 | H     | Line 2 | 7      | ZDIP is used to select whether or not to capture the selected line. The line to be continued and be obtained by additing an officer of 10 to the dubit value. | 32Нех   |

| ٧ĸ        | 0Hex | W05          | 0Hex W05 Selects Line 4 / Line 5 capture.      | LINE45   | Lir   | Line 5 | Н     | Ľį     | Line 4 | (e.g. If 01018in is specified, 5H + 10H, that is, 15H, is selected.)                                                                                          | 54Hex   |

| ٧R        | ОНех |              | W06 Selects Line 6/Line 7 capture.             | LINE67   | Li    | Line 7 | Н     | Ë      | Line 6 | The same line cannot be selected to be captured into multiple buffers.                                                                                        | ВбНех   |

| N.        | 0Hex | W07          | 0Hex W07 Selects framing code.                 | FCCODE   | 1 1   | -      | 0 0   | -      | 0      | 1 Selects framing code.                                                                                                                                       | ESHex   |

Consecutive Writes

| WR         1 Hex         W10         Selects line buffer to be read out.         INPH         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 </th <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th>ļ</th> <th>-</th> <th>ŀ</th> <th>١</th> <th></th> <th>l</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |      |        |                                     |         |   | ļ     | -    | ŀ | ١        |                                                                                                     | l     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|--------|-------------------------------------|---------|---|-------|------|---|----------|-----------------------------------------------------------------------------------------------------|-------|

| address.         ARSTA         0         0         0         0         0         0         0         0         Selects the byte address of the line buffer to start access (00Hex~22Hex) using the lower six bits.           FLGRST         FLGRST         0         1 : Resets Capture Completion Flag and Error Correction Completion Flag.           T signal.         INTRST         0         1 : Deasserts INT signal.           Internally.         HLDASST         0         1 : HLDA signal is set internally in the IC. (Refer to 2.2.)         Do not simultaneously set these two bits to 1.           Internally.         0         1 : COR signal is set internally in the IC. (Refer to 2.2.)         Do not simultaneously set these two bits to 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | WR | 1Hex | W10    | Selects line buffer to be read out. | HdNi    | 0 | 0     | 0    | 0 | 0        | Selects line buffer $(7\sim0)$ to be read out on R30 using the lower three bits.                    | 00Hex |

| Tignal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ٧R |      | ž<br>L | Selects byte address.               | ARSTA   | 0 | ٥     | 0    | 0 | 0        | Selects the byte address of the line buffer to start access (00Hex~22Hex) using the lower six bits. | 00Hex |

| FLGRST         0         1 : Resets Capture Completion Flag and Error Correction and Error Correction (Annual Section Flag and Error Correction (Annual Flag and Error Corr |    |      |        |                                     |         |   |       |      |   |          | 00Hex∼22Hex                                                                                         |       |

| Tiggnal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |      |        |                                     |         |   |       |      |   |          |                                                                                                     |       |

| INTRST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | WR | 2Hex | W20    | Resets flags.                       | FLGRST  |   |       |      |   | 0        | 1 : Resets Capture Completion Flag and Error Correction Completion Flag.                            | 0     |

| HLDASET         0         1 : HLDA signal is set internally in the IC. (Refer to 2.2)           HLDARST         0         1 : HLDA signal is reset internally in the IC. (Refer to 2.2)           CORSET         0         1 : COR signal is set internally in the IC. (Refer to 2.2)           0         0         These bits must be fixed to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |      |        | Deasserts INT signal.               | INTRST  |   |       |      | 0 | <u>.</u> | 1 : Deasserts INT signal.                                                                           | 0     |

| HLDARST   0   1 : HLDA signal is reset internally in the IC. (Refer to 2.2   CORSET   0   0   These bits must be fixed to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |      |        | Sets HLDA internally.               | HLDASET |   |       | 0    | ļ | <br>!    | 1 : HLDA signal is set internally in the IC. (Refer to 2.2.)                                        | 0     |

| CORSET         0         1 : COR signal is set internally in the IC. (Refer to 2.2.)           0         0         0         These bits must be fixed to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |      |        | Resets HLDA internally.             | HLDARST |   | 0     | <br> |   |          | 1: HLDA signal is reset internally in the IC. (Refer to 2.2.)                                       | 0     |

| 0 0 These bits must be fixed to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |      |        | Sets COR internally.                | CORSET  | ° | L     |      |   |          | ١.                                                                                                  | 0     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |      |        |                                     |         | 0 | ····· | l°   |   | Ĺ        | These bits must be fixed to 0.                                                                      | 0     |

(Note): Registers W00~W07, W10~W11, W40~W41, R10~R11 and R20~R2F respectively, which share the same address, are written to or read from consecutively. If an access to a different address occurs during the consecutive Read/Write access, the Read/Write resumes by accessing the first register. Writes data to the internal line buffer specified in W10 and W11. ARRDW WR 3Hex W30 Internal RAM Write access

TC90A60U - 9

1. Write Registers (continued)

| 5YM- FUNCTION SW NAME B7 B6 B5 B4 B3 B2 B1 B1        |

|------------------------------------------------------|

| 4Hex W40 General-purpose port output data POD0       |

| setting POD1                                         |

| POD2                                                 |

| 0 0 0                                                |

| WR 4Hex W41 General-purpose port mode setting POCNT0 |

| POCNT1                                               |

| POCNT2                                               |

| 0 0 0 0                                              |

Consecutive Writes

|                           | TRGSTN<br>TRESETON | 1 0 Fixed tap gain 1 0 Equalizer stopped. 1 0 Equalizer reset. |       |

|---------------------------|--------------------|----------------------------------------------------------------|-------|

|                           | TRGSTN RESETON     | 1 0 : Equalizer reset.  1 1 1 1 Theoretise man be fixed to a   | -     |

|                           | RESETON            | 1 0 : Equalizer reset.                                         |       |

|                           |                    | 1 1 Those his must be fload to 1                               | -     |

|                           |                    | I I I I I I I I I I I I I I I I I I I                          | -     |

|                           |                    |                                                                |       |

| WR 6Hex W60 Test register |                    | 1 1 1 1 1 1 1 1 All the bits must be fixed to 1.               | FFHex |

| WR 6Hex W61 Test register |                    | 0 0 0 0 0 0 0 All the bits must be fixed to 0.                 | однех |

| ~         | 7нех | W70 | VR 7Hex W70 Test register | Test register                                          |  |

|-----------|------|-----|---------------------------|--------------------------------------------------------|--|

| æ         | 7нех | W71 | WR 7Hex W71 Test register | When all the test pins (Pin 12~Pin 14) are pulled HIGH |  |

| <u>بر</u> | 7Hex | W72 | WR 7Hex W72 Test register | (i.e. the device is in normal operation),              |  |

| ~         | 7нех | W73 | WR 7Hex W73 Test register | Inputting any value on W70~W73 has no effect.          |  |

(Note): Registers W00~W07, W10~W11, W40~W41, R10~R11 and R20~R2F respectively, which share the same address, are written to or read from consecutively. If an access to a different address occurs during the consecutive Read/Write access, the Read/Write resumes by accessing the first register.

2. Read Registers

|           | REMARKS                         | 1 : Capture complete                     | 1 : BEST correction complete         | 1 : Line buffer internal access. (Refer to 2.2.) | 1 : Correction is in progress. (Refer to 2.2.) | Bits B7∼B4 are undefined. |

|-----------|---------------------------------|------------------------------------------|--------------------------------------|--------------------------------------------------|------------------------------------------------|---------------------------|

| H         |                                 | -                                        | ш                                    | _                                                | -                                              |                           |

|           | 8                               |                                          |                                      |                                                  |                                                |                           |

|           | B1 B0                           |                                          |                                      |                                                  |                                                |                           |

|           | B2 B1 B0                        |                                          |                                      |                                                  |                                                |                           |

|           | 83 82 81 80                     |                                          |                                      |                                                  |                                                |                           |

|           | 84 83 82 81 80                  |                                          |                                      |                                                  |                                                | ×                         |

|           | 85 84 83 82 81 B0               |                                          |                                      |                                                  |                                                | ×                         |

|           | 86 85 84 83 82 81 80            |                                          |                                      |                                                  |                                                | ×                         |

|           | B7 86 85 84 B3 82 81 B0         |                                          |                                      |                                                  |                                                | ×<br>×<br>×               |

|           | SW NAME B7 86 85 84 83 82 81 80 | TFLG                                     | CFLG                                 | HLDA                                             | COR                                            | ×<br>×<br>×               |

|           | FUNCTION SW NAME                |                                          | BEST Correction Completion Flag CFLG | HLDA signal monitor HLDA                         | COR signal monitor COR                         | ××××                      |

|           | FUNCTION SW NAME                |                                          | BEST Correction Completion Flag CFLG |                                                  |                                                | × × × ×                   |

| PIN STATE | SW NAME                         | RD 8Hex R00 Capture Completion Flag TFLG | BEST Correction Completion Flag CFLG |                                                  |                                                | × × × ×                   |

| Stores framing detection result 0 : Normal 1 : Error Bits B7~80 corresponds to line buffer 7~0, respectively. | Stores BEST correction result 0 : Normal 1 : Error Bits B7~B0 corresponds to line buffers 7~0, respectively. | Check Outputs the first two bytes of the line buffer content before error correction. | The lift $\times$ X The bit sequence is inverted. (B7 becomes LSB.) | Check       | × × 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 |

|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------|-----------------------------------------|

|                                                                                                               |                                                                                                              | SI SI                                                                                 | TE TE                                                               | <br>- 15    | Cl TF                                   |

| FCDET                                                                                                         | BESTFLG                                                                                                      | OIS                                                                                   | CI0                                                                 | <br>215     | CI7                                     |

| 9Hex R10 Framing code detection result                                                                        | RD 9Hex R11 BEST correction result                                                                           | RD AHex R20 SI data and CI data                                                       | RD AHex R21 (All line buffers)                                      |             |                                         |

| R10                                                                                                           | R11                                                                                                          | R20                                                                                   | R21                                                                 | <br>RZE     | RZF                                     |

| 9нех                                                                                                          | энех                                                                                                         | AHex                                                                                  | AHex                                                                | АНех        | RD AHex R2F                             |

| SD.                                                                                                           | g                                                                                                            | å.                                                                                    | ₽D.                                                                 | <br>RD AHex | Ğ.                                      |

| L | -        |        |                                    |      |                  |   |                                                                     |  |

|---|----------|--------|------------------------------------|------|------------------|---|---------------------------------------------------------------------|--|

| Z | <u> </u> | CHex R | 40 General-purpose port input data | PID0 |                  |   | <br>1 : HIGH, 0 : LOW (Undefined when the port is used for output.) |  |

|   |          |        |                                    | PID1 |                  |   | 1 : HIGH, 0 : LOW (Undefined when the port is used for output.)     |  |

|   |          |        |                                    | PID2 |                  |   | 1 : HIGH, 0 : LOW (Undefined when the port is used for output.)     |  |

|   |          |        |                                    |      | ×<br>×<br>×<br>× | × | <br>Bits B7~B3 are undefined.                                       |  |

|   |          |        |                                    |      |                  |   |                                                                     |  |

Outputs the content of the line buffer specified in W10 and W11. W11 (byte address) is automatically incremented on each consecutive access.

ARRDR

Receive data (line buffer data)

R30

ВНех

RD.

| (NSB) (LSB) Outputs the content of W70. | V41, R10~R11 and R20~R2F respectively, which share the same address, are written to or read from consecutively. If an access to |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| R70 Test Register                       | Registers W00~W07, W10~W11, W40~W41                                                                                             |

| FHex                                    | Vote) : I                                                                                                                       |

| RD.                                     | ڪ                                                                                                                               |

to a different address occurs during the consecutive Read/Write access, the Read/Write resumes by accessing the first register.

#### **FUNCTIONAL DESCRIPTION**

#### 1. Basic Functions

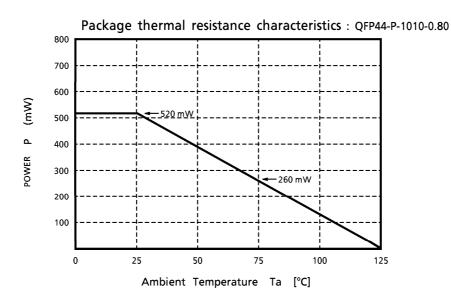

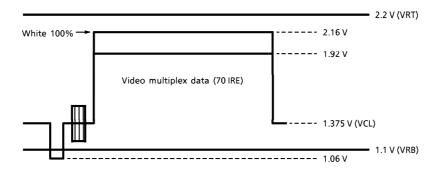

1.1 AD Converter Specifications (video input)

Data conversion range :  $1.1 \text{ V} \pm 0.01 \text{ V} \text{ (VRB)} \sim 2.2 \text{ V} \pm 0.01 \text{ V} \text{ (VRT)}$

Pedestal Clamp :  $1.375 \text{ V} \pm 0.01 \text{ V} (1/4 \text{ of data conversion range})$

Data conversion rate : 16/5 fsc (11.454545 MHz)

• The difference between AD bottom range (VRB) and clamp level (VCL) is 0.25 V (35 IRE).

• The amplitude of video multiplex data is 70 IRE.

# ■ 1V<sub>p-p</sub> Video Input

# ■ 1.1 Vp-p Video Input

#### 1.2 System Clock Oscillator

TC90A60U uses a crystal resonator to generate 32/5 fsc source clock (4 times teletext data rate 8/5 fsc).

The crystal resonator to be used should observe the following specifications.

# Crystal resonator specifications

| PARAMETER                           | SPECIFICATION                             |

|-------------------------------------|-------------------------------------------|

| Nominal Frequency (f <sub>0</sub> ) | 22.909088 MHz                             |

| Load Capacitance                    | 30.0 pF ± 0.5 pF                          |

| Frequency Deviation                 | ± 20 ppm                                  |

| Equivalent Resistance               | 30 $\Omega$ or below, serial              |

| Temperature Characteristics         | ±30 ppm, -20 °C~75 °C (reference : 25 °C) |

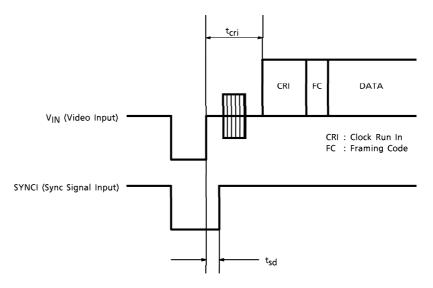

#### 1.3 Video Input and Sync Input

| PARAMETER    | SYMBOL           | MIN | TYP. | MAX | UNIT   |

|--------------|------------------|-----|------|-----|--------|

| CRI position | t <sub>cri</sub> | 27  | 29   | 32  | TC (*) |

| SYNC delay   | t <sub>sd</sub>  | _   | _    | 0.8 | μs     |

(\*) :  $TC = 1/364 f_H \mu s$

# 1.4 Equalization Circuit

The equalization circuit incorporates a 13-tap transversal filter. The equalization range is  $-0.5 \,\mu\text{s} \sim +1.5 \,\mu\text{s}$ . Equalization takes approximately  $0.1 \,\text{s} \sim 2 \,\text{s}$  to complete. (Equalization is almost complete when 32 to 128 lines are captured.)

The filter modulus cannot be changed by the user.

If the tap gain of the filter is too high, ATTN (Pin 10) is pulled LOW.

By attaching an attenuator circuit external to the IC, the LOW signal can be used to control the input amplitude and thereby to prevent overflows.

#### 1.5 Error Correction Circuit

Error correction is performed on each data packet (272,190) using shortened cyclic code for difference set.

The data after error correction is written in the 8 built-in line buffers.

Error correction takes approximately 100  $\mu$ s for each line buffer.

#### 1.6 Line Buffers

TC90A60U incorporates 8 line buffers, each of which consists of 35 bytes.

Each line buffer corresponds to a single data line: which line buffer corresponds to which data line can be set in software. A single data line cannot be set to be captured into multiple line buffers. Thus it is not allowed, for instance, to capture 10H into all the 8 line buffers. TC90A60U is not capable of accumulating more than 1-field data. A set of data usually extends continuously across many fields. Thus capturing such a set of data requires field-by-field access to TC90A60U and storing the captured data in a larger external memory.

• Line buffer data configuration

The two tables below show the contents to be captured into a line buffer before error correction (left) and the contents of the line buffer after error correction (right) in ordinary teletext broadcast.

Line buffer content before error correction

| Line butter conte | iii L                   | nt before error correction |    |    |      |    |    |    |

|-------------------|-------------------------|----------------------------|----|----|------|----|----|----|

| BYTE ADDRESS      | В7                      | В6                         | В5 | В4 | В3   | В2 | В1 | во |

| 00hex             | b0                      | b1                         | b2 | b3 | b4   | b5 | b6 | b7 |

|                   |                         | SI Check                   |    |    |      |    |    |    |

| 01hex             | b0                      | b0 b1 b2 b3 b              |    |    |      | b0 | b1 |    |

|                   |                         | C                          | ]  |    | TF   | IF | DI | 31 |

| 02hex             | b2                      | b3                         | b4 | b5 | b6   | b7 | b0 | b1 |

|                   |                         |                            | DI | 31 |      |    | DI | 32 |

| \$                |                         |                            |    | 1  | 5    |    |    |    |

| 17hex             | b2                      | b3                         | b4 | b5 | b6   | b7 | 0  | 1  |

|                   |                         |                            | DB | 22 |      |    | С  | В  |

| 18hex             | 2                       | 3                          | 4  | 5  | 6    | 7  | 8  | 9  |

|                   | CB: Check bit (82 bit)  |                            |    |    |      |    |    |    |

| \$                | \$                      |                            |    |    |      |    |    |    |

| 21hex             | 74                      | 75                         | 76 | 77 | 78   | 79 | 80 | 81 |

|                   | CB : Check bit (82 bit) |                            |    |    |      |    |    |    |

| 22hex             |                         |                            | =  |    | ===  |    |    | b0 |

|                   |                         |                            |    |    | (*1) |    |    |    |

Line buffer content after error correction

| Line burier conte | nt after error correction |                   |            |    |     |                           |     |      |

|-------------------|---------------------------|-------------------|------------|----|-----|---------------------------|-----|------|

| BYTE ADDRESS      | В7                        | В6                | В5         | В4 | В3  | В2                        | В1  | В0   |

| 00hex             | b5                        | b5 b4 b3 b2 b1 b0 |            |    |     | ${} {\color{red} {\sim}}$ |     |      |

|                   | Ch                        | eck               |            | S  | 51  |                           | Unı | ısed |

| 01hex             |                           |                   | b3         | b2 | b1  | b0                        | b7  | b6   |

|                   | IF                        | TF                |            | (  | i i |                           | Ch  | eck  |

| 02hex             | b7                        | b6                | <b>b</b> 5 | b4 | b3  | b2                        | b1  | b0   |

|                   |                           | DB1               |            |    |     |                           |     |      |

| S                 |                           |                   |            | 1  | 5   |                           |     |      |

| 17hex             | b7                        | b6                | b5         | b4 | b3  | b2                        | b1  | b0   |

|                   |                           |                   |            | DB | 22  |                           |     |      |

| 18hex             |                           |                   |            |    |     | =                         |     |      |

|                   | Unused                    |                   |            |    |     |                           |     |      |

| \$                | \$                        |                   |            |    |     |                           |     |      |

| 21hex             |                           |                   |            |    |     |                           |     |      |

|                   | Unused                    |                   |            |    |     |                           |     |      |

| 22hex             |                           |                   |            |    |     | =                         |     |      |

|                   |                           | Unused            |            |    |     |                           |     |      |

(\*1): Stores Framing Code Information (FCI). (See next page for details.)

(\*2): Values of unused bits are undefined.

Data line and line buffer address

Which data line will be captured into which line buffer can be set as shown in the below table.

| ADDRESS |           | DATA LINE               |

|---------|-----------|-------------------------|

| DECIMAL | VARLN = 0 | VARLN = 1               |

| 0       | 10H       | Set using LINE01 [3~0]. |

| 1       | 11H       | Set using LINE01 [7~4]. |

| 2       | 12H       | Set using LINE23 [3~0]. |

| 3       | 13H       | Set using LINE23 [7~4]. |

| 4       | 14H       | Set using LINE45 [3~0]. |

| 5       | 15H       | Set using LINE45 [7~4]. |

| 6       | 16H       | Set using LINE67 [3~0]. |

| 7       | 21H       | Set using LINE67 [7~4]. |

# ■ Control registers

VARLN : VARLN (0Hex W02 B4) : Selects 0: fixed line capture / 1 : variable line

capture.

LINE01~67: LINE01~LINE67: (0Hex W03~W06): Selects the line to be captured.

The line to be captured is obtained by adding an offset of 10 to the specified 4-bit value. A single data line cannot be set to be captured into

multiple line buffers.

(If this is attempted, a capture error is assumed to have occurred and the

buffer content will be undefined.)

• Framing Code Information (FCI)

Framing code information is captured into line buffer (22Hex B0) before performing error correction. The FCI value has the following meanings:

0 : FCI not detected.

FCI is not properly captured or the data line does not contain teletext data.

1 : FCI detected.

(Note): Error correction is not performed on line buffers for which FCI = 0 (i.e. an error is detected).

■ FCI for Line Buffers 7~0 are stored in FCDET (9Hex R10) with their polarity inverted. FCDET[B7~B0] corresponds to Line Buffers 7~0, respectively.

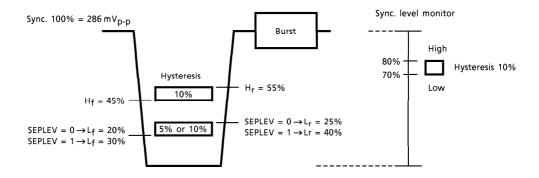

# 1.7 Sync Separation Circuit

TC90A60U incorporates a sync separation circuit to extract composite sync signals from luminance signals. It also incorporates a Sync-Tip Clamp to allow video input signals to be sliced at a fixed voltage and thereby sync signals to be generated. The slice level is automatically switched between two modes according to the Sync amplitude.

Block diagram of sync separation circuit and its peripherals

#### ■ Design specification

(The values are given for reference and does not necessarily represent the IC's actual performance.)

Input signal

Input amplitude : Luminance signal (140 IRE) 0.8  $V_{p-p} \sim 2 \ V_{p-p}$  (1  $V_{p-p}$  is recommended.) Composite video signals should be input to the IC via a buffer (Zo = 300  $\Omega$  or below recommended) after removing color signal in the LPF.

Clamp voltage : Sync. Tip =  $1.089 \text{ V (V}_{DD} = 3.3 \text{ V)}$

Slice level (when  $V_{DD} = 3.3 \text{ V}$ )

(1) Sync. amplitude: 229 mV<sub>P-P</sub> or above

H<sub>f</sub> (leading edge detection) : Sync-Tip + 129 mV H<sub>f</sub> (trailing edge detection) : Sync-Tip + 157 mV

Hysteresis : 28 mV

(2) Sync. amplitude : 200 mVp-p or below (0Hex W01 B3 SEPLEV = 0)

$L_f$  : Sync-Tip + 57 mV  $L_r$  : Sync-Tip + 71 mV

Hysteresis : 14 mV

(2)' Sync. amplitude : 200 mVp-p or below (0Hex W01 B3 SEPLEV = 1)

$L_{f}$  : Sync-Tip + 86 mV  $L_{r}$  : Sync-Tip + 114 mV

Hysteresis : 28 mV

(\*): Either (2) or (2)' can be selected using the control register.

The slice level can be expressed in percentage as shown below (when input signal is NTSC 1  $V_{P-P}$ ).

# NTSC 1 V<sub>P-P</sub> input

# Sync signal output

- Signal output delay: Within slice level + 100 ns

- Signal jitter: Within 10 ns

- Precautions regarding the sync separation circuit

- The values given in the design specification are for reference and do not necessarily represent the IC's actual performance.

- Sync signal is not output when there is no input signal.

- It takes several hundred ms (depending on the external coupling capacitance) for the clamp voltage to be stable, during which time valid output signal is not available.

- When the input signal is switched to that of a different amplitude, Sync. level may not be monitored correctly during the first field input.

# 1.8 Microcontroller Interface

TC90A60U incorporates 4-bit address bus, 8-bit data bus, 3-bit control bus and 1-bit interrupt output bus so as to allow parallel interfacing to a microcontroller.

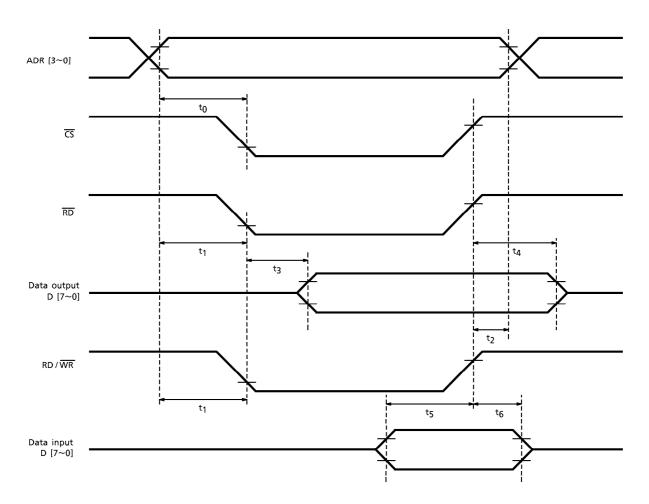

# **■** Timing chart

Microcontroller Interface AC Characteristics (Design Specification)

| PARAMETER                                        | SYMBOL         | MIN | MAX | UNIT |

|--------------------------------------------------|----------------|-----|-----|------|

| Address Setup Time Prior to CS                   | t <sub>0</sub> | 0   | _   | ns   |

| Address Setup Time Prior to RD/WR                | t <sub>1</sub> | 0   | _   | ns   |

| Address Hold Time After Deactivation of RD/WR/CS | t <sub>2</sub> | 0   | _   | ns   |

| Data Setup Time After RD                         | t <sub>3</sub> | _   | 40  | ns   |

| Data Hold Time After Deactivation of RD/CS       | t <sub>4</sub> | 3   | 18  | ns   |

| Data Setup Time Prior to Deactivation of WR      | t <sub>5</sub> | 20  | _   | ns   |

| Data Hold Time After Deactivation of WR          | t <sub>6</sub> | 0   | _   | ns   |

- Interface Access Procedure

- ① Parallel ports are used for accessing I/O registers within the IC.

- ② CS is asserted when accessing the IC.

- ③ The IC acknowledges the register to be accessed by the conditions of ADR, RD and RD/WR

- When RD is asserted along with CS, the IC acknowledges the access as a Read access and outputs the contents of the registers specified using ADR and RD on the data bus.

- (5) When either RD or CS is deasserted, the IC acknowledges the Read access to be completed and deactivates output on the data bus.

- When RD/WR is asserted along with CS, the IC acknowledges the access as a Write

access and get ready to write data in the registers specified using ADR and RD/WR.

- The data is latched into the registers on deassertion of RD/WR.

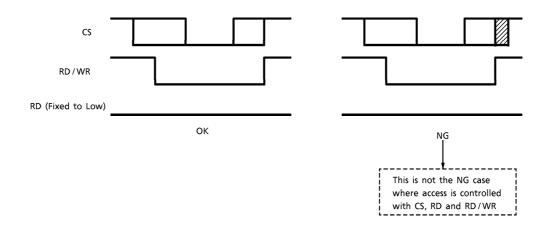

- Controlling Read/Write Access using CS and RD/WR only

Read/Write access to TC90A60U, which is usually controlled using CS, RD and RD/WR, can also be controlled with CS and RD/WR only. In that case, RD Pin must be grounded to GND, High on RD/WR Pin indicates a Read access and Low on the same pin indicates a Write access, and t3 and t4 on the preceding page depend not assertion/deassertion timing of CS, not on RD.

When access is controlled with CS and RD/WR only, an access is invalid if RD/WR is deasserted before CS is deasserted. This is not the case where access is controlled with CS, RD and RD/WR.

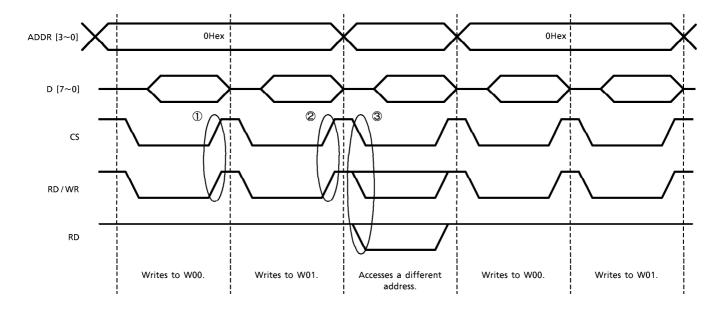

- Consecutive Read/Write from/to the Same Address

Registers W00~W07, W10~W11, W60~W61, W70~W73, R10~R11, R20~R2F and R40~R41 respectively share the same address and thus the address needs to be accessed consecutively. If an access to a different address occurs during the consecutive Read/Write access, the Read/Write resumes by accessing the first register.

- Example: An access to a different address occurs while accessing OHex registers.

- ① When a Write to W00 is complete, the address of the register to be accessed next is counted up to W01. The address is counted up in synchronization with the rising edges of CS.

- When a Write to WOL is complete the address of the register to be accessed next is counted up to WO2.

- ③ If an access to a different address occurs during a consecutive Read/Write access, the Read/Write resumes by accessing the first register (W00 in the above example).

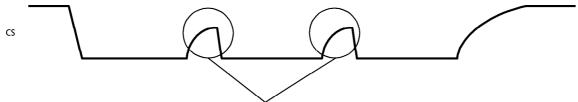

The address of the register to be accessed in consecutive Read/Write accesses is counted up in synchronization with the rising edges of CS signal. Therefore inadequate waveform and noise, as shown in the example below, could cause consecutive accesses to fail.

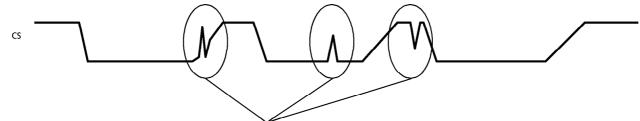

• Failed consecutive access due to inadequate waveform of CS

The next access starts before CS goes high and the consecutive access fails.

Failed consecutive access due to noise on CS

The address of the register to be accessed next is erroneously counted up if CS either goes above  $V_{IL}$  during Low output or goes below  $V_{IH}$  during High output.

#### 1.9 Monitor Pins and Their Functions

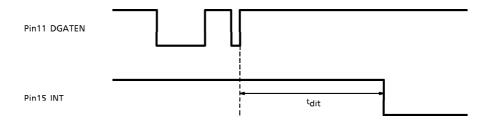

• DGATEN/SYNCO Pin (Pin 11)

This pin is used to monitor operation of internal circuits.

The signal to be monitored can be selected using DGATENSW (0Hex W01 B2).

■ DGATENSW = 0 : DGATEN monitor

Monitors internal data capture timing.

■ DGATENSW = 1 : SYNCO monitor

Monitors sync signal (C.Sync)

#### • ATTN Pin (Pin 10)

This pin is used either to output video attenuation signal or to monitor the system clock. The setting can be made in ATTNSW (0Hex W01 B7).

■ ATTNSW = 0 : Video attenuation signal output

The pin is used for attenuation control and thereby to prevent overflows of the transversal filter in the equalization circuit.

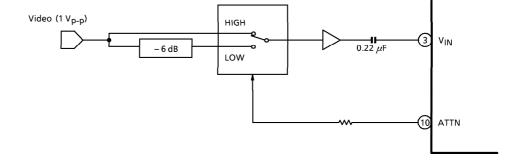

The pin is pulled LOW when the tap gain of the transversal filter reaches a certain value. The below chart shows an example of video attenuation control using ATTN Pin.

■ ATTNSW = 1 : System clock monitor

The pin is used to monitor the system clock (22.9 MHz) generated by an internal oscillator.

An example of control circuit using ATTN video attenuation output

#### 2. Data Capture Function

#### 2.1 Data Capture Mode

TC90A60U allows selection of data capture mode using control registers FC1STN (W02 B0) and FCH0G0 (W02 B1). The following explains how to use these registers.

• FC1STN (W02 B0) (initial value and recommended value : 0)

This register is used to select whether to validate only the framing code detected first (0) or all the detected framing codes (1).

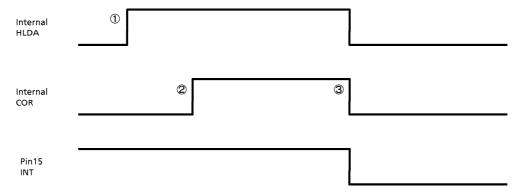

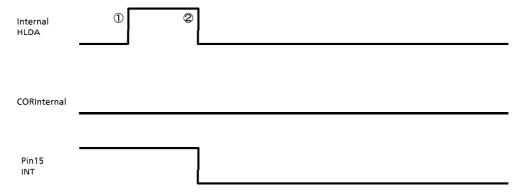

It is recommended to usually select 0 in order to avoid erroneous detections.