WD83C691A INTRODUCTION

#### INTRODUCTION 1.0

#### DESCRIPTION 1.1

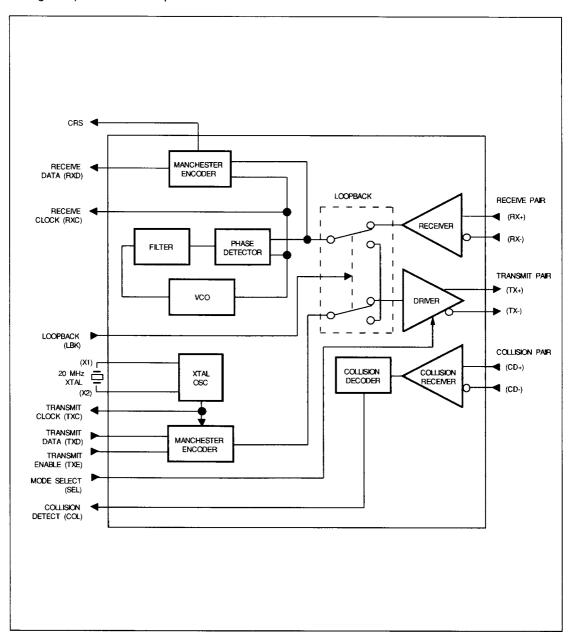

The Manchester Encoder/Decoder (MED) consists of balanced drivers and receivers, an onboard crystal oscillator, a signal translator, and a diagnostic loopback circuit. Manufactured using CMOS silicon gate technology, the device is functionally compatible with the National DP8391 Serial Network Interface (SNI).

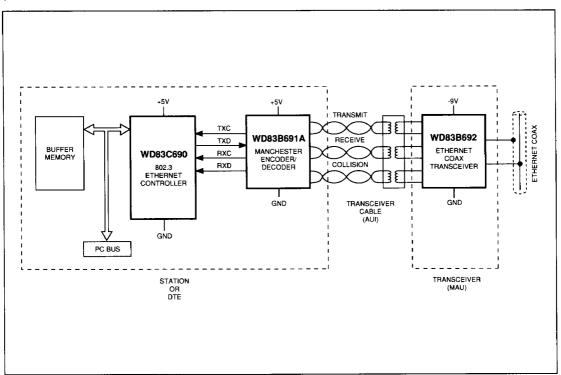

The WD83C691A is part of a three-device set that implements the complete IEEE 802.3-compatible network node electronics (see Figure 1-1). The WD83C690 Ethernet LAN Controller (ELC) and the WD83B692 Ethernet Transceiver (ET) comprise the other two devices in the set. The WD83C690 provides media access protocol functions and performs buffer management tasks, while the WD83B692 serves as a coaxial cable line driver/receiver and collision detector.

The WD83C691A Manchester Encoder/Decoder provides the interface between the WD83C690

ELC and the WD83B692 ET. When transmitting, the device converts non-return-to-zero (NRZ) data from the controller into Manchester encoded data, then sends the data to the transceiver. When receiving, the device reverses the process using an analog phase-locked loop that decodes 10 Mbit/sec signals with up to 18 nsec of jitter.

This document describes the operation of the WD83C691A Manchester Encoder/Decoder, and provides information on the following functional blocks:

- Oscillator

- Manchester Encoder and Differential Driver

- Manchester Decoder

- Collision Translator

- Loopback Capabilities

The appendices provide pin designations, electrical operating and switching characteristics, and timing and package diagrams.

FIGURE 1-1, WD83C691A SYSTEM INTERFACE

## 1.2 FEATURES

- Compatible with Ethernet II (10BASE5) and Cheapernet (10BASE2) IEEE 802.3 standards

- Incorporates low power, 1.25 CMOS technology

- Provides 10 Mbps Manchester encoding/ decoding with receive clock recovery

- Connects directly to the transceiver (AUI) cable

- Provides 16V fault protection at the transceiver interface

- TTL/MOS-compatible controller interface

- Features externally-selectable half- or full-step modes of operation at transmit output

- Incorporates squelch circuits at receive and collision inputs to reject noise

- Provides loopback capability for diagnostics

## 2.0 OPERATIONAL DESCRIPTION

This section describes the five basic components of the WD83C691A.

#### 2.1 Oscillator

Control is provided either by a 20 MHz, parallel resonant crystal connected between X1 and X2, or by an external clock connected at X1. The oscillator's 20-MHz output is divided in half to generate the 10-MHz transmit clock for the Ethernet LAN controller and to provide the internal clock signals for the encoding and decoding circuits.

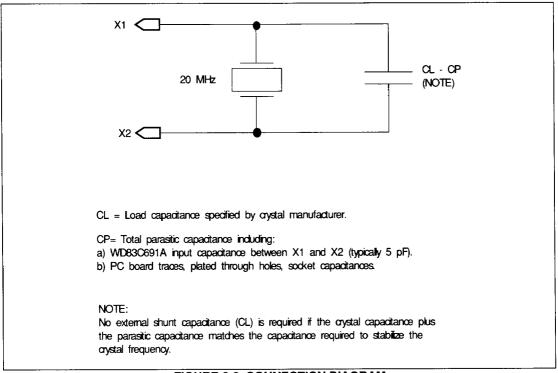

The IEEE 802.3 standard requires 0.01% absolute accuracy on the transmitted signal frequency. Stray capacitance, however, can shift the crystal's frequency out of range, causing it to exceed the 0.01% tolerance. To remedy this, you may need to add extra load capacitance.

To determine the amount of capacitance to add, measure the board capacitance and the capacitance between the X1 and X2 pins. Then add these values together, and subtract them from the crystal's required load capacitance. (Refer to Figure 2-2.)

#### 2.2 Manchester Encoder/Differential Driver

Data encoding and transmission begin when the transmit enable input (TXE) goes high, and continue as long as the TXE remains high. It is essential that the transmit enable and transmit data inputs meet the setup and hold time requirements in relation to the rising edge of the transmit clock. Transmission ends when the transmit enable input goes low. The last transition occurs at the center of the bit cell if the last bit is one, or at the boundary of the bit cell if the last bit is zero.

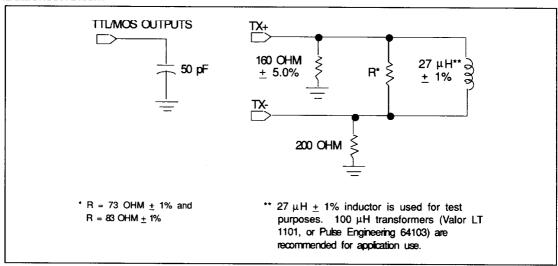

The differential line driver, which has the ability to drive up to 50 meters of twisted pair AUI/ Ethernet transceiver cable, provides the emitter-coupled logic (ECL) level signals. The outputs consist of current drivers that must be loaded with external 1602 pull-down resistors.

With the SEL input, one of two modes can be selected, full-step or half-step. When SEL is low, TX+ is positive in relation to TX- in the idle state. When SEL is high, TX+ and TX- are equal in the

idle state. Figures C1 through C3 illustrate transmit timing.

#### 2.3 Manchester Decoder

Decoding is accomplished by a differential input receiver circuit and an analog phase-locked loop that separate the Manchester-encoded data stream into clock signals and NRZ data. With the standard 782 transceiver drop cable, the differential input must be externally terminated. This requirement can be satisfied by connecting two 392 resistors in series with one optional common mode bypass capacitor.

To prevent noise at the input from falsely triggering the decoder, a squelch circuit rejects signals with pulse widths less than 20 nsec (negative going), or with levels less than -175 mV. When the input exceeds the squelch requirements, the analog phase-locked loop locks onto the incoming signal and the WD83C691A decodes a data frame. The carrier sense (CRS) is activated, and the receive data (RXD) and receive clock (RXC) become available within five bit times. At the end of a frame, when the normal mid-bit transition on the differential input ceases, carrier sense is deactivated. The receive clock remains active for an additional six bit times before subsiding. Figures C-4 through C-6 illustrate receive timing.

#### 2.4 Collision Translator

The Ethernet transceiver detects collisions on the coaxial cable and generates a 10-MHz signal, which is monitored by the WD83C691A through the collision detect pins. The presence of the signal activates the collision detect (CD) pin connected to the WD83C690, and causes the controller to stop transmitting. The collision detect output is deactivated within 350 nsec after the absence of the 10-MHz signal. (Figure C-7 illustrates the collision timing.) Make sure that the collision differential inputs are terminated in exactly the same manner as the receive inputs.

41

v.DataSheet4U.com

## 2.5 Loopback Functions

A logic "1" on the loopback input causes the WD83C691A to send serial data from the transmit data input through the encoder, and back through the phase-locked loop decoder to

receive the output data. The transmit driver is in the idle state during loopback mode and the receiver circuitry is disabled.

FIGURE 2-1. WD83C691A GENERAL SYSTEM BLOCK DIAGRAM

www.DataSheet4U.com

## 2.6 CRYSTAL SPECIFICATIONS

Resonant Frequency:

20 MHz

Overall Tolerance:

0.005% at 25°C (77°F)

Type:

AT-Cut

Temperature Tolerance:

0.005% 0°C (32°F) to 70°C (158°F)

Circuit Type:

Parallel resonance (refer to Figure 2-2 for crystal connection diagram).

**FIGURE 2-2. CONNECTION DIAGRAM**

JataSheet4U.com

## **APPENDIX A - PIN DESIGNATIONS**

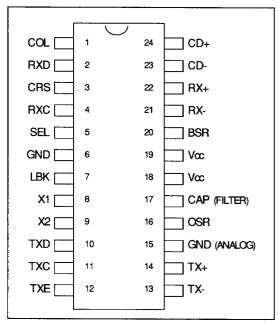

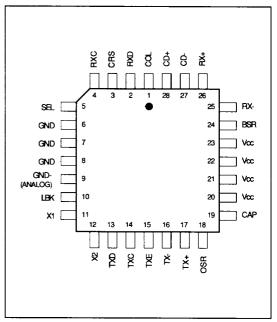

This Appendix provides information on the 24-Pin DIP and 28-Pin PLCC devices. Figures A-1 and A-2 depict the devices, and Table A-1 lists all pin designations.

FIGURE A-1. WD83C691-PG 24-Pin DIP Manchester Encoder/Decoder

FIGURE A-2. WD83C691-JH 28-Pin PLCC Manchester Encoder/Decoder

| DIP<br>PINS | PLCC<br>PINS | MNEMONIC | SIGNAL NAME                   | DESCRIPTION/FUNCTION                                                                                                                                                                                                                                                                                    |

|-------------|--------------|----------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | 1            | COL      | COLLISON DETECT<br>OUTPUT     | TTL/MOS level active high output. A 10-MHz signal at the collision input produces a logic high at COL output. When there is no signal at the collision input, COL output is low.                                                                                                                        |

| 2           | 2            | RXD      | RECEIVE DATA<br>OUTPUT        | TTL/MOS level output. This is the NRZ data from the analog phase-locked loop. This signal is sampled by the controller at the rising edge of the receive clock.                                                                                                                                         |

| 3           | 3            | CRS      | CARRIER SENSE                 | TTL/MOS level active high output. The output is activated when there is valid data from the transceiver at the receive input. It is deactivated two bit times after the last bit at receive point.                                                                                                      |

| 4           | 4            | RXC      | RECEIVE CLOCK                 | TTL/MOS level recovered clock output. When the analog phase-locked loop locks to a valid incoming signal, a 10-MHz clock signal is activated on this output, which remains low during idle (5 bit times after activity ceases at receive input.)                                                        |

| 5           | 5            | SEL*     | MODE SELECT                   | When high, the TX+ and TX- outputs have the same voltage in idle state, providing a "zero" differential. When low, TX+ is positive with respect to TX-in idle state.                                                                                                                                    |

| 6           | 6-8          | GND      | GROUND                        |                                                                                                                                                                                                                                                                                                         |

| 7           | 10           | LBK      | LOOPBACK                      | TTL/MOS level active high on this input enables the loopback mode.                                                                                                                                                                                                                                      |

| 8           | 11           | X1       | CRYSTAL1                      | Crystal or external frequency source input (TTL).                                                                                                                                                                                                                                                       |

| 9           | 12           | X2       | CRYSTAL<br>FEEDBACK<br>OUTPUT | This output is used only in the crystal connection, and must be left open when driving X1 with an external frequency source.                                                                                                                                                                            |

| 10          | 13           | TXD      | TRANSMIT DATA                 | TTL/MOS level input. When transmit enable input is high, this signal is sampled by the WD83C691A at the rising edge of the transmit clock. The WD83C691A combines transmit data and transmit clock signals to produce a Manchester-encoded bit stream, which is sent differentially to the transceiver. |

TABLE A-1. PIN DESCRIPTIONS

| DIP<br>PINS | PLCC<br>PINS | MNEMONIC | SIGNAL NAME         | DESCRIPTION/FUNCTION                                                                                                                                |

|-------------|--------------|----------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 11          | 14           | TXC      | TRANSMIT<br>CLOCK   | Derived from the 20-MHz oscillator,<br>This TTL/MOS level 10-MHz clock<br>output is always active.                                                  |

| 12          | 15           | TXE      | TRANSMIT<br>ENABLE  | TTL/MOS level active high data encoder enable input, sampled by the WD83C691A at the rising edge of the transmit clock.                             |

| 13,14       | 16,17        | TX-,TX+  | TRANSMIT<br>OUTPUT  | These outputs are current drivers and require 160 $\pm$ 5.0% Ohm pull-down resistors to GND.                                                        |

| 15          | 9            | GND      | GROUND              | System analog ground.                                                                                                                               |

| 16          | 18           | OSR      | VCO RESISTOR        | A 31.6 ± 1.0% Kbyte, bias oscillator resistor connected between this pin and a VCC pin.                                                             |

| 17          | 19           | CAP      | FILTER<br>CAPACITOR | A ceramic capacitor must be connected from this output pin to ground as close to the part as possible. The capacitor must be .01 $\mu$ F $\pm$ 10%. |

| 18,19       | 20-23        | VCC      | VCC                 | +5V positive supply pins. A 0.1μ F ceramic decoupling capacitor must be connected across VCC and GND, as close to the device as possible.           |

| 20          | 24           | BSR      | BIAS RESISTOR       | A 10.0 $\pm$ 1.0% Kbyte bias resistor connects beween this pin and a VCC pin.                                                                       |

| 21,22       | 25,26        | RX-,RX+  | RECEIVE INPUT       | Differential receive input pair from the transceiver.                                                                                               |

| 23,24       | 27,28        | CD-,CD+  | COLLISION<br>OUTPUT | Differential collision input pair from transceiver.                                                                                                 |

# **TABLE A-1. PIN DESCRIPTIONS, Continued**

<sup>\*</sup>SEL is not a TTL/MOS level input. The VCO frequency can be observed at RXC when SEL is forced to one-half Vcc (for test purposes).

www.DaiaSheei4U.com

# APPENDIX B - ELECTRICAL OPERATING CHARACTERISTICS

Ta = 0°C (32°F) to 70°C (158°F),  $Vcc = +5V \pm 5\%$  (Refer to note after table)

| SYMBOL          | CHARACTERISTIC                                 | MIN  | MAX  | UNITS       | CONDITIONS                                                 |

|-----------------|------------------------------------------------|------|------|-------------|------------------------------------------------------------|

| V <sub>IH</sub> | Input High Voltage<br>(TTL and X1)             | 2.0  | _    | V           |                                                            |

| V <sub>IH</sub> | Input High Voltage<br>(SEL)                    | 4.0  | -    | V           | -                                                          |

| VIL             | Input Low Voltage<br>(TTL and X1)              | -    | 0.8  | V           | -                                                          |

| VIL             | Input Low Voltage<br>(SEL)                     | -    | 1.0  | V           |                                                            |

| lін             | Input High Current                             | -    | 10   | μА          | Vin = Vcc                                                  |

|                 | (TTL)<br>Input High Current<br>(RX±, CD±)      | -    | 10   | μА          | Vin = Vcc                                                  |

| IIL             | Input Low Current                              | -    | -10  | μΑ          | Vin = 0.5V                                                 |

|                 | (TTL)<br>Input Low Current<br>(RX±, CD±)       | -    | -500 | μА          | Vin = 0.5V                                                 |

| V <sub>CL</sub> | Input Clamp Voltage<br>(TTL)                   | -    | -1.2 | V           | lin = -12mA                                                |

| Vон             | Output High Voltage<br>(TTL/MOS)               | 3.5  | -    | <b>&gt;</b> | loh = -100 μA                                              |

| V <sub>OL</sub> | Output Low Voltage<br>(TTL/MOS)                | -    | 0.5  | V           | lol = 8mA                                                  |

| ics             | Output Short Circuit<br>Current (TTL/MOS)      | -40  | -200 | mA          | -                                                          |

| V <sub>OD</sub> | Differential Output<br>Voltage (TX±)           | ±450 | ±120 | mV          | $78\Omega$ termination and $200\Omega$ from each to ground |

| V <sub>OB</sub> | Differential Output<br>Voltage Imbalance (TX±) | -    | ±40  | mV          | $78\Omega$ termination and $200\Omega$ from each to ground |

| V <sub>DS</sub> | Differential Squelch<br>Threshold (RX± CD±)    | -175 | -300 | mV          | -                                                          |

| V <sub>CM</sub> | Input Common Mode<br>Voltage (RX± CD±)         | 0    | 7.0  | V           | -                                                          |

| icc             | Power Supply Current                           | -    | 80   | mA          | 10 Mbit/sec                                                |

TABLE B-1. ELECTRICAL OPERATING CHARACTERISTICS

NOTE: All currents into device pins are positive. All currents out of device pins are negative. All voltages are referenced to ground unless otherwise specified.

All typical values are given for Vcc = 5V and Ta = 25°C (77°F)

## **ABSOLUTE MAXIMUM RATINGS**

Supply Voltage (Vcc) 6

TTL Input Voltage 0 - 5.5V

Differential Input Voltage -5.5 - 16V

Differential Output Voltage 0 - 16V

Differential Output Current -40 mA

Storage Temperature -65°C (-85°F) to 150° (302°F)

Absolute maximum ratings indicate limits beyond which permanent damage may occur. Continuous operation at these limits is not recommended; operation should be limited to conditions specified under DC Operating Characteristics.

## RECOMMENDED OPERATING CONDITIONS

Supply Voltage (Vcc) 5V ±5%

Ambient Temperature 0°C (32°F) to 70°C (158°F)

# **APPENDIX C - SWITCHING CHARACTERISTICS**

Ta = 0°C (32°F) to 70°C (158°F),  $V\infty = +5V \pm 5\%$  (Refer to note after table)

| SYMBOL           | PARAMETER                                                       | MIN | TYP   | MAX | UNITS |

|------------------|-----------------------------------------------------------------|-----|-------|-----|-------|

| Oscillator       | Specification                                                   |     |       |     |       |

| tхтн             | X1 to Transmit Clock High                                       | 8   | -     | 20  | nsec  |

| txtl             | X1 to Transmit Clock Low                                        | 8   | -     | 20  | nsec  |

| Transmit S       | Specification                                                   |     |       |     |       |

| tTCD             | Transmit Clock Duty<br>Cycle at 1.5V (10 MHz)                   | 42  | 50    | 58  | %     |

| tTCR             | Transmit Clock Rise<br>Time (1.1V to 2.9V)                      | _   | -     | 10  | nsec  |

| trcf             | Transmit Clock Fall<br>Time (2.9V to 1.1V)                      | -   | -     | 10  | nsec  |

| tтрs             | Transmit Data Setup<br>Time to Transmit<br>Clock Rising Edge    | 20  | -     | -   | nsec  |

| tтрн             | Transmit Data Hold<br>Time from Transmit<br>Clock Rising Edge   | 0   | -     | -   | nsec  |

| ttes             | Transmit Enable Setup<br>Time to Transmit<br>Clock Rising Edge  | 20  | -     | -   | nsec  |

| tтен             | Transmit Enable Hold<br>Time from Transmit<br>Clock Rising Edge | 0   | -     | -   | nsec  |

| ttop             | Transmit Output Delay<br>from Transmit Clock<br>Rising Edge     | -   | -     | 40  | nsec  |

| t <sub>TOR</sub> | Transmit Output Rise<br>Time (20% to 80%)                       | -   | -     | 7   | nsec  |

| t <sub>TOF</sub> | Transmit Output Fall<br>Time (80% to 20%)                       | -   | -     | 7   | nsec  |

| tTOJ             | Transmit Output Jitter                                          | -   | ±0.25 | -   | nsec  |

| <b>t</b> тон     | Transmit Output High<br>Before Idle in Half<br>Step Mode        | 200 | -     | -   | nsec  |

| tTOI             | Transmit Output Idle Time in Half Step Mode                     | -   | -     | 800 | nsec  |

| Receive S        | pecification                                                    |     |       |     |       |

| trod             | Receive Clock Duty<br>Cycle at 1.5V (10 MHz)                    | 40  | 50    | 60  | %     |

| trcr             | Receive Clock Rise<br>Time (1.1V to 2.9V)                       | -   | -     | 10  | nsec  |

| trcf             | Receive Clock Fall<br>Time (2.9V to 1.1V)                       | -   | -     | 8   | nsec  |

**TABLE C-1. SWITCHING CHARACTERISTICS**

| SYMBOL           | PARAMETER                                                 | MIN | TYP | MAX       | UNITS |

|------------------|-----------------------------------------------------------|-----|-----|-----------|-------|

| Receive S        | pecification, continued                                   |     |     |           |       |

| trdr             | Receive Data Rise<br>Time (20% to 80%)                    | -   | -   | 8         | nsec  |

| t <sub>RDF</sub> | Receive Data Fall<br>Time (80% to 20%)                    | -   | -   | 8         | nsec  |

| t <sub>RDS</sub> | Receive Data Stable<br>From Receive Clock<br>Rising Edge  | 40  | -   | -         | nsec  |

| tcson            | Carrier Sense Turn<br>on Delay                            | -   | -   | 50        | nsec  |

| tcsoff           | Carrier Sense Turn off Delay                              | -   | -   | 160       | nsec  |

| tDAT             | Decoder Acquisition Time                                  | -   | -   | 700       | nsec  |

| torej            | Differential Inputs<br>Rejection Pulse<br>Width (Squelch) | 8   | -   | 30        | nsec  |

| t <sub>RD</sub>  | Receive Throughout<br>Delay                               | _   | -   | 150       | nsec  |

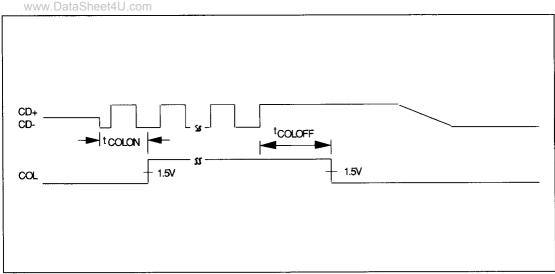

| Collision        | Specification                                             |     | ·   | · · · · · |       |

| tcolon           | Collision Turn On Delay                                   | -   | -   | 50        | nsec  |

| tcoloff          | Collision Turn Off Delay                                  | -   | -   | 350       | nsec  |

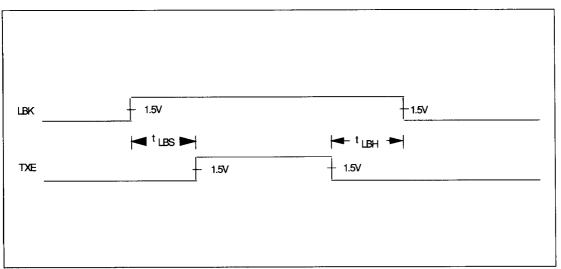

| Loopback         | Specification                                             |     |     | - · · -   |       |

| tLBS             | Loopback Setup Time                                       | 20  | -   | -         | nsec  |

| tlbH             | Loopback Hold Time                                        | 0   | -   | -         | nsec  |

TABLE C-1. SWITCHING CHARACTERISTICS, Continued

NOTE: All typical values are given for Vcc = 5V and Ta = 25°C (77°F).

WD83C691A

www.DataSheet4U.com

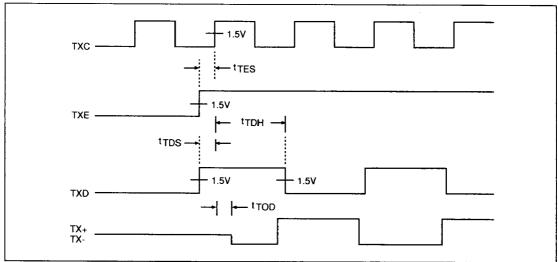

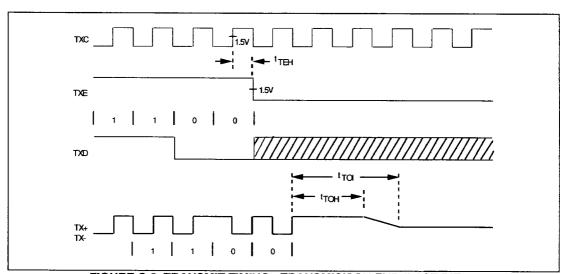

# **TIMING DIAGRAMS**

Table C-2 lists all timing diagrams. Figures C-1 through C-9 illustrate all timings.

| Figure<br>Number | Title                                              |  |  |  |

|------------------|----------------------------------------------------|--|--|--|

| C-1              | Transmit Timing Start of Transmission              |  |  |  |

| C-2              | Transmit Timing End of Transmission (last bit = 0) |  |  |  |

| C-3              | Transmit Timing End of Transmission (last bit = 1) |  |  |  |

| C-4              | Receive Timing Start of Packet                     |  |  |  |

| C-5              | Receive Timing End of Packet (last bit = 0)        |  |  |  |

| C-6              | Receive Timing End of Packet (last bit = 1)        |  |  |  |

| C-7              | Collision Timing                                   |  |  |  |

| C-8              | Loopback Timing                                    |  |  |  |

| C-9              | Test Loads                                         |  |  |  |

TABLE C-2. WD83C691A TIMING DIAGRAMS

FIGURE C-1. TRANSMIT TIMING - TRANSMISSION START

FIGURE C-2. TRANSMIT TIMING - TRANSMISISON END (LAST BIT=0)

WD83C691A

www.DataSheet4U.com

FIGURE C-3. TRANSMIT TIMING - TRANSMISSION END (LAST BIT=1)

FIGURE C-4. RECEIVE TIMING - START OF PACKET

FIGURE C-5. RECEIVE TIMING - END OF PACKET (LAST BIT = 0)

FIGURE C-6. RECEIVE TIMING - END OF PACKET (LAST BIT = 1)

TIMING DIAGRAMS WD83C691A

FIGURE C-7. COLLISION TIMING

FIGURE C-8. LOOPBACK TIMING

FIGURE C-9. TEST LOADS

1/2

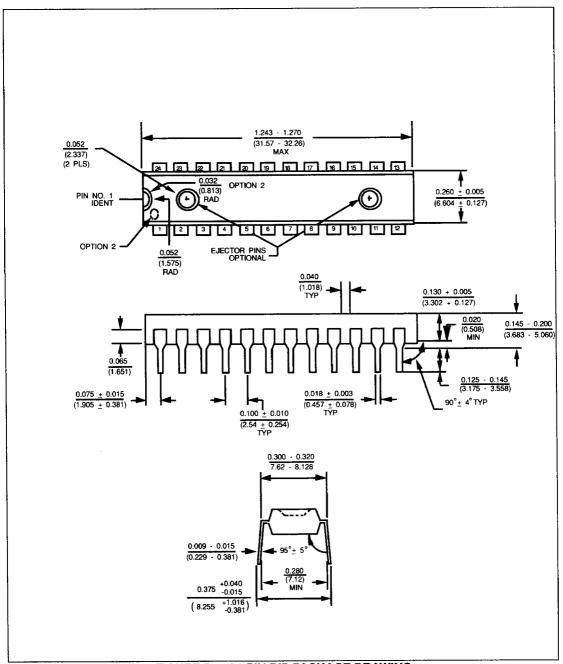

# **APPENDIX D - PACKAGE DIAGRAMS**

Figures D-1 and D-2 are illustrations of the 24-Pin DIP and 28-Pin PLCC packages showing dimensions in inches.

FIGURE D-1. 24-PIN DIP PACKAGE DRAWING

41

0.075 (8 PLCS) 0.170 REF 1.905 0.170 REF 0.008 0.203 0.008 0.203 1.143 0.050 REF. LOCATING 0.711 0.127 CHAMFER 0.018 0.018 0.457 0.045 1.143 0.490 ± 0.015 0.028 (23 PLCS) 0028 (23 FLCS) 12.446 ± 0.38 0.005 0.127mm 0.127mm 0.045 - 0.055 0.045 - 0.055 1.143 - 1.397 1.143 - 1.397 0.490 ± 0.015 12.446 ± 0.38 OPTION 'A' OPTION 'B' 0.045 DIA PIN No.1 ID 1.143 0.022 SURFACE SPOT POLISHED 0.001 - 0.003 0.025 - 0.076 OPTION 'C'

FIGURE D-2, 28-PIN PLCC PACKAGE DRAWING