#### MITSUBISHI MICROCOMPUTERS

## **3817 Group**

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

#### DESCRIPTION

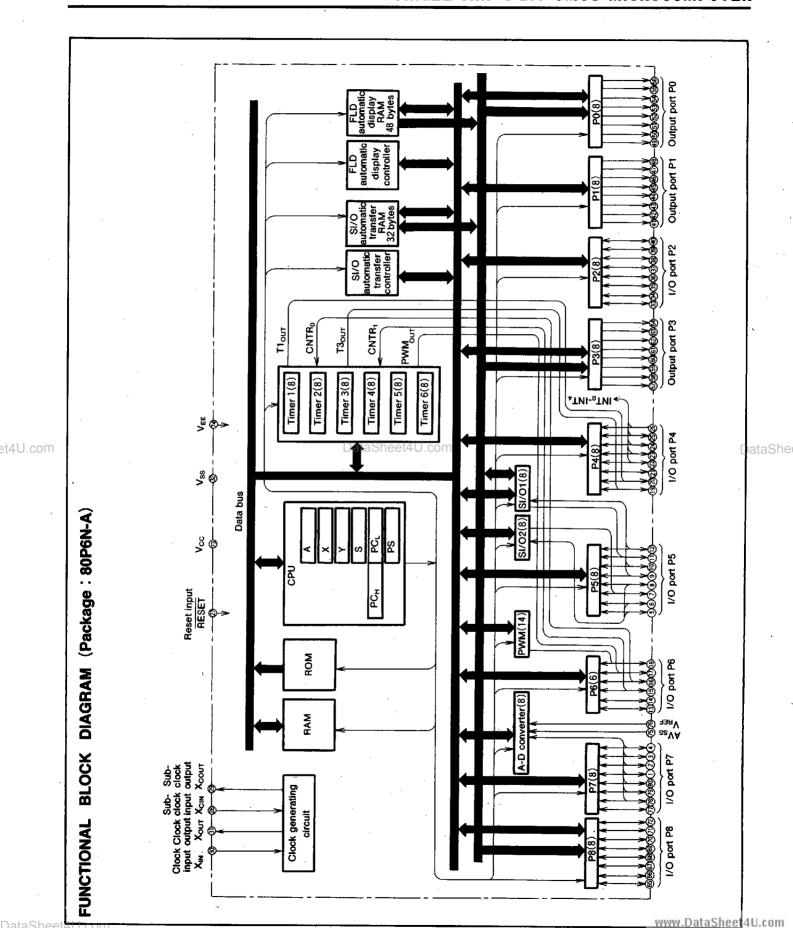

The 3817 group is 8-bit microcomputer based on the 740 family core technology.

The 3817 group is designed mainly for VCR timer/function control, and include six 8-bit timers, a fluorescent display automatic display circuit, a PWM function, and an 8-channel A-D converter.

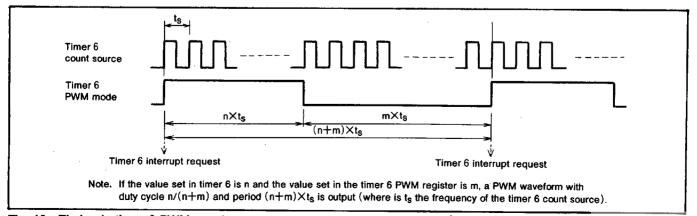

The various microcomputers in the 3817 group include variations of internal memory size and packaging. For details, refer to the section on part numbering.

For details on availability of microcomputers in the 3817 group, refer to the section on group expansion.

#### **FEATURES**

| • | Basic machine-language instructions 71        |

|---|-----------------------------------------------|

| • | The minimum instruction execution time 0.63µs |

|   | (at 6.3MHz oscillation frequency)             |

| • | Memory size                                   |

|   | ROM ····· 4K to 60K bytes                     |

|   | RAM192 to 1024 bytes                          |

| • | Programmable input/output ports 45            |

| • | High-breakdown-voltage output ports ····· 32  |

| • | Interrupts                                    |

P75/AN5

P74/AN4

| • Timers 8-bit×6                                                                           |

|--------------------------------------------------------------------------------------------|

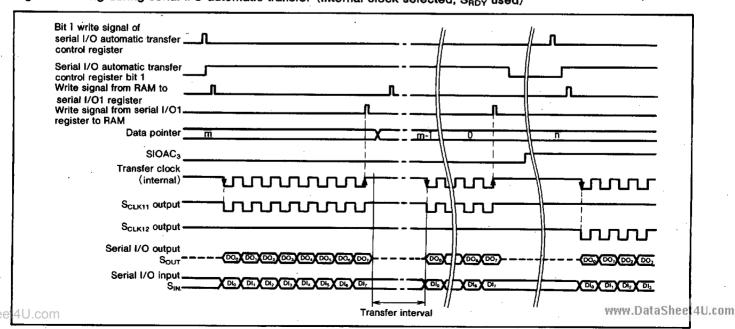

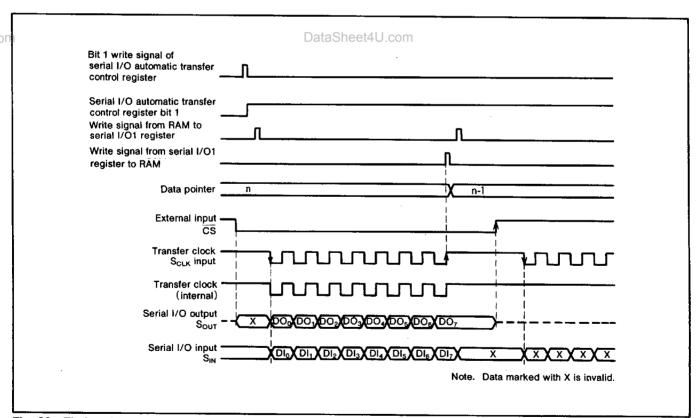

| ● Serial I/O ··························Clock-synchronized 8-bit×2                          |

| (Serial I/O1 has an automatic data transfer function)                                      |

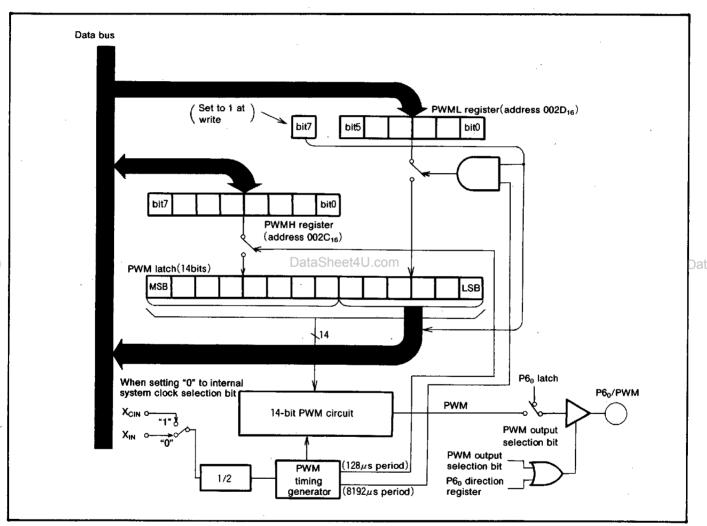

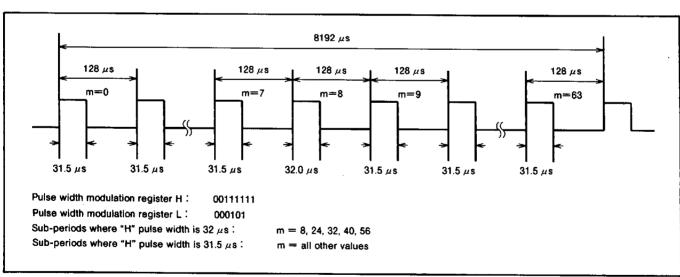

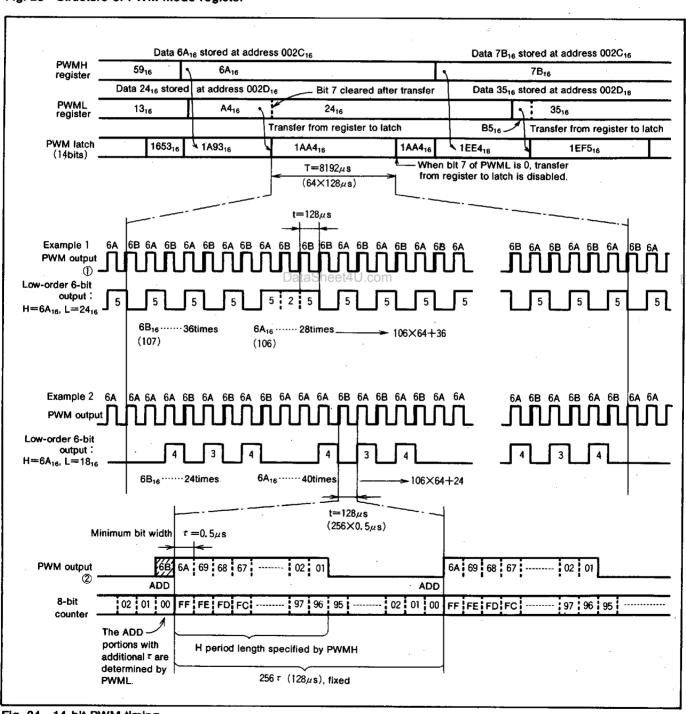

| PWM output circuit14-bitX1                                                                 |

| 8-bit×1(also functions as timer 6)                                                         |

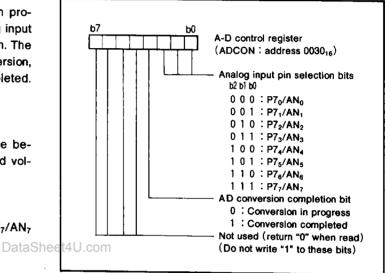

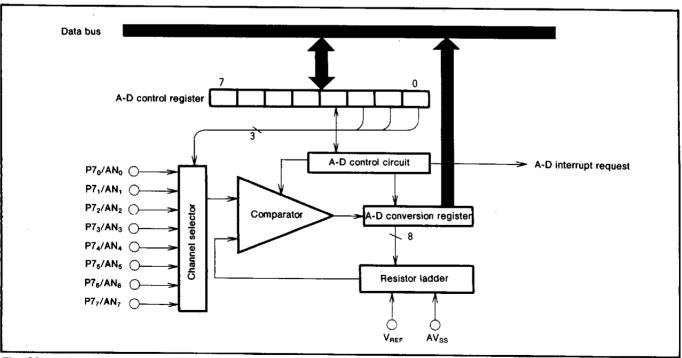

| A-D converter 8-bit × 8 channels                                                           |

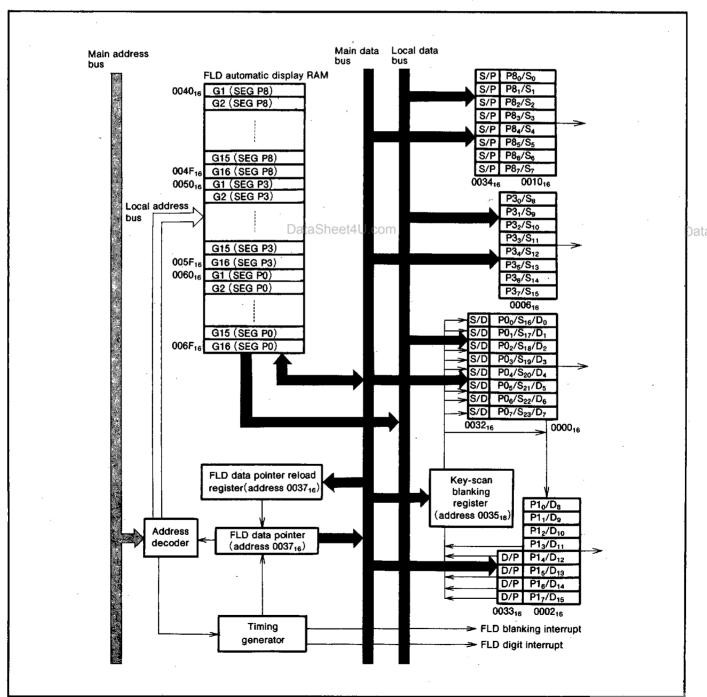

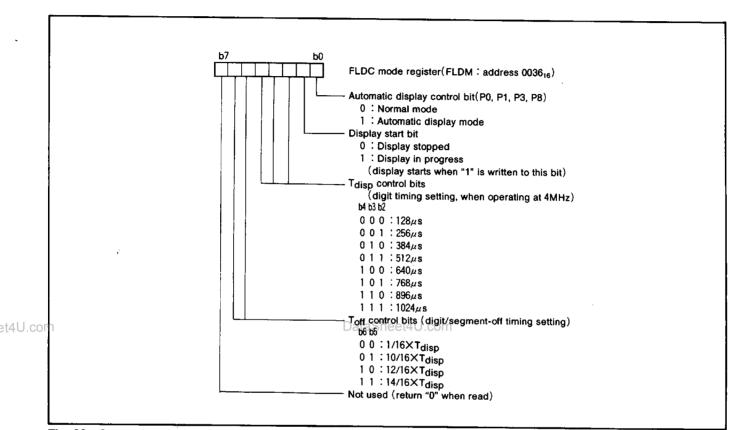

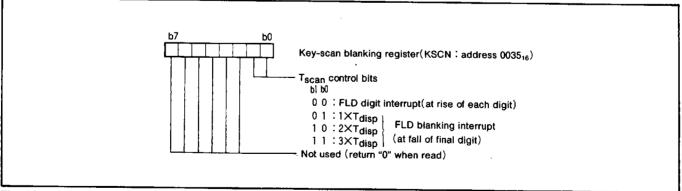

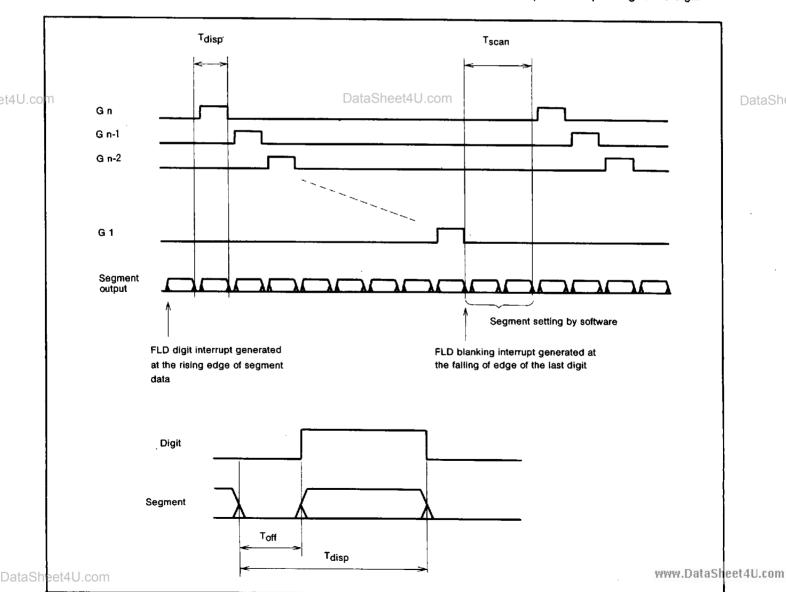

| Fluorescent display function                                                               |

| Segments 8 to 24                                                                           |

| Digits 4 to 16                                                                             |

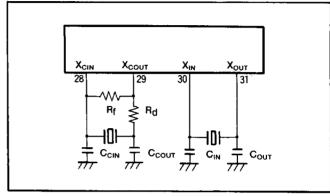

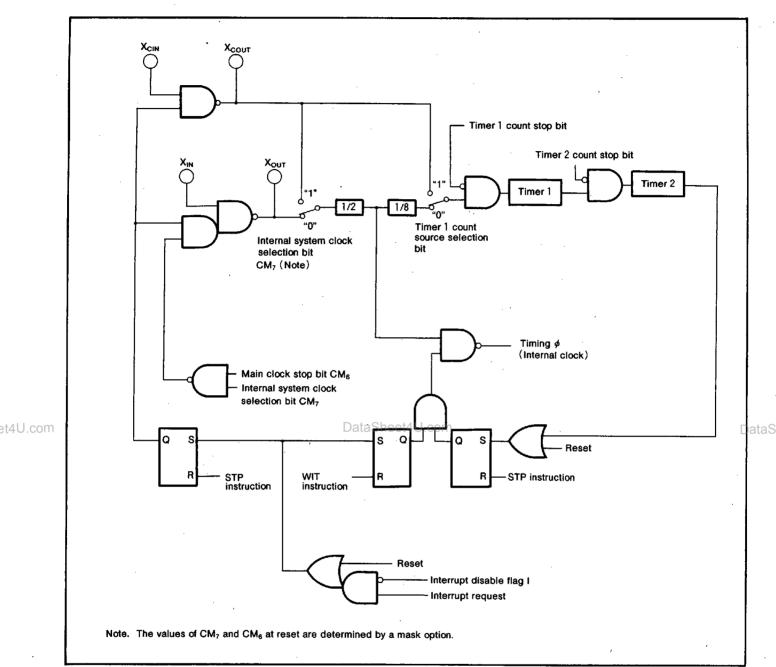

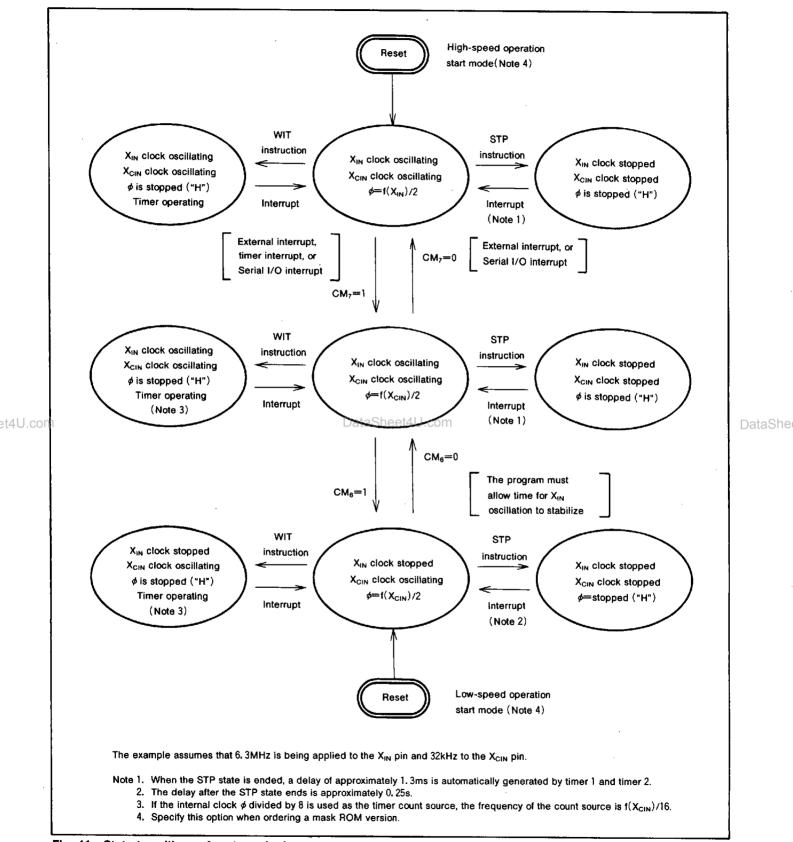

| 2 Clock generating circuit                                                                 |

| Clock (X <sub>IN</sub> -X <sub>OUT</sub> )Internal feedback resistor                       |

| Sub-clock (X <sub>CIN</sub> -X <sub>COUT</sub> ) ·······Without internal feedback resistor |

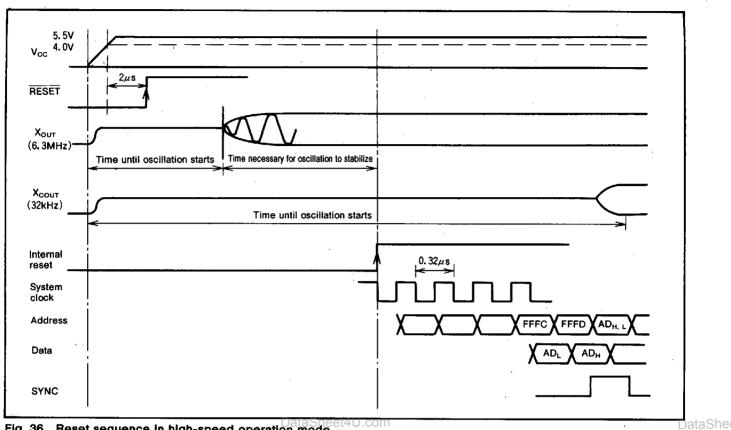

| Power source voltage4.0 to 5.5V                                                            |

| Power dissipation                                                                          |

| In high-speed mode ·······38mW                                                             |

| (at 6.3MHz oscillation frequency)                                                          |

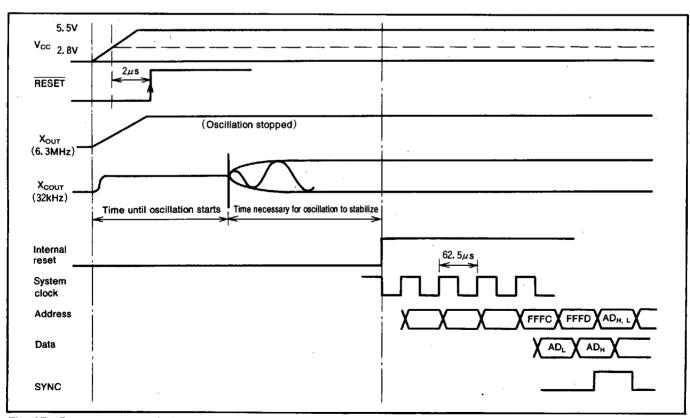

| In low-speed mode ························· 300 $\mu$ W                                    |

| (at 32kHz oscillation frequency)                                                           |

| Operating temperature range ······ −10 to +85℃                                             |

| APPLICATIONS                                                                               |

| VCRs, tuners, musical instruments, office automation, etc.                                 |

|                                                                                            |

P4<sub>0</sub>/INT<sub>0</sub>

#### PIN CONFIGURATION (TOP VIEW) 111111111111 P8<sub>7</sub>/SEG<sub>7</sub> P86/SEG6 P85/SEG5 P8<sub>4</sub>/SEG<sub>4</sub> P2<sub>3</sub> P83/SEG3 P24 P82/SEG2 P25 P8<sub>1</sub>/SEG<sub>1</sub> P26 P8<sub>0</sub>/SEG<sub>0</sub> P27 M38173M6-XXXFP Vcc V<sub>SS</sub> VEE Xout AVSS XIN VAEF **XCOUT** P77/AN7 X<sub>CIN</sub> RESET P76/AN6

Package type: 80P6N-A

80-pin plastic molded QFP

www.DataSheet4U.com

DataSheet4U.com

DataSheet4U.com

DataShe

DataSheet4U.com

#### PIN DESCRIPTION

|                                       |                                                                                                                        |                            |                                                                                                                                                                                                                                                                                                                                                                             | · · · · · · · · · · · · · · · · · · · |  |  |  |  |  |  |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|--|--|--|--|--|

|                                       | Pin                                                                                                                    | Name                       | Function ·                                                                                                                                                                                                                                                                                                                                                                  | Function except a port function       |  |  |  |  |  |  |

| -                                     | V <sub>CC</sub> , V <sub>SS</sub>                                                                                      | Power source               | Apply voltage of 4.0 to 5.5V to V <sub>CC</sub> , and 0V to V <sub>SS</sub> .                                                                                                                                                                                                                                                                                               | · · · · · · · · · · · · · · · · · · · |  |  |  |  |  |  |

|                                       | VEE                                                                                                                    | Pull-down power input      | Applies voltage supplied to pull-down resistors of ports P0                                                                                                                                                                                                                                                                                                                 | , P1 and P3.                          |  |  |  |  |  |  |

|                                       | V <sub>REF</sub>                                                                                                       | Analog reference voltage   | • Reference voltage input pin for A-D converter                                                                                                                                                                                                                                                                                                                             |                                       |  |  |  |  |  |  |

|                                       | AV <sub>ss</sub>                                                                                                       | Analog power source        | GND input pin for A-D converters     Connect to Vss.                                                                                                                                                                                                                                                                                                                        |                                       |  |  |  |  |  |  |

|                                       | RESET                                                                                                                  | Reset input                | Reset input pin for active "L"                                                                                                                                                                                                                                                                                                                                              |                                       |  |  |  |  |  |  |

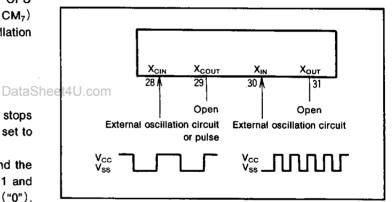

|                                       | X <sub>IN</sub>                                                                                                        | Clock input                | Input and output signals for the Internal clock generating circuit.     It consist of internal feedback resistor.                                                                                                                                                                                                                                                           |                                       |  |  |  |  |  |  |

| .                                     | X <sub>OUT</sub>                                                                                                       | Clock output               | <ul> <li>Connect a ceramic resonator or quartz-crystal oscillator between the X<sub>IN</sub> and X<sub>OUT</sub> plns to set the oscillation frequency.</li> <li>If an external clock is used, connect the clock source to the X<sub>IN</sub> pin and leave the X<sub>OUT</sub> pln open.</li> <li>This clock is used as the oscillating source of system clock.</li> </ul> |                                       |  |  |  |  |  |  |

|                                       | X <sub>CIN</sub>                                                                                                       | Sub-clock input            | <ul> <li>Input and output signals for the sub-clock generating circuit.</li> <li>It consist of without internal feedback resistor.</li> <li>Connect a ceramic resonator or quartz-crystal oscillator and external feedback resistor between the X<sub>CIN</sub> and X<sub>COUT</sub> pins.</li> </ul>                                                                       |                                       |  |  |  |  |  |  |

| 4U.com                                | Хсоит                                                                                                                  | Sub-clock output           | If an external clock is used, connect the clock source to the X <sub>CIN</sub> pin and leave the X <sub>COUT</sub> pin open.      This clock can also be used as the oscillating source of system clock.      Data Sheet 41.1.                                                                                                                                              |                                       |  |  |  |  |  |  |

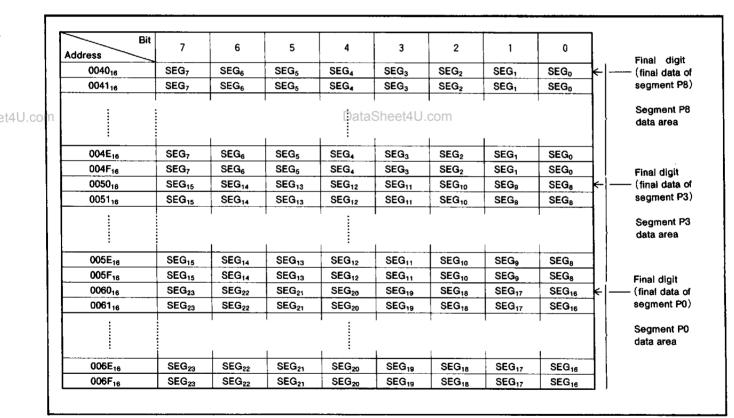

|                                       | P0 <sub>0</sub> /SEG <sub>10</sub> /<br>DIG <sub>0</sub> -<br>P0 <sub>7</sub> /SEG <sub>23</sub> /<br>DIG <sub>7</sub> | Output port P0             | 8-bit output port     The output structure is high-breakdown-voltage P-channel open drain with internal pull-down resistors connected between the output and the V <sub>EE</sub> pin.     At reset this port is set to V <sub>EE</sub> pin level.                                                                                                                           | • FLD automatic display pins          |  |  |  |  |  |  |

|                                       | P1 <sub>0</sub> /DIG <sub>8</sub> -<br>P1 <sub>7</sub> /DIG <sub>15</sub>                                              | Output port P1             | 8-bit output port with the same function as port P0                                                                                                                                                                                                                                                                                                                         | FLD automatic display pins            |  |  |  |  |  |  |

| -<br> -<br> -<br> -<br> -<br> -<br> - | P2 <sub>0</sub> -P2 <sub>7</sub>                                                                                       | I/O port P2                | 8-bit CMOS I/O port     I/O direction register allows each pin to be individually programmed as either input or output.     At reset this port is set to input mode.     TTL compatible input level     CMOS 3-state output structure                                                                                                                                       |                                       |  |  |  |  |  |  |

|                                       | P3 <sub>0</sub> /SEG <sub>8</sub> -<br>P3 <sub>7</sub> /SEG <sub>15</sub>                                              | Output port P3             | 8-bit output port with the same function as port P0                                                                                                                                                                                                                                                                                                                         | FLD automatic display pins            |  |  |  |  |  |  |

|                                       | P4 <sub>0</sub> /INT <sub>0</sub>                                                                                      | Input port P4 <sub>0</sub> | • 1-bit CMOS input pin.                                                                                                                                                                                                                                                                                                                                                     | External interrupt input pin          |  |  |  |  |  |  |

|                                       | P4 <sub>1</sub> /INT <sub>1</sub> -<br>P4 <sub>4</sub> /INT <sub>4</sub>                                               | I/O port P4                | 7-bit CMOS I/O port with the same function as port P2     CMOS compatible input level     CMOS 3 states are transferred.                                                                                                                                                                                                                                                    | External interrupt input pins         |  |  |  |  |  |  |

|                                       | P4 <sub>5</sub>                                                                                                        |                            | CMOS 3-state output structure                                                                                                                                                                                                                                                                                                                                               |                                       |  |  |  |  |  |  |

| ļ                                     | P4 <sub>6</sub> /T1 <sub>OUT</sub> ,<br>P4 <sub>7</sub> /T3 <sub>OUT</sub>                                             |                            |                                                                                                                                                                                                                                                                                                                                                                             | Timer 1, Timer 3 output pin           |  |  |  |  |  |  |

DataShe

# mitsubishi microcomputers 3817 Group

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

#### PIN DESCRIPTION

| Pin                                                                                                                                                                                   | Name        | Function                                                                                                                                                                                              |                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

|                                                                                                                                                                                       |             |                                                                                                                                                                                                       | Alternate Function           |

| P5 <sub>0</sub> /S <sub>IN1</sub> ,<br>P5 <sub>1</sub> /S <sub>OUT1</sub> ,<br>P5 <sub>2</sub> /S <sub>CLK11</sub> ,<br>P5 <sub>3</sub> /S <sub>RDY1</sub> /<br>CS/S <sub>CLK12</sub> | I/O port P5 | 8-bit I/O port with the same function as port P2     N-channel open drain output structure     CMOS compatible input level     Keep the input voltage of this port between 0V and V <sub>CC</sub> .   | • Serial I/O1 I/O pins       |

| P5 <sub>4</sub> /S <sub>IN2</sub> ,<br>P5 <sub>5</sub> /S <sub>OUT2</sub> ,<br>P5 <sub>6</sub> /S <sub>CLK2</sub> ,<br>P5 <sub>7</sub> /S <sub>RDY2</sub>                             |             |                                                                                                                                                                                                       | Serial I/O2 I/O pins         |

| P6 <sub>0</sub> /PWM <sub>0</sub>                                                                                                                                                     | I/O port P6 | 6-bit CMOS I/O port with the same function as port P2     CMOS compatible input level                                                                                                                 | • 14-bit PWM output pin      |

| P6 <sub>1</sub> /PWM <sub>1</sub>                                                                                                                                                     |             | CMOS 3-state output structure                                                                                                                                                                         | 8-bit PWM output pin         |

| P6 <sub>2</sub> /CNTR <sub>0</sub> ,<br>P6 <sub>3</sub> /CNTR <sub>1</sub>                                                                                                            |             |                                                                                                                                                                                                       | Timer 2, Timer 4 input pins  |

| P6 <sub>4</sub> , P6 <sub>5</sub>                                                                                                                                                     |             |                                                                                                                                                                                                       |                              |

| P7 <sub>0</sub> /AN <sub>0</sub> -<br>P7 <sub>7</sub> /AN <sub>7</sub>                                                                                                                | I/O port P7 | 8-bit CMOS I/O port with the same function as port P2     CMOS compatible input level     CMOS 3-state output structure                                                                               | A-D conversion input pins    |

| P8 <sub>0</sub> /SEG <sub>0</sub> -<br>P8 <sub>7</sub> /SEG <sub>7</sub>                                                                                                              | I/O port P8 | 8-bit I/O port with the same function as port P2     P-channel open drain output structure     CMOS compatible input level     Please note that this port does not have internal pull-down resistors. | • FLD automatic display pins |

et4U.com

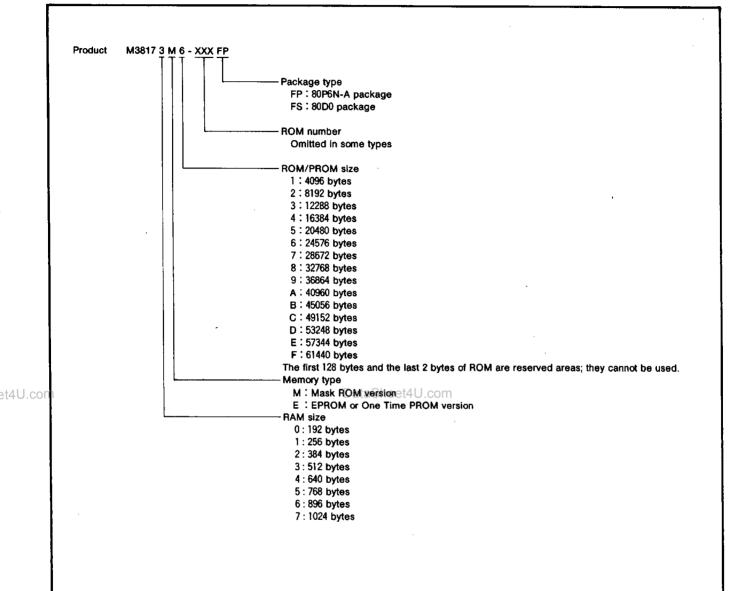

#### PART NUMBERING

DataShe

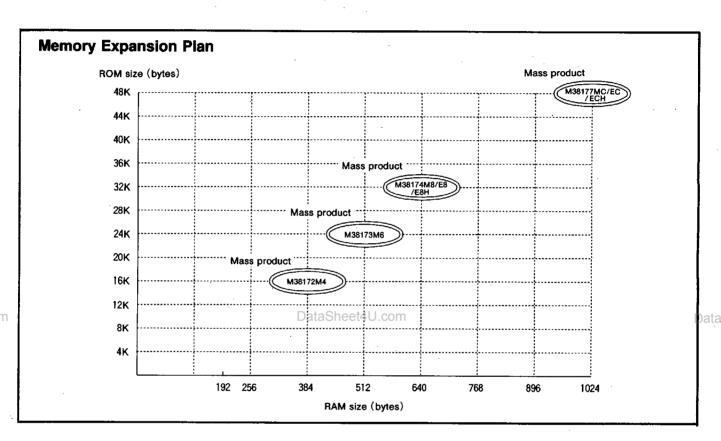

#### **GROUP EXPANSION**

Mitsubishi plans to expand the 3817 group as follows:

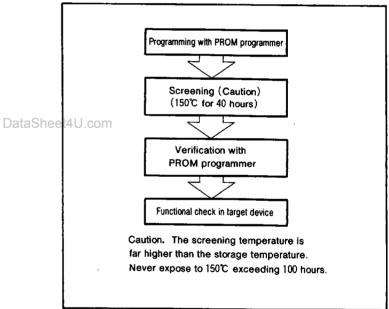

- (1) Support for mask ROM, One Time PROM, and EPROM versions

- (2) ROM/PROM size ············16K to 48K bytes RAM size ·········384 to 1024 bytes

(3) Packages

80P6N-A ··········· 0.8mm-pitch plastic molded QFP

80D0 ········ 0.8mm-pitch window type ceramic LCC

(EPROM version)

#### Currently supported products are listed below.

As of May 1996

| Product        | (P) ROM size (bytes)<br>ROM size for User in ( ) | RAM size (bytes) | Package | Remarks                       |

|----------------|--------------------------------------------------|------------------|---------|-------------------------------|

| M38172M4-XXXFP | 16384(16254)                                     | 384              |         | Mask ROM version              |

| M38173M6-XXXFP | 24576(24446)                                     | 512              | 7 .     | Mask ROM version              |

| M38174M8-XXXFP |                                                  |                  | 80P6N-A | Mask ROM version              |

| M38174E8-XXXFP |                                                  | 640              |         | One Time PROM version         |

| M38174E8FP     | 32768(32638)                                     |                  |         | One Time PROM version (blank) |

| M38174E8FS     |                                                  |                  | 80D0    | EPROM version                 |

| M38174E8HXXXFP |                                                  |                  | 80P6N-A | One Time PROM version         |

| M38174E8HFP    |                                                  |                  |         | One Time PROM version (blank) |

| M38174E8HFS    | ·                                                |                  | 80D0    | EPROM version                 |

| M38177MC-XXXFP |                                                  |                  |         | Mask ROM version              |

| M38177EC-XXXFP |                                                  |                  | 80P6N-A | One Time PROM version         |

| M38177ECFP     | 1                                                |                  |         | One Time PROM version (blank) |

| M38177ECFS     | 49152(49022)                                     | 1024             | 80D0    | EPROM version                 |

| M38177ECHXXXFP |                                                  |                  |         | One Time PROM version         |

| M38177ECHFP    |                                                  |                  | 80P6N-A | One Time PROM version (blank) |

| M38177ECHFS    |                                                  |                  | 80D0    | EPROM version                 |

# FUNCTIONAL DESCRIPTION Central Processing Unit (CPU)

The 3817 group uses the standard 740 family instruction set. Refer to the table of 740 family addressing modes and machine instructions or the SERIES 740 (Software) User's Manual for details on the instruction set.

Machine-resident 740 family instructions are as follows:

The FST and SLW instruction cannot be used.

The STP, WIT, MUL and DIV instruction can be used.

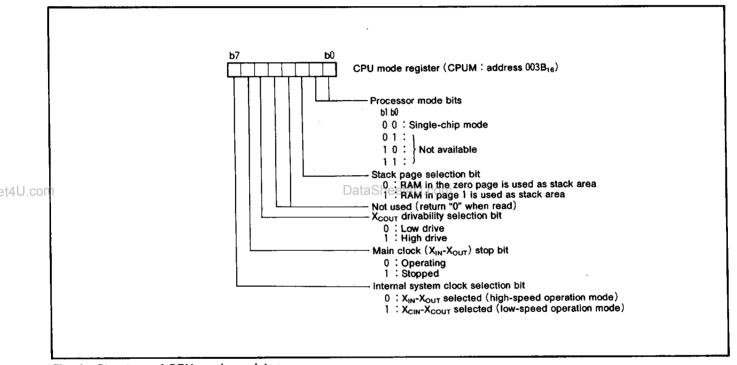

#### **CPU MODE REGISTER**

The CPU mode register is allocated at address 003B<sub>16</sub>. The CPU mode register contains the stack page selection bit and the internal system clock selection bit.

Fig. 1 Structure of CPU mode register

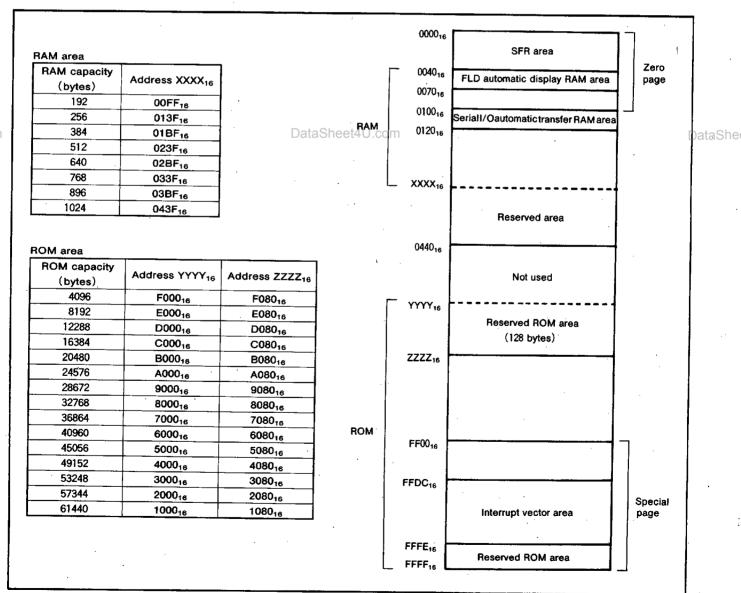

#### MEMORY

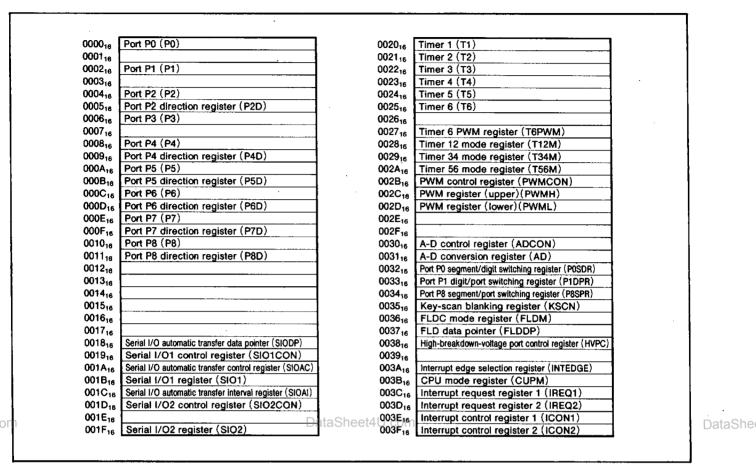

#### Special Function Register (SFR) Area

The Special Function Register area in the zero page contains control registers such as I/O ports and timers.

#### RAM

RAM is used for data storage and for stack area of sub-routine calls and interrupts.

#### ROM

The first 128 bytes and the last 2 bytes of ROM are reserved for device testing and the rest is user area for storing programs.

#### Interrupt Vector Area

The interrupt vector area contains reset and interrupt vectors.

#### Zero Page

The 256 bytes from addresses  $0000_{16}$  to  $00FF_{16}$  are called the zero page area. The internal RAM and the special function registers (SFR) are allocated to this area.

The zero page addressing mode can be used to specify memory and register addresses in the zero page area. Access to this area with only 2 bytes is possible in the zero page addressing mode.

#### **Special Page**

The 256 bytes from addresses FF00<sub>16</sub> to FFFF<sub>16</sub> are called the special page area. The special page addressing mode can be used to specify memory addresses in the special page area. Access to this area with only 2 bytes is possible in the special page addressing mode.

Fig. 2 Memory map diagram

Fig. 3 Memory map of special function register (SFR)

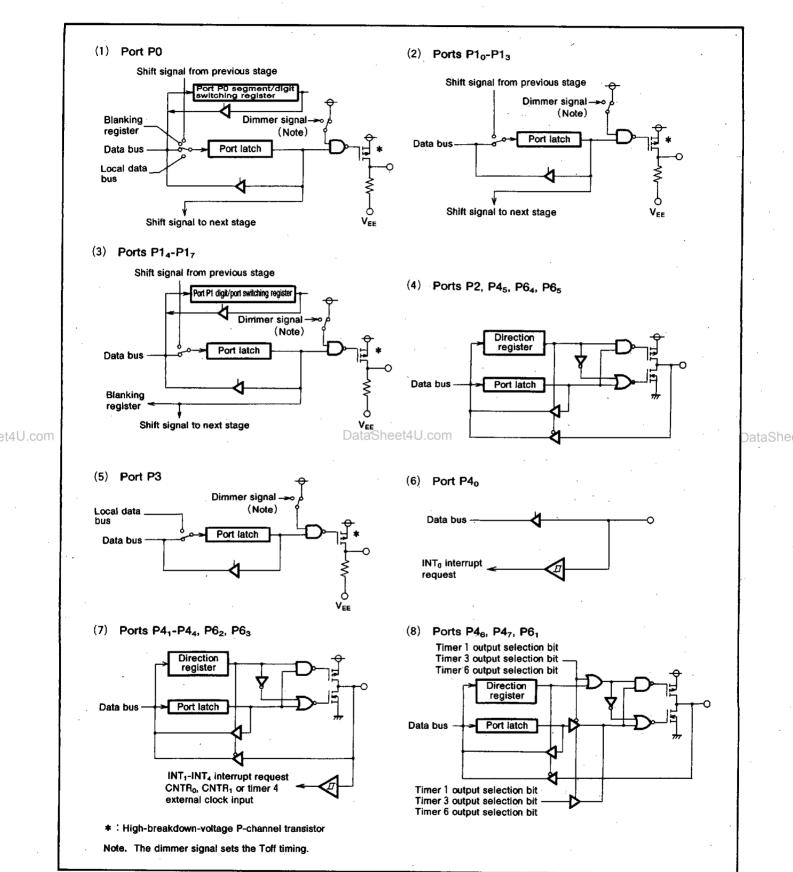

# I/O PORTS Direction Registers

The 3817 group has 45 programmable I/O pins arranged in six I/O ports (ports P2 and P4 to P8). The I/O ports have direction registers which determine the input/output direction of each individual pin. Each bit in a direction register corresponds to one pin, each pin can be set to be input port or output port.

When "0" is written to the bit corresponding to a pin, that pin becomes an input pin. When "1" is written to that bit, that pin becomes an output pin.

If data is read from a pin which is set to output, the value of the port output latch is read, not the value of the pin itself. Pins set to input are floating. If a pin set to input is written to, only the port output latch is written to and the pin remains floating.

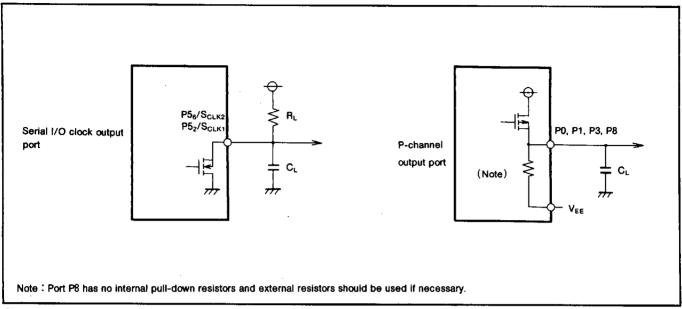

#### High-Breakdown-Voltage Output Ports

The 3817 group has four ports with high-breakdown-voltage pins (ports P0, P1, P3, P8). The high-breakdown-voltage ports have P-channel open drain output with a breakdown voltage of  $V_{\rm CC}$ —40V. Each pin in Ports P0, P1, and P3 has an internal pull-down resistor connected to  $V_{\rm EE}$ . Port P8 has no internal pull-down resistors, so that connect an external resistor to each port. At reset, the P-channel output transistor of each port latch is turned off, so it becomes  $V_{\rm EE}$  level ("L") by the pull-down resistor.

Writing "1" to bit 0 of the high-breakdown-voltage port control register (address 0038<sub>16</sub>) slows the transition of the output transistors to reduce transient noise. At reset, bit 0 of the high-breakdown-voltage port control register is set to "0" (strong drive).

#### MITSUBISHI MICROCOMPUTERS

### **3817 Group**

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

| Pin                                                                                                                    | Name    | Input/Output                        | I/O Format                                                                              | Non-Port Function              | Related SFRs                                                                                                                | Diagram<br>No. |

|------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------|

| P0 <sub>0</sub> /SEG <sub>16</sub> /<br>DIG <sub>0</sub> -<br>P0 <sub>7</sub> /SEG <sub>23</sub> /<br>DIG <sub>7</sub> | Port P0 | Output                              | High-breakdown-<br>voltage P-channel<br>open-drain output<br>with pull-down<br>resistor | FLD automatic display function | FLDC mode register<br>Port P0<br>segment/digit<br>switching register<br>High-breakdown-<br>voltage port control<br>register | (1)            |

| P1 <sub>0</sub> /DIG <sub>8</sub> -<br>P1 <sub>3</sub> /DIG <sub>11</sub>                                              |         |                                     | High-breakdown-voltage P-channel                                                        |                                | FLDC mode register<br>High-breakdown-<br>voltage port control<br>register                                                   | (2)            |

| P1 <sub>4</sub> /DIG <sub>12</sub> -<br>P1 <sub>7</sub> /DIG <sub>15</sub>                                             | Port P1 | Output                              | open-drain output<br>with pull-down<br>resistor                                         | FLD automatic display function | FLDC mode register<br>Port P1 digit/port<br>switching register<br>High-breakdown-<br>voltage port control<br>register       | (3)            |

| P2 <sub>0</sub> -P2 <sub>7</sub>                                                                                       | Port P2 | Input/output, individual bits       | TTL level input CMOS 3-state output                                                     |                                |                                                                                                                             | (4)            |

| P3 <sub>0</sub> /SEG <sub>8</sub> -<br>P3 <sub>7</sub> /SEG <sub>15</sub>                                              | Port P3 | Output                              | High-breakdown-voltage P-channel open-drain output with pull-down resistor              | FLD automatic display function | FLDC mode register<br>High-breakdown-<br>voltage port control<br>register                                                   | (5)            |

| P4 <sub>0</sub> /INT <sub>0</sub>                                                                                      |         | Input                               | CMOS compatible input level                                                             | External interrupt input       | Interrupt edge selection register                                                                                           | (6)            |

| P4 <sub>1</sub> /INT <sub>1</sub> -<br>P4 <sub>4</sub> /INT <sub>4</sub><br>P4 <sub>6</sub>                            | Port P4 | Port P4 Input/output,               | CMOS compatible input level CMOS 3-state output                                         | External interrupt input       | Interrupt edge selection register                                                                                           | (7)            |

| P4 <sub>6</sub> /T1 <sub>OUT</sub> ,<br>P4 <sub>7</sub> /T3 <sub>OUT</sub>                                             |         | individual bits                     |                                                                                         | Timer output                   | Timer 12 mode register Timer 34 mode register                                                                               | (8)            |

| P5 <sub>0</sub> /S <sub>IN1</sub> ,<br>P5 <sub>1</sub> /S <sub>OUT1</sub> ,                                            |         |                                     |                                                                                         |                                | Serial I/O1 control register                                                                                                | (9)            |

| P5 <sub>2</sub> /S <sub>CLK1</sub> ,<br>P5 <sub>3</sub> /S <sub>RDY1</sub> /                                           | Port P5 | Input/output,                       | CMOS compatible input level                                                             | Serial I/O1 function<br>I/O    | Serial I/O automatic transfer control                                                                                       | (10)           |

| CS/S <sub>CLK12</sub><br>P5 <sub>4</sub> /S <sub>IN2</sub> ,                                                           |         | individual bits N-channel           | N-channel open-drain output                                                             |                                | register                                                                                                                    | (9)            |

| P5 <sub>5</sub> /S <sub>OUT2</sub> ,<br>P5 <sub>6</sub> /S <sub>CLK2</sub> ,                                           |         |                                     | open-drain output                                                                       | Serial I/O2 function I/O       | Serial I/O2 control register                                                                                                | (10)           |

| P57/SRDY2                                                                                                              |         |                                     |                                                                                         |                                |                                                                                                                             | (11)           |

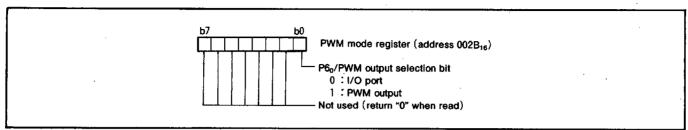

| P6 <sub>0</sub> /PWM <sub>0</sub>                                                                                      |         | Port P6 individual bits input level |                                                                                         | 14-bit PWM output              | PWM control register . PWML register PWMH register                                                                          | (12)           |

| P61/PWM1                                                                                                               | Port P6 |                                     | l '                                                                                     | 8-bit PWM output               | Timer 56 mode register Timer6 PWM register                                                                                  | (8)            |

| P6 <sub>2</sub> /CNTR <sub>0</sub> ,<br>P6 <sub>3</sub> /CNTR <sub>1</sub>                                             |         |                                     | CMOS 3-state output                                                                     | Timer 2, Timer 4 input         | Interrupt edge<br>selection register                                                                                        | (7)            |

| P6 <sub>4</sub> , P6 <sub>5</sub>                                                                                      |         |                                     |                                                                                         | -                              |                                                                                                                             | (4)            |

| P7 <sub>0</sub> /AN <sub>0</sub> -<br>P7 <sub>7</sub> /AN <sub>7</sub>                                                 | Port P7 | Input/output, individual bits       | CMOS compatible input level CMOS 3-state output                                         | A-D conversion input           | A-D control register                                                                                                        | (13)           |

et4U.com

# MITSUBISHI MICROCOMPUTERS 3817 Group

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

| Pin                                                                      | Name    | Input/Output                  | I/O Format                                                                                                | Non-Port Function              | Related SFRs                                                                                                            | Diagram<br>No. |

|--------------------------------------------------------------------------|---------|-------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------|

| P8 <sub>0</sub> /SEG <sub>0</sub> -<br>P8 <sub>7</sub> /SEG <sub>7</sub> | Port P8 | Input/output, individual bits | CMOS compatible input level High-breakdown-voltage P-channel open-drain output without pull-down resistor | FLD automatic display function | FLDC mode register<br>Port P8 segment/port<br>switching register<br>High-breakdown-<br>voltage port control<br>registor |                |

Note 1. For details of how to use double-function ports as function I/O ports, refer to the applicable sections.

et4U.com

DataSheet4U.com

DataSne

Make sure that the input level at each pin is either 0V or V<sub>CC</sub> during execution of the STP instruction.

When an input level is at an intermediate potential, a current will flow from V<sub>CC</sub> to V<sub>SS</sub> through the input-stage gate.

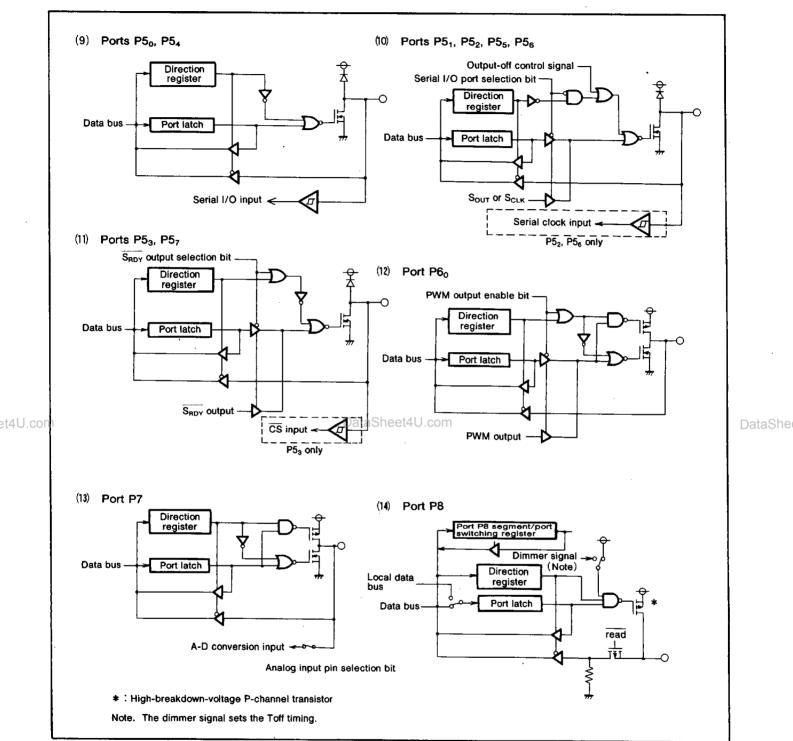

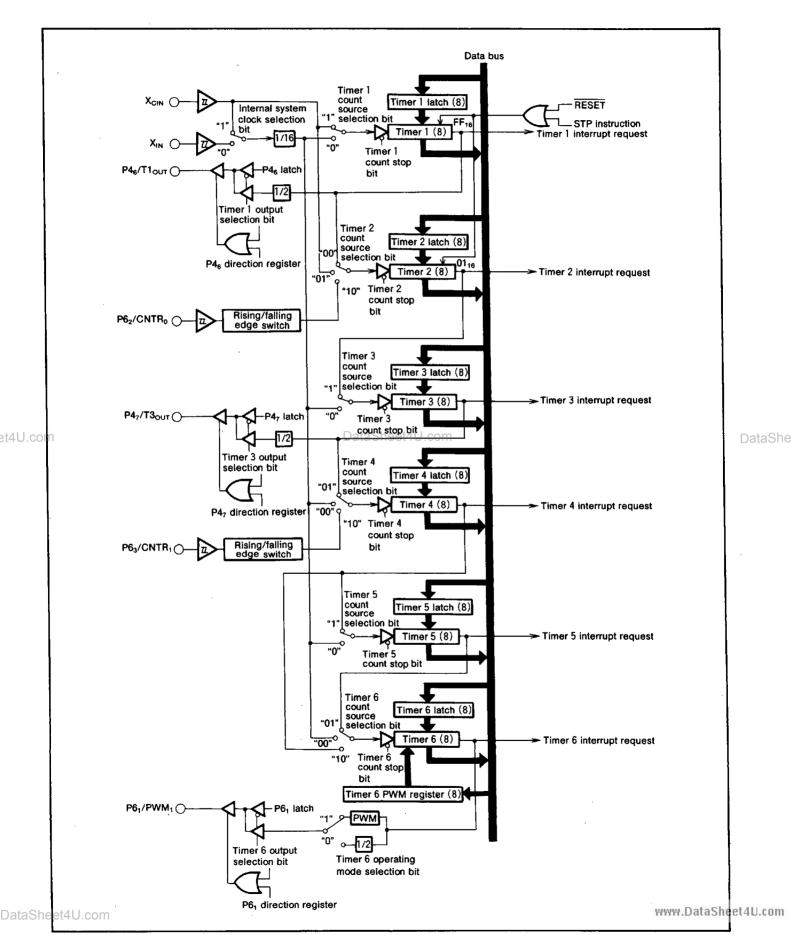

Fig. 4 Port block diagram (1)

Fig. 5 Port block diagram (2)

#### **INTERRUPTS**

Interrupts occur by eighteen sources: five external, twelve internal, and one software.

#### **Interrupt Control**

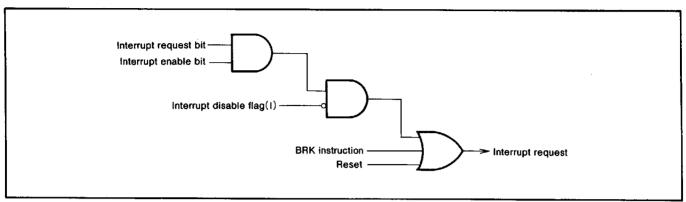

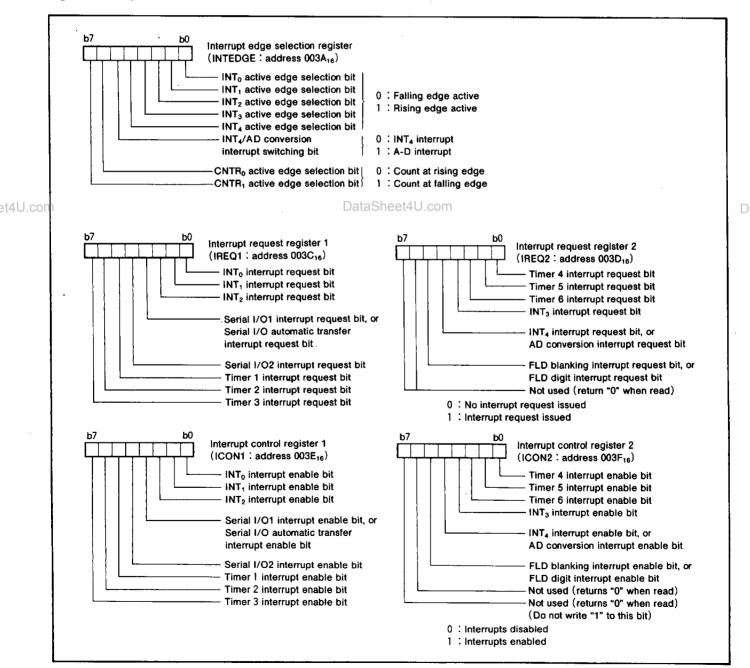

Each interrupt is controlled by its interrupt request bit, its interrupt enable bit, and the interrupt disable flag except for the software interrupt set by the BRK instruction. An interrupt occurs if the corresponding interrupt request and enable bits are "1" and the interrupt disable flag is "0". Interrupt enable bits can be set or cleared by software. Interrupt request bits can be cleared by software, but cannot be set by software.

The BRK instruction cannot be disabled with any flag or bit. The I (interrupt disable) flag disables all interrupts except the BRK instruction interrupt.

When several interrupts occur at the same time, the interrupts are received according to priority.

#### **Interrupt Operation**

When an interrupt is received, the contents of the program counter and processor status register are automatically stored into the stack. The interrupt disable flag is set to inhibit other interrupts from interfering. The corresponding interrupt request bit is cleared and the interrupt jump destination address is read from the vector table into the program counter.

#### **Notes on Use**

When the active edge of an external interrupt (INT<sub>0</sub>-INT<sub>4</sub>) is changed or when switching interrupt sources in the same vector address, the corresponding interrupt request bit may also be set. Therefore, please take following sequence;

- (1) Disable the external interrupt which is selected.

- (2) Change the active edge selection.

- (3) Clear the interrupt request bit which is selected to "0".

- (4) Enable the external interrupt which is selected.

Table 1. Interrupt vector addresses and priority

| Interrupt Source                      | Delanta  | Vector Addre                | sses (Note 1)      | Interrupt Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                       |

|---------------------------------------|----------|-----------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| interrupt source                      | Priority | High                        | Low                | Generating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Remarks                                               |

| Reset (Note 2)                        | 1        | FFFD <sub>16</sub>          | FFFC <sub>16</sub> | At reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Non-maskable                                          |

| INT <sub>0</sub>                      | 2        | FFFB <sub>16</sub>          | FFFA <sub>16</sub> | At detection of either rising or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | External interrupt                                    |

|                                       |          |                             | DataShee           | falling edge of INT <sub>0</sub> input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | (active edge selectable)                              |

| INT <sub>1</sub>                      | ` 3      | FF <b>F</b> 9 <sub>16</sub> | FFF8 <sub>16</sub> | At detection of either rising or falling edge of INT <sub>1</sub> input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | External interrupt (active edge selectable)           |

|                                       |          |                             | <del> </del>       | At detection of either rising or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | External interrupt                                    |

| INT <sub>2</sub>                      | 4        | FFF7 <sub>16</sub>          | FFF6 <sub>16</sub> | falling edge of INT <sub>2</sub> input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | (active edge selectable)                              |

|                                       |          |                             |                    | idaming dags of http://iput                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Valid when serial I/O ordinary                        |

| Serial I/O1                           | 5        |                             |                    | At completion of data transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | mode is selected                                      |

| Serial I/O automa-                    | 5        | FFF5 <sub>16</sub>          | FFF4 <sub>16</sub> | At completion of the last data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Valid when serial I/O automa-                         |

| tic transfer                          |          |                             |                    | transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | tic transfer mode is selected                         |

| Serial I/O2                           | 6        | FFF3 <sub>16</sub>          | FFF2 <sub>16</sub> | At completion of data transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                       |

| Timer 1                               | 7        | FFF1 <sub>16</sub>          | FFF0 <sub>16</sub> | At timer 1 underflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ·                                                     |

| Timer 2                               | 8        | FFEF <sub>16</sub>          | FFEE <sub>16</sub> | At timer 2 underflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | STP release timer underflow                           |

| Timer 3                               | 9        | FFED <sub>16</sub>          | FFEC <sub>16</sub> | At timer 3 underflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                       |