# UNISONIC TECHNOLOGIES CO., LTD

LC1126

**Preliminary**

# LINEAR INTEGRATED CIRCUIT

# **ULTRA LOW OUTPUT VOLTAGE LINEAR N-FET** CONTROLLER

#### DESCRIPTION

The UTC LC1126 is an ultra low output voltage linear N-FET controller designed to provide well supply voltage for front-side-bus termination on motherboards and NB applications. The UTC LC1126 integrates many functions. A Power-On-Reset (POR) circuit monitors supply voltages to prevent wrong operations. A POK indicates the output status with time delay which is set internally. It can control other converter for power sequence. It can available for SC-59-6 package.

The UTC LC1126 can be enabled by other power system. A 0.5V reference voltage with 2% accuracy providing tight regulation of the output voltage, enable control, open drain power good signal, under-voltage protection and soft start.

- \* MLCC and POSCAP Stable

- \* 0.5V±2% Reference Voltage

- \* Internal soft-start

- \* Enable control

- \* Fast transient response

- \* Under-Voltage short circuit protection

- \* Power OK output with a delay time

- \* Adjustable output voltage down to 0.5V

- \* Drive N-Channel MOSFETs

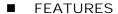

#### ORDERING INFORMATION

| Ordering Number |               | Dooleage             | Packing   |  |

|-----------------|---------------|----------------------|-----------|--|

| Lead Free       | Halogen Free  | Halogen Free Package |           |  |

| LC1126L-AG6-R   | LC1126G-AG6-R | SOT-26               | Tape Reel |  |

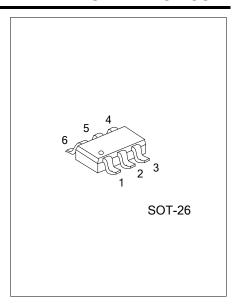

# MARKING INFORMATION

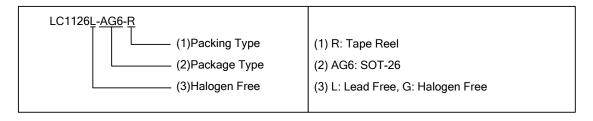

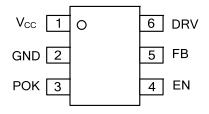

# PIN CONFIGURATION

# PIN DESCRIPTION

| PIN NO. | PIN NAME | DESCRIPTION                      |

|---------|----------|----------------------------------|

| 1       | Vcc      | Input Voltage                    |

| 2       | GND      | Ground                           |

| 3       | POK      | Power ok Output Pin              |

| 4       | EN       | H: Normal Operation, L: Shutdown |

| 5       | FB       | Feedback Pin                     |

| 6       | DRV      | Gate Drive to N-FET              |

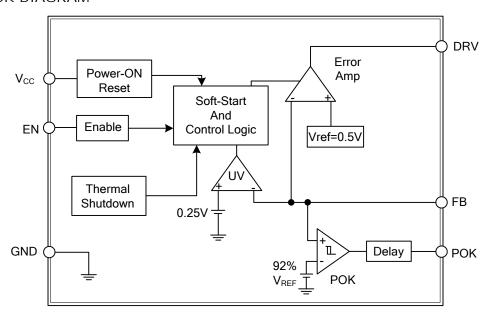

# ■ BLOCK DIAGRAM

# ABSOLUTE MAXIMUM RATING (T<sub>A</sub>=25°C, unless otherwise specified)

| PARAMETER             | SYMBOL           | RATINGS                   | UNIT |

|-----------------------|------------------|---------------------------|------|

| Supply Voltage        | VCC              | -0.3~7                    | V    |

| DRV to GND            |                  | -0.3~V <sub>CC</sub> +0.3 | V    |

| Power Dissipation     | $P_{D}$          | 0.4                       | W    |

| Junction Temperature  | TJ               | -40~+125                  | °C   |

| Operating Temperature | T <sub>OPR</sub> | -40~+85                   | °C   |

| Storage Temperature   | T <sub>STG</sub> | -65~+150                  | °C   |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

# **ELECTRICAL CHARACTERISTICS**

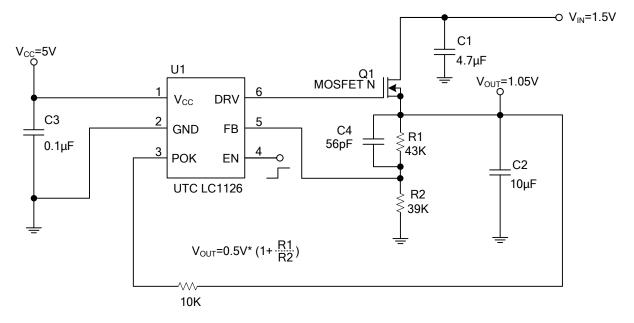

( $V_{IN}$ =1.5V,  $V_{SHDN}$ = $V_{IN}$ ,  $T_A$ =25 $^{\circ}$ C,  $C_{IN}$ = $C_{OUT}$ =1 $\mu$ F, unless otherwise noted.)

| PARAMETER                              | SYMBOL                 | TEST CONDITIONS                                      | MIN  | TYP  | MAX  | UNIT |

|----------------------------------------|------------------------|------------------------------------------------------|------|------|------|------|

| Supply Voltage Range                   | V <sub>CC</sub>        |                                                      | 4.5  |      | 5.5  | V    |

| Input Voltage UVLO Threshold           | $V_{UVLO}$             | V <sub>CC</sub> Rising                               |      | 3.75 |      | V    |

| Input Voltage UVLO Hysteresis          | $V_{HYST}$             | V <sub>CC</sub> Falling                              |      | 0.25 |      | V    |

| Supply Current                         | I <sub>CC</sub>        | EN=V <sub>CC</sub>                                   |      | 0.4  | 0.8  | mΑ   |

| Shutdown Current                       | $I_{SD}$               | EN=0V                                                | -1   |      | 1    | μΑ   |

| Feedback Voltage                       | $V_{FB}$               |                                                      | 0.49 | 0.5  | 0.51 | V    |

| Feedback Pin Input Current             | $I_{FB}$               | VFB=0.5V                                             | -100 |      | 100  | nA   |

| Soft Start Time                        | TSS                    |                                                      |      | 1    |      | ms   |

| EN Pin Logic High Threshold Voltage    | $V_{ENH}$              | Enable                                               | 1.3  |      |      | V    |

| EN PIN Logic High Threshold Voltage    | $V_{ENL}$              | Disable                                              |      |      | 0.5  | V    |

| EN Pin Input Current                   | I <sub>EN</sub>        | I <sub>OUT</sub> =0mA, V <sub>IN</sub> =5V           | -1   |      | +1   | μΑ   |

| Output Voltage UVLO Threshold          | $V_{TH(UV)}$           | V <sub>FB</sub> Falling                              | 0.2  | 0.25 | 0.3  | V    |

| Ton Duty                               | T <sub>ON</sub>        | V <sub>FB</sub> <0.25V                               |      | 30   |      | %    |

| DDV Outrout Comment                    | I <sub>DRV(SRC)</sub>  | Sourcing, V <sub>FB</sub> =0.48V                     |      | 20   |      | mΑ   |

| DRV Output Current                     | I <sub>DRV(SINK)</sub> | Sinking, V <sub>FB</sub> =0.52V                      |      | 20   |      | mΑ   |

| DRV Pin Output Voltage                 | $V_{DRV}$              | V <sub>FB</sub> =0.48V, V <sub>CC</sub> =5V, No Load | 4.9  |      | 5.0  | V    |

| POK Threshold Voltage for Power OK     | $V_{POK}$              | V <sub>FB</sub> Rising                               | 90%  | 93%  | 96%  | VFB  |

| POK Threshold Voltage for Power Not OK | $V_{PNOK}$             | V <sub>FB</sub> Falling                              | 82%  | 85%  | 88%  | VFB  |

| POK Low Voltage                        |                        | POK Sinks 1mA                                        |      | 50   | 100  | mV   |

| POK Delay Time                         | T <sub>DELAY</sub>     |                                                      | 0.8  | 2    | 10   | ms   |

| Thermal Shutdown Temperature           | T <sub>SD</sub>        |                                                      |      | 150  |      | °C   |

| Thermal Shutdown Hysteresis            |                        |                                                      |      | 50   |      | °C   |

#### FUNCTION DESCRIPTIONS

#### Power-On-Reset

A Power-On-Reset (POR) circuit monitors the VCC pin voltage (VCC) for power-on-reset function to prevent wrong operation. The built-in POR circuit keeps the output shutting off until internal circuit is operating properly.

#### **Internal Soft-Start**

An internal soft-start provides an internal soft-start circuitry to control rise rate of the output voltage and limit the current surge during start-up. The typical soft-start interval is about 1ms.

#### **Output Voltage Regulation**

An error amplifier working with a temperature compensated 0.5V reference and an output NMOS regulates output to the preset voltage. The error amplifier designed with high bandwidth and DC gain provides very fast transient response and less load regulation.

## **Under-Voltage Protection (UVP)**

UTC **LC1126** monitors the voltage on FB pin after soft-start process is finished. Therefore the UVP is disabling during soft-start. When the voltage on FB pin falls below the under-voltage threshold, the UVP circuit shuts off the output immediately. After a while (~70% Duty), UTC **LC1126** starts a new soft-start to regulate output.

#### Thermal Shutdown

A thermal shutdown circuit limits the junction temperature of UTC **LC1126**. When the junction temperature exceeds +150°C, a thermal sensor turns off the output NMOS, allowing the device to cool down. The regulator regulates the output again through initiation of new soft-start cycle after the junction temperature cools by 50°C, resulting in a pulsed output during continuous thermal overload conditions.

## TYPICAL APPLICATION CIRCUIT

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice.