# Enhanced Poly-Phase High-Performance Wide-Span Energy Metering IC

#### PRELIMINARY DATASHEET

# **FEATURES**

# **Metering Features**

- Metering features fully in compliance with the requirements of IEC62052-11, IEC62053-22 and IEC62053-23, ANSI C12.1 and ANSI C12.20; applicable in polyphase class 0.2S, 0.5S or class 1 watt-hour meter or class 2 var-hour meter.

- Accuracy of  $\pm 0.1\%$  for active energy and  $\pm 0.2\%$  for reactive energy over a dynamic range of 6000:1.

- Temperature coefficient is 6 ppm/  $\,^{\circ}$ C (typ.) for on-chip reference voltage. Automatically temperature compensated.

- Single-point calibration on each phase over the whole dynamic range for active energy; no calibration needed for reactive/ apparent energy.

- ±1 °C (typ.) temperature sensor accuracy.

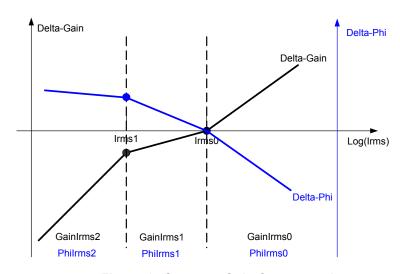

- Flexible piece-wise non-linearity compensation: three current (RMS value)-based segments with two programmable thresholds for each phase. Independent gain and phase angle compensation for each segment.

- Electrical parameters measurement: less than  $\pm 0.5\%$  fiducial error for Vrms, Irms, mean active/ reactive/ apparent power, frequency, power factor and phase angle.

- Active (forward/reverse), reactive (forward/reverse), apparent energy with independent energy registers.

- · Programmable startup and no-load power thresholds.

- 6 dedicated ADCs for phase A/B/C current and voltage sampling circuits. Current sampled over Current Transformer (CT) or Rogowski coil (di/dt coil); voltage sampled over resistor divider network.

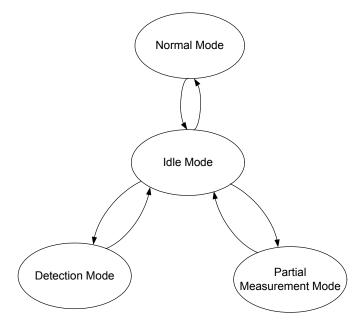

- Programmable power modes: Normal, Idle, Detection and Partial Measurement mode.

- Fundamental (0.2%) and harmonic (1%) active energy with dedicated energy / power registers and independent energy outputs.

- Current and voltage instantaneous signal monitoring.

- Enhanced event detection: sag, over voltage, phase loss, over current, reverse V/I phase sequence, calculated neutral line current I<sub>NC</sub> over-current and frequency upper and lower threshold.

#### Other Features

- 3.3V single power supply. Operating voltage range: 2.8V~3.6V. Metering accuracy guaranteed within 3.0V~3.6V.

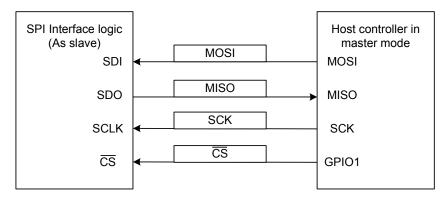

- · Four-wire SPI interface.

- Programmable voltage sag detection and zero-crossing output.

- Crystal oscillator frequency: 16.384MHz. On-chip two capacitors and no need of external capacitors.

- Lower power consumption. I=13mA (typ.) in Normal mode.

- · TQFP48 package.

- Operating temperature: -40  $^{\circ}$ C ~ +85  $^{\circ}$ C .

# **APPLICATION**

- Poly-phase energy meters of class 0.2S, 0.5S and class 1 which are used in three-phase four-wire (3P4W, Y0) or three-phase three-wire (3P3W, Y or Δ) systems.

- Power monitoring instruments which need to measure voltage, current, mean power, etc.

# GENERAL DESCRIPTION

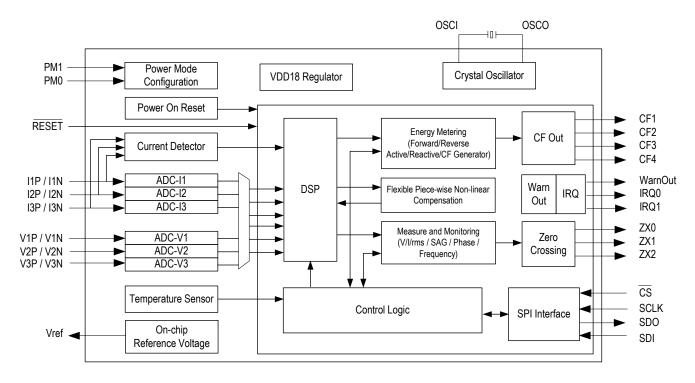

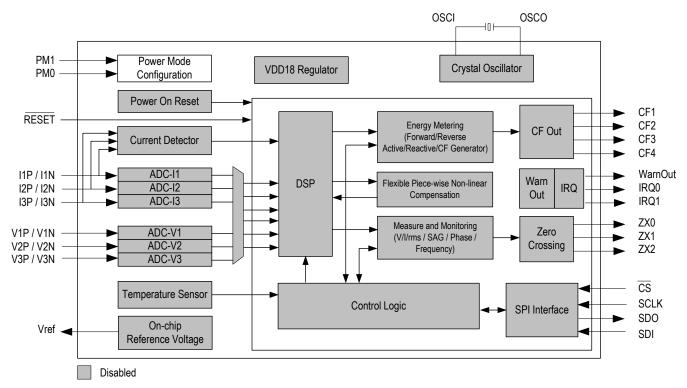

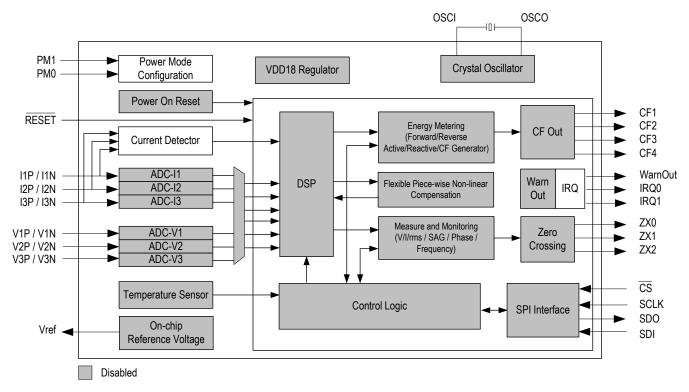

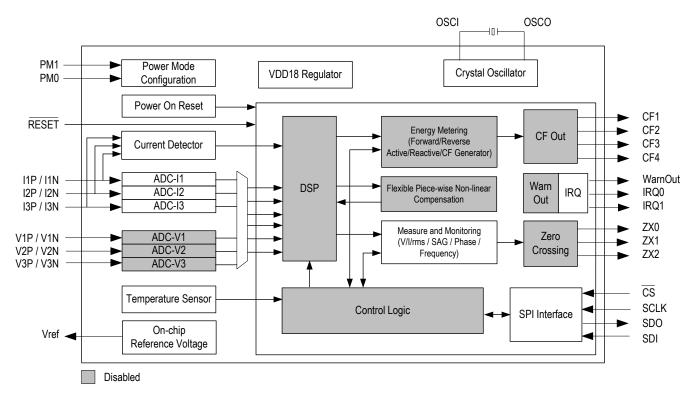

The M90E32AS is a poly-phase high performance wide-dynamic range metering IC. The M90E32AS incorporates 6 independent 2nd order sigma-delta ADCs, which could be employed in three voltage channels (phase A, B and C) and three current channels (phase A, B, C) in a typical three-phase four-wire system.

The M90E32AS has an embedded DSP which executes calculation of active energy, reactive energy, apparent energy, fundamental and harmonic active energy over ADC signal and on-chip reference voltage. The DSP also calculates measurement parameters such as voltage and current RMS value as well as mean active/reactive/apparent power.

A four-wire SPI interface is provided between the M90E32AS and the external microcontroller.

The M90E32AS is suitable for poly-phase multi-function meters which could measure active/reactive/apparent energy and fundamental/harmonic energy either through four independent energy pulse outputs CF1/CF2/CF3/CF4 or through the corresponding registers.

The ADC and auto-temperature compensation technology for reference voltage ensure the M90E32AS's long-term stability over variations in grid and ambient environment conditions.

# **BLOCK DIAGRAM**

Figure-1 M90E32AS Block Diagram

# **Table of Contents**

| FE | EAT | URES                                                 | . 1 |

|----|-----|------------------------------------------------------|-----|

| ΑI | PPL | ICATION                                              | . 2 |

|    |     | RAL DESCRIPTION                                      |     |

|    |     | K DIAGRAM                                            |     |

|    |     |                                                      |     |

|    |     | I ASSIGNMENT                                         |     |

| 2  | PIN | I DESCRIPTION                                        | 8   |

| 3  | FUI | NCTION DESCRIPTION                                   | 10  |

|    | 3.1 | POWER SUPPLY                                         | .10 |

|    | 3.2 | CLOCK                                                | .10 |

|    | 3.3 | RESET                                                | .10 |

|    |     | 3.3.1 RESET Pin                                      | 10  |

|    |     | 3.3.2 Power On Reset (POR)                           | 10  |

|    |     | 3.3.3 Software Reset                                 | 10  |

|    | 3.4 | ANALOG/DIGITAL CHANNEL MAPPING                       | .11 |

|    | 3.5 | METERING FUNCTION                                    | .12 |

|    |     | 3.5.1 Theory of Energy Registers                     | 12  |

|    |     | 3.5.2 Energy Registers                               |     |

|    |     | 3.5.3 Energy Pulse Output                            |     |

|    |     | 3.5.4 Startup and No-load Power                      |     |

|    | 3.6 | MEASUREMENT FUNCTION                                 |     |

|    |     | 3.6.1 Active/ Reactive/ Apparent Power               |     |

|    |     | 3.6.2 Fundamental / Harmonic Active Power            |     |

|    |     | 3.6.3 Mean Power Factor (PF)                         |     |

|    |     | 3.6.4 Voltage / Current RMS                          |     |

|    |     | 3.6.5 Phase Angle                                    |     |

|    |     | 3.6.6 Frequency                                      |     |

|    |     | 3.6.8 Peak Value                                     |     |

|    | 27  | POWER QUALITY MONITORING                             |     |

|    | 3.1 | 3.7.1 Instantaneous Signal Monitoring                |     |

|    |     | 3.7.2 Instantaneous Signal Related Status And Events |     |

|    |     | 3.7.3 Frequency Monitoring Related Status And Events |     |

|    |     | 3.7.4 Zero-Crossing Detection                        |     |

|    |     | 3.7.5 Neutral Line Overcurrent Detection             |     |

|    |     | 3.7.6 Phase Sequence Error Detection                 |     |

|    | 3.8 | POWER MODE                                           |     |

|    |     | 3.8.1 Normal Mode (N Mode)                           |     |

|    |     | 3.8.2 Idle Mode (I Mode)                             |     |

|    |     | 3.8.3 Detection Mode (D Mode)                        | 24  |

|    |     | 3.8.4 Partial Measurement mode (M Mode)              |     |

|    |     | 3.8.5 Transition of Power Modes                      | 26  |

|    | 3.9 | EXTERNAL COMPONENT COMPENSATION                      |     |

|    |     | 3.9.1 Gain Based Compensation                        |     |

|    |     | 3.9.2 Delay/Phase Based Compensation                 | 29  |

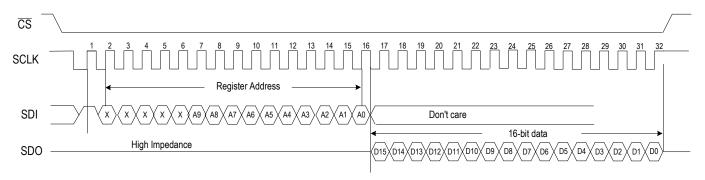

| 4  | SPI                | INTERFACE                                                            | 30  |  |  |  |  |  |  |

|----|--------------------|----------------------------------------------------------------------|-----|--|--|--|--|--|--|

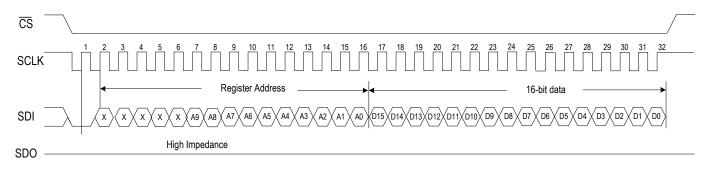

|    | 4.1                | INTERFACE DESCRIPTION                                                | .30 |  |  |  |  |  |  |

|    | 4.2                | SPI INTERFACE                                                        | .30 |  |  |  |  |  |  |

|    |                    | 4.2.1 SPI Slave Interface Format                                     | 30  |  |  |  |  |  |  |

|    |                    | 4.2.2 Reliability Enhancement Feature                                | 31  |  |  |  |  |  |  |

| 5  | RE                 | GISTER                                                               | 32  |  |  |  |  |  |  |

|    |                    | REGISTER LIST                                                        |     |  |  |  |  |  |  |

|    |                    | SPECIAL REGISTERS                                                    |     |  |  |  |  |  |  |

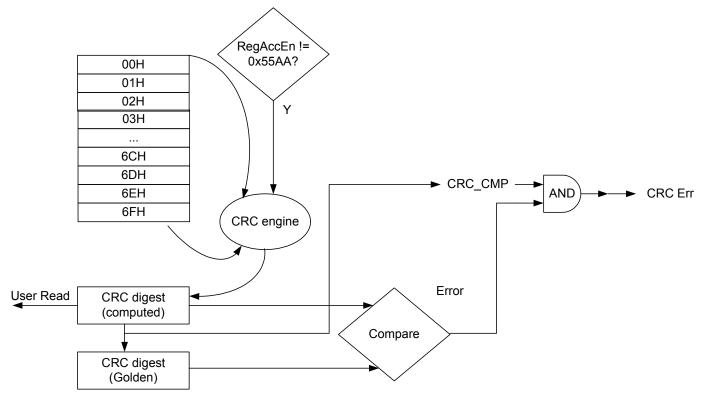

|    |                    | 5.2.1 Configuration Registers CRC Generation                         |     |  |  |  |  |  |  |

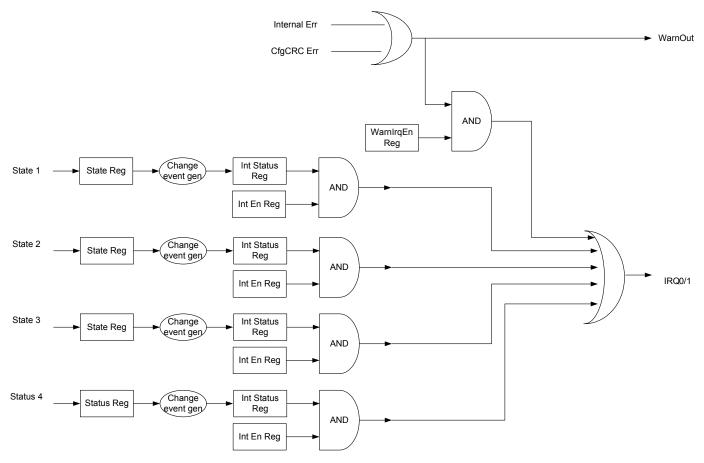

|    |                    | 5.2.2 IRQ and WarnOut Signal Generation                              |     |  |  |  |  |  |  |

|    |                    | 5.2.3 Special Configuration Registers                                | 45  |  |  |  |  |  |  |

|    | 5.3                | LOW-POWER MODES REGISTERS                                            | .48 |  |  |  |  |  |  |

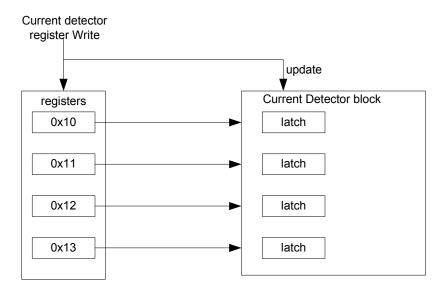

|    |                    | 5.3.1 Detection Mode Registers                                       | 48  |  |  |  |  |  |  |

|    |                    | 5.3.2 Partial Measurement mode Registers                             | 50  |  |  |  |  |  |  |

|    | 5.4                | CONFIGURATION AND CALIBRATION REGISTERS                              |     |  |  |  |  |  |  |

|    |                    | 5.4.1 Configuration Registers                                        |     |  |  |  |  |  |  |

|    |                    | 5.4.2 Energy Calibration Registers                                   |     |  |  |  |  |  |  |

|    |                    | 5.4.3 Fundamental/Harmonic Energy Calibration registers              |     |  |  |  |  |  |  |

|    |                    | 5.4.4 Measurement Calibration                                        |     |  |  |  |  |  |  |

|    |                    | 5.4.5 EMM Status                                                     |     |  |  |  |  |  |  |

|    | 5.5                | ENERGY REGISTER                                                      |     |  |  |  |  |  |  |

|    |                    | 5.5.1 Regular Energy Registers                                       |     |  |  |  |  |  |  |

|    |                    | 5.5.2 Fundamental / Harmonic Energy Register                         |     |  |  |  |  |  |  |

|    | 5.6                | MEASUREMENT REGISTERS                                                |     |  |  |  |  |  |  |

|    |                    | 5.6.1 Power and Power Factor Registers                               |     |  |  |  |  |  |  |

|    |                    | 5.6.2 Fundamental/ Harmonic Power and Voltage/ Current RMS Registers |     |  |  |  |  |  |  |

|    |                    | 5.6.3 Peak, Frequency, Angle and Temperature Registers               |     |  |  |  |  |  |  |

| 6  |                    | ECTRICAL SPECIFICATION                                               |     |  |  |  |  |  |  |

|    |                    | ELECTRICAL SPECIFICATION                                             |     |  |  |  |  |  |  |

|    | 6.2                | METERING/ MEASUREMENT ACCURACY                                       |     |  |  |  |  |  |  |

|    |                    | 6.2.1 Metering Accuracy                                              |     |  |  |  |  |  |  |

|    |                    | 6.2.2 Measurement Accuracy                                           |     |  |  |  |  |  |  |

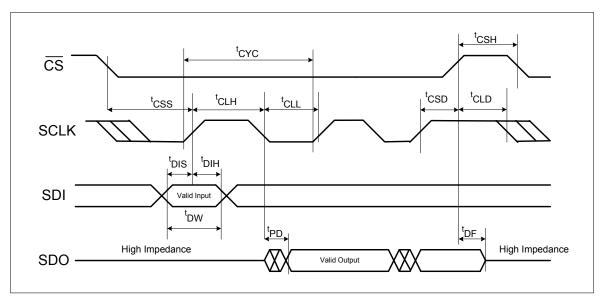

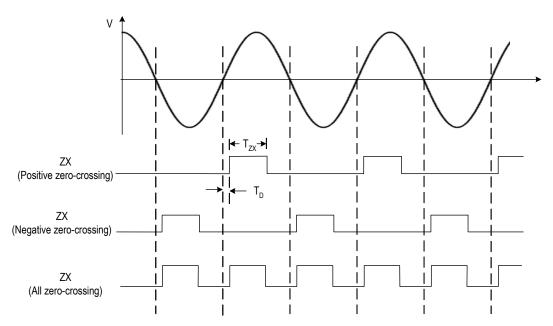

|    | 6.3                | INTERFACE TIMING                                                     |     |  |  |  |  |  |  |

|    |                    | 6.3.1 SPI Interface Timing (Slave Mode)                              |     |  |  |  |  |  |  |

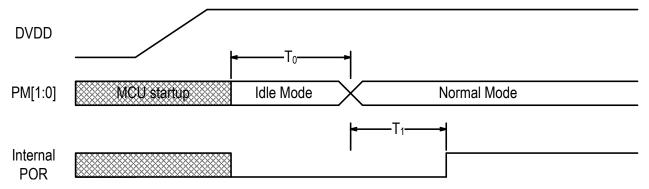

|    |                    | POWER ON RESET TIMING                                                |     |  |  |  |  |  |  |

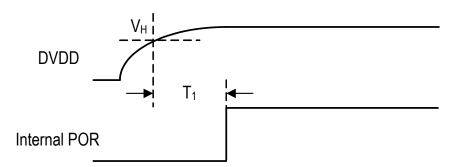

|    |                    | ZERO-CROSSING TIMING                                                 |     |  |  |  |  |  |  |

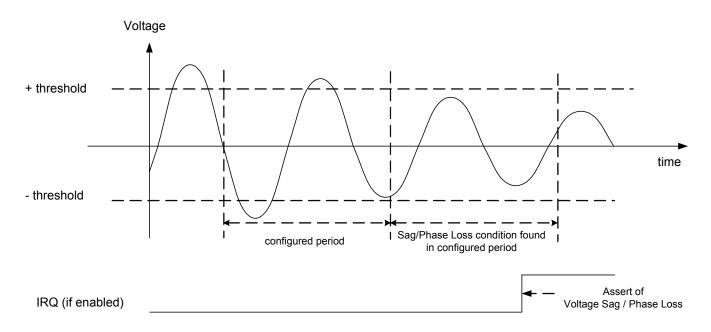

|    |                    | VOLTAGE SAG AND PHASE LOSS TIMING                                    |     |  |  |  |  |  |  |

|    | 6.7                | ABSOLUTE MAXIMUM RATING                                              | .80 |  |  |  |  |  |  |

| OI | RDE                | RING INFORMATION                                                     | 81  |  |  |  |  |  |  |

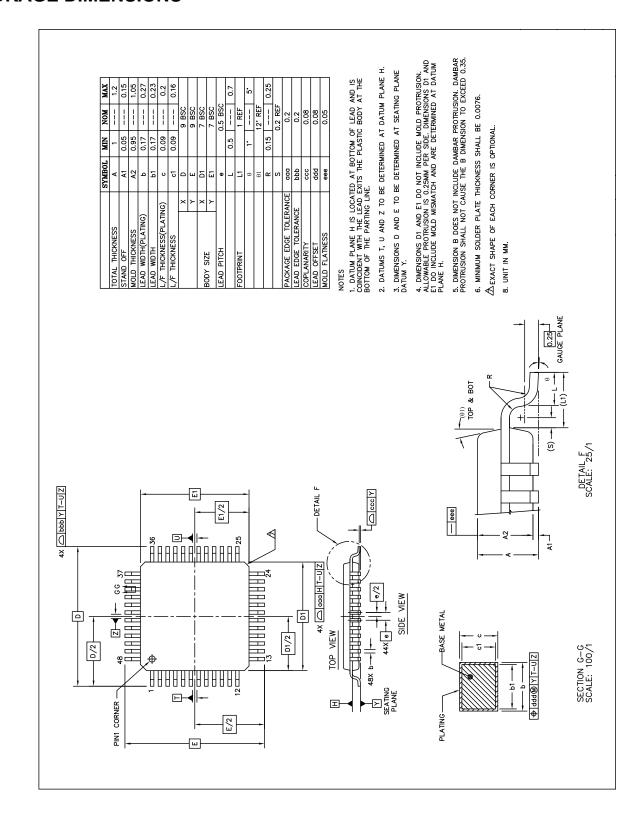

| P  | ۱CK                | AGE DIMENSIONS                                                       | 82  |  |  |  |  |  |  |

| R  | PACKAGE DIMENSIONS |                                                                      |     |  |  |  |  |  |  |

# **List of Tables**

| Table-1  | Pin Description                                                 | 8  |

|----------|-----------------------------------------------------------------|----|

| Table-2  | Power Mode Mapping                                              | 21 |

| Table-3  | Digital I/O and Power Pin States in Idle Mode                   | 22 |

| Table-4  | Compensation Related Registers                                  |    |

| Table-5  | Register List                                                   |    |

| Table-6  | Configuration Registers                                         |    |

| Table-7  | Calibration Registers                                           |    |

| Table-8  | Fundamental/Harmonic Energy Calibration Registers               |    |

| Table-9  | Measurement Calibration Registers                               |    |

| Table-10 | EMM Status Registers                                            | 59 |

| Table-11 | Regular Energy Registers                                        | 67 |

| Table-12 | Fundamental / Harmonic Energy Register                          | 68 |

| Table-13 | Power and Power Factor Register                                 |    |

| Table-14 | Fundamental/ Harmonic Power and Voltage/ Current RMS Registers  | 70 |

| Table-15 | Peak, Frequency, Angle and Temperature Registers                |    |

| Table-16 | Metering Accuracy for Different Energy within the Dynamic Range | 74 |

| Table-17 | Measurement Parameter Range and Format                          | 75 |

| Table-18 | SPI Timing Specification                                        | 76 |

| Table-19 | Power On Reset Specification                                    | 77 |

| Table-20 | Zero-Crossing Specification                                     |    |

|          |                                                                 |    |

# List of Figures

| Figure-1  | M90E32AS Block Diagram                                                 | 2    |

|-----------|------------------------------------------------------------------------|------|

| Figure-2  | Pin Assignment (Top View)                                              | 7    |

| Figure-3  | Channel to Phase Mapping                                               | . 11 |

| Figure-4  | Energy Accumulation Diagram                                            | . 13 |

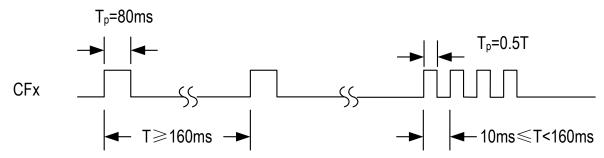

| Figure-5  | CFx Pulse Output Regulation                                            | . 14 |

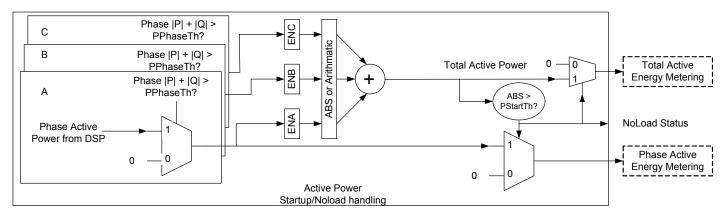

| Figure-6  | Active Power Startup/Noload Processing                                 | . 14 |

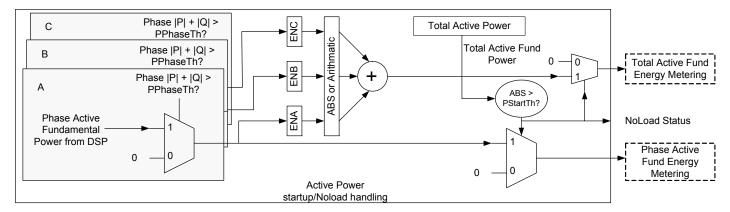

| Figure-7  | Fundamental Active Power Startup/Noload Processing                     | . 15 |

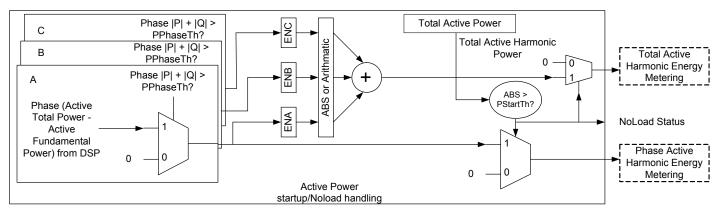

| Figure-8  | Harmonic Active Power Startup/Noload Processing                        | . 15 |

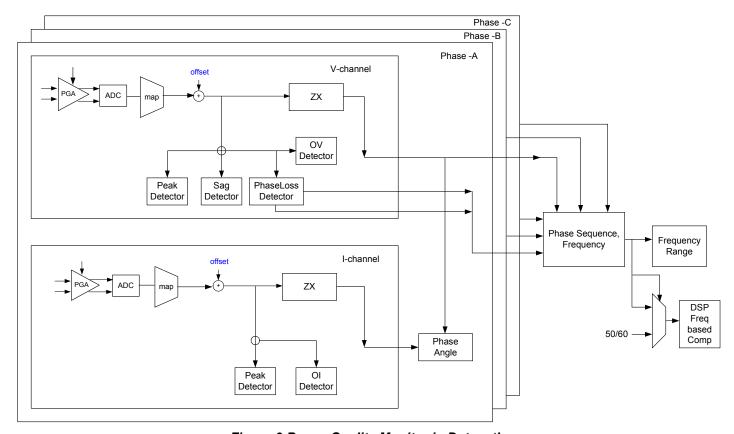

| Figure-9  | Power Quality Monitor in Datapath                                      | . 18 |

| Figure-10 | Block Diagram in Normal Mode                                           | . 21 |

| Figure-11 | Block Diagram in Idle Mode                                             | . 22 |

| Figure-12 | Block Diagram in Detection Mode                                        | . 24 |

| Figure-13 | Block Diagram in Partial Measurement mode                              | . 25 |

| Figure-14 | Power Mode Transition                                                  | . 26 |

| Figure-15 | Segment Gain Compensation                                              | . 28 |

| Figure-16 | Slave Mode                                                             | . 30 |

| Figure-17 | Read Sequence                                                          | . 31 |

| Figure-18 | Write Sequence                                                         | . 31 |

|           | CRC Checking Diagram                                                   |      |

| Figure-20 | IRQ and WarnOut Generation                                             | . 40 |

| Figure-21 | Current Detection Register Latching Scheme                             | . 48 |

| Figure-22 | SPI Timing Diagram                                                     | . 76 |

| Figure-23 | Power On Reset Timing (M90E32AS and MCU are Powered on Simultaneously) | . 77 |

| Figure-24 | Power On Reset Timing in Normal & Partial Measurement Mode             | . 77 |

| Figure-25 | Zero-Crossing Timing Diagram (per phase)                               | . 78 |

| Figure-26 | Voltage Sag and Phase Loss Timing Diagram                              | . 79 |

|           |                                                                        |      |

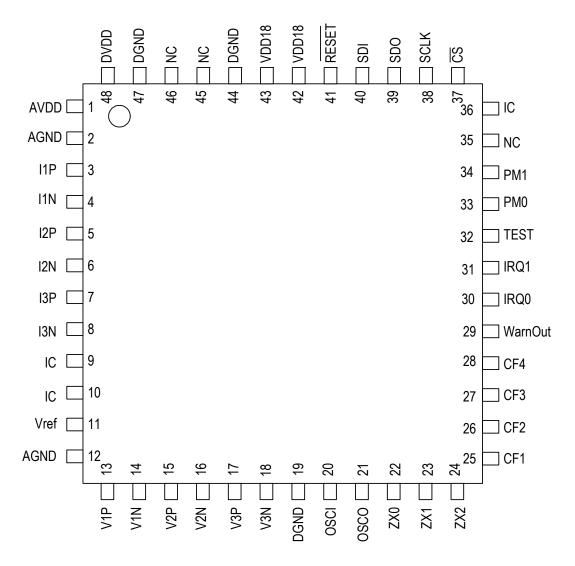

# 1 PIN ASSIGNMENT

Figure-2 Pin Assignment (Top View)

# 2 PIN DESCRIPTION

**Table-1 Pin Description**

| Name       | Pin No.    | I/O | Type   | Description                                                                                                                                                                                                                                                                                             |

|------------|------------|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset      | 41         | I   | LVTTL  | Reset: Reset Pin (active low) This pin should connect to ground through a 0.1 $\mu$ F filter capacitor and a 10k $\Omega$ resistor to VDD. In application it can also directly connect to one output pin from microcontroller (MCU).                                                                    |

| AVDD       | 1          | I   | Power  | AVDD: Analog Power Supply This pin provides power supply to the analog part. This pin should connect to DVDD and be decoupled with a 0.1μF capacitor.                                                                                                                                                   |

| DVDD       | 48         | I   | Power  | DVDD: Digital Power Supply This pin provides power supply to the digital part. It should be decoupled with a $10\mu F$ capacitor and a $0.1\mu F$ capacitor.                                                                                                                                            |

| VDD18      | 42, 43     | Р   | Power  | VDD18: Digital Power Supply (1.8 V) These two pins should be connected together and connected to ground through a 10µF capacitor.                                                                                                                                                                       |

| DGND       | 19, 44, 47 | I   | Power  | DGND: Digital Ground                                                                                                                                                                                                                                                                                    |

| AGND       | 2, 12      | 1   | Power  | AGND: Analog Ground                                                                                                                                                                                                                                                                                     |

| I1P<br>I1N | 3<br>4     | I   | Analog | I1P: Positive Input for Analog ADC Channel I1N: Negative Input for Analog ADC Channel These pins are differential inputs for analog ADC channel. These 6 analog ADC channels can be flexibly mapped, refer to 3.4 Analog digital Channel Mapping. <sup>1</sup>                                          |

| 12P<br>12N | 5<br>6     | I   | Analog | I2P: Positive Input for Analog ADC Channel I2N: Negative Input for Analog ADC Channel These pins are differential inputs for analog ADC channel. These 6 analog ADC channels can be flexibly mapped, refer to 3.4 Analog                                                                                |

| 13P<br>13N | 7 8        | I   | Analog | digital Channel Mapping.   I3P: Positive Input for Analog ADC Channel I3N: Negative Input for Analog ADC Channel These pins are differential inputs for analog ADC channel. These 6 analog ADC channels can be flexibly mapped, refer to 3.4 Analog                                                     |

| Vref       | 11         | 0   | Analog | digital Channel Mapping. $^1$ Vref: Output Pin for Reference Voltage  This pin should be decoupled with a $4.7\mu F$ capacitor, it is better to add a $0.1\mu F$ ceramic capacitor.                                                                                                                     |

| V1P<br>V1N | 13<br>14   | I   | Analog | V1P: Positive Input for Analog ADC Channel V1N: Negative Input for Analog ADC Channel These pins are differential inputs for analog ADC channel. These 6 analog ADC channels can be flexibly mapped, refer to 3.4 Analog                                                                                |

| V2P<br>V2N | 15<br>16   | I   | Analog | digital Channel Mapping. <sup>1</sup> V2P: Positive Input for Analog ADC Channel  V2N: Negative Input for Analog ADC Channel  These pins are differential inputs for analog ADC channel.  These 6 analog ADC channels can be flexibly mapped, refer to 3.4 Analog digital Channel Mapping. <sup>1</sup> |

| V3P<br>V3N | 17<br>18   | I   | Analog | V3P: Positive Input for Analog ADC Channel V3N: Negative Input for Analog ADC Channel These pins are differential inputs for analog ADC channel. These 6 analog ADC channels can be flexibly mapped, refer to 3.4 Analog digital Channel Mapping. <sup>1</sup>                                          |

**Table-1 Pin Description (Continued)**

| This pin is asserted when one or more events in the EMMIntStateO register (1CCH), in Detection mode, the IRQ0 state is cleared when one or more events in the EMMIntState1 register (1DOH), in Detection mode, the IRQ1 state is cleared when entering or exiting Detection mode.    This pin is asserted when one or more events in the EMMIntState1 register (1DOH).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Name    | Pin No.    | I/O            | Туре  | Description                                                                                                                                                                                                                                          |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|----------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| OSCO  21 O OSC A 16.384 MHz crystal is connected between OSCI and OSCO. There are two on-chip capacitors, therefore no need of external capacitors.  ZX0 22 C YX1 23 O LVTTL  These pins are asserted when voltage or current crosses zero. Zero-crossing mode can be configured by the ZXConfig register (07H).  CF1 25 O LVTTL  CF1: (all-phase-sum total) Active Energy Pulse Output  CF2 26 O LVTTL  CF2: (all-phase-sum total) Reactive/ Apparent Energy Pulse Output  The output of this pin is determined by the CF2varh bit (b7, MMode0).  CF3 27 O LVTTL  CF3: (all-phase-sum total) Active Fundamental Energy Pulse Output  CF4 28 O LVTTL  CF3: (all-phase-sum total) Active Fundamental Energy Pulse Output  WarnOut 29 O LVTTL  CF3: (all-phase-sum total) Active Fundamental Energy Pulse Output  WarnOut: Fatal Error Warning  This pin is asserted high when there is metering related parameter check-sum error. Otherwise this pin stays low. Refer to 5.2.2 IRQ and WarnOut Signal Generation.  IRQ0: Interrupt Output 0  This pin is asserted when one or more events in the EMMintState0 register (1CCH).  In Detection mode, the IRQ0 is used to indicate the output of current detector. The IRQ0 state is cleared when entering or exiting Detection mode.  RR01: Interrupt Output 1  This pin is asserted when there is no bit set in the EMMintState1 register (1DOH).  In Detection mode, the IRQ1 is used to indicate the output of current detector. The IRQ0 state is cleared when entering or exiting Detection mode.  PM0 33 I LVTTL  This pin is asserted when fore or more events in the EMMintState1 register (1DOH).  In Detection mode, the IRQ1 is used to indicate the output of current detector. The IRQ1 state is cleared when entering or exiting Detection mode.  PM1 34 I LVTTL  This pin is used as the clock for the SPI interface. Refer to Table-2.  CS: Chip Select (Active Low)  In SPI mode, this pin must be driven from high to low for each read/ write operation, and maintain low for the entire operation.  SCLK 38 I LVTTL  This pin is used as the data output for | OSCI    | 20         | ı              | OSC   |                                                                                                                                                                                                                                                      |  |

| ZX1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | osco    | 21         | 0              | osc   | A 16.384 MHz crystal is connected between OSCI and OSCO. There are                                                                                                                                                                                   |  |

| CF1 25 O LVTTL CF1: (all-phase-sum total) Active Energy Pulse Output  CF2 26 O LVTTL CF1: (all-phase-sum total) Active Energy Pulse Output  CF2 26 O LVTTL CF2: (all-phase-sum total) Reactive/ Apparent Energy Pulse Output  The output of this pin is determined by the CF2 varh bit (b7, MMode0).  CF3 (all-phase-sum total) Active Fundamental Energy Pulse Output  CF4 28 O LVTTL CF4: (all-phase-sum total) Active Fundamental Energy Pulse Output  WarnOut 29 O LVTTL CF4: (all-phase-sum total) Active Harmonic Energy Pulse Output  WarnOut Eatal Error Warning  This pin is asserted high when there is metering related parameter check-sum error. Otherwise this pin stays low. Refer to 5.2.2 IRQ and WarnOut Signal Generation.  IRQ0: Interrupt Output 0  This pin is asserted when one or more events in the EMMIntStateO register (1CCH).  In Detection mode, the IRQ0 is used to indicate the output of current detector. The IRQ0 state is cleared when there is no bit set in the EMMIntStateI register (1D0H).  In Detection mode, the IRQ1 is used to indicate the output of current detector. The IRQ1 state is cleared when there is no bit set in the EMMIntStateI register (1D0H).  In Detection mode, the IRQ1 is used to indicate the output of current detector. The IRQ1 state is cleared when entering or exiting Detection mode.  PM0 33 I² LVTTL PM10: Power Mode Configuration These two pins define the power mode of M90E32AS. Refer to Table-2.  CS: Chip Select (Active Low)  In SPI mode, this pin must be driven from high to low for each read/ write operation.  SCLK Serial Clock This pin is used as the clock for the SPI mode. Refer to 4 SPI Interface.  SDI 40 I² LVTTL This pin is used as the data output for the SPI mode. Refer to 4 SPI Interface.  SDI Sorial Data Input This pin is hould be always connected to DGND in system application.                                                                                                                                                                                                                            | ZX1     | 23         | 0              | LVTTL | These pins are asserted when voltage or current crosses zero. Zero-cross-                                                                                                                                                                            |  |

| CF2 26 O LVTTL CF2: (all-phase-sum total) Reactive/ Apparent Energy Pulse Output The output of this pin is determined by the CF2varh bit (b7, MMode0).  CF3 27 O LVTTL CF3: (all-phase-sum total) Active Fundamental Energy Pulse Output CF4: (all-phase-sum total) Active Fundamental Energy Pulse Output WarnOut Pulse Output UVTTL CF4: (all-phase-sum total) Active Harmonic Energy Pulse Output WarnOut: Fatal Error Warning This pin is asserted high when there is metering related parameter check-sum error. Otherwise this pin stays low. Refer to 5.2.2 IRQ and WarnOut Signal Generation.  IRQ0: Interrupt Output 0 This pin is asserted when one or more events in the EMMIntState0 register (1CCH) occur. It is deasserted when there is no bit set in the EMMIntState0 register (1CCH). In Detection mode, the IRQ0 is used to indicate the output of current detector. The IRQ0 state is cleared when entering or exiting Detection mode.  IRQ1: Interrupt Output 1 This pin is asserted when one or more events in the EMMIntState1 register (1CCH). In Detection mode, the IRQ1 is used to indicate the output of current detector. The IRQ1 state is cleared when there is no bit set in the EMMIntState1 register (1DOH). In Detection mode, the IRQ1 is used to indicate the output of current detector. The IRQ1 state is cleared when entering or exiting Detection mode.  PM0 33 I² LVTTL Server Worde Configuration These two pins define the power mode of M90E32AS. Refer to Table-2.  CS: Chip Select (Active Low) In SPI mode, this pin must be driven from high to low for each read/ write operation, and maintain low for the entire operation.  SCLK: Serial Clock This pin is used as the clock for the SPI interface. Refer to 4 SPI Interface.  SD0: Serial Data Output This pin is used as the data output for the SPI mode. Refer to 4 SPI Interface.  SD1: Serial Data Untput This pin is used as the data input for the SPI mode. Refer to 4 SPI Interface.  TEST 32 I LVTTL This pin should be always connected to DGND in system application.                                        |         | 25         | 0              | LVTTL |                                                                                                                                                                                                                                                      |  |

| CF4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CF2     | 26         | 0              |       | CF2: (all-phase-sum total) Reactive/ Apparent Energy Pulse Output                                                                                                                                                                                    |  |

| WarnOut   29   O   LVTTL   WarnOut: Fatal Error Warning   This pin is asserted high when there is metering related parameter checksum error. Otherwise this pin stays low. Refer to 5.2.2 IRQ and WarnOut   Signal Generation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CF3     | 27         | 0              | LVTTL | CF3: (all-phase-sum total) Active Fundamental Energy Pulse Output                                                                                                                                                                                    |  |

| WarnOut   29   O   LVTTL   This pin is asserted high when there is metering related parameter checks sum error. Otherwise this pin stays low. Refer to 5.2.2 IRQ and WarnOut Signal Generation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CF4     | 28         | 0              | LVTTL | CF4: (all-phase-sum total) Active Harmonic Energy Pulse Output                                                                                                                                                                                       |  |

| This pin is asserted when one or more events in the EMMIntState0 register (1CCH) occur. It is deasserted when there is no bit set in the EMMIntState0 register (1CCH). In Detection mode, the IRQ0 is used to indicate the output of current detector. The IRQ0 state is cleared when entering or exiting Detection mode.  IRQ1 31 O LVTTL  IRQ1: Interrupt Output 1 This pin is asserted when one or more events in the EMMIntState1 register (1DOH) occur. It is deasserted when there is no bit set in the EMMIntState1 register (1DOH). In Detection mode, the IRQ1 is used to indicate the output of current detector. The IRQ1 state is cleared when entering or exiting Detection mode.  PM0 33 I² LVTTL  PM1/0: Power Mode Configuration These two pins define the power mode of M90E32AS. Refer to Table-2.  CS: Chip Select (Active Low) In SPI mode, this pin must be driven from high to low for each read/ write operation, and maintain low for the entire operation.  SCLK: Serial Clock This pin is used as the clock for the SPI interface. Refer to 4 SPI Interface.  SDO: Serial Data Output This pin is used as the data output for the SPI mode. Refer to 4 SPI Interface.  SDO: Serial Data Input This pin is used as the data input for the SPI mode. Refer to 4 SPI Interface.  SDI: Serial Data Input This pin is used as the data input for the SPI mode. Refer to 4 SPI Interface.  SDI: Serial Data Input This pin is used as the data input for the SPI mode. Refer to 4 SPI Interface.  SDI: Serial Data Input This pin is used as the data input for the SPI mode. Refer to 4 SPI Interface.  TEST 32 I LVTTL This pin should be always connected to DGND in system application.  IC 9, 10, 36 LVTTL These pins should be always connected to DGND in system application.                                                                                                                                                                                                                                                                                                                       | WarnOut | 29         | 0              | LVTTL | This pin is asserted high when there is metering related parameter check-<br>sum error. Otherwise this pin stays low. Refer to 5.2.2 IRQ and WarnOut                                                                                                 |  |

| This pin is asserted when one or more events in the EMMIntState1 register (1D0H) occur. It is deasserted when there is no bit set in the EMMIntState1 register (1D0H).  In Detection mode, the IRQ1 is used to indicate the output of current detector. The IRQ1 state is cleared when entering or exiting Detection mode.  PM0 33 I² LVTTL PM1/0: Power Mode Configuration These two pins define the power mode of M90E32AS. Refer to Table-2.  CS: Chip Select (Active Low) In SPI mode, this pin must be driven from high to low for each read/ write operation, and maintain low for the entire operation.  SCLK 38 I² LVTTL SCLK: Serial Clock This pin is used as the clock for the SPI interface. Refer to 4 SPI Interface.  SDO: Serial Data Output This pin is used as the data output for the SPI mode. Refer to 4 SPI Interface.  SDO: Serial Data Input This pin is used as the data input for the SPI mode. Refer to 4 SPI Interface.  TEST 32 I LVTTL This pin should be always connected to DGND in system application.  IC 9, 10, 36 LVTTL These pins should be always connected to DGND in system application.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IRQ0    | 30         | 0              | LVTTL | This pin is asserted when one or more events in the EMMIntState0 register (1CCH) occur. It is deasserted when there is no bit set in the EMMIntState0 register (1CCH).  In Detection mode, the IRQ0 is used to indicate the output of current detec- |  |

| PM1 34   I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IRQ1    | 31         | 0              | LVTTL | This pin is asserted when one or more events in the EMMIntState1 register (1D0H) occur. It is deasserted when there is no bit set in the EMMIntState1 register (1D0H).  In Detection mode, the IRQ1 is used to indicate the output of current detec- |  |

| CS   SCI   Chip Select (Active Low)   In SPI mode, this pin must be driven from high to low for each read/ write operation, and maintain low for the entire operation.    SCLK   38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            | l <sup>2</sup> | LVTTL | <del>-</del>                                                                                                                                                                                                                                         |  |

| SDO 39 O LVTTL This pin is used as the clock for the SPI interface. Refer to 4 SPI Interface.  SDO: Serial Data Output This pin is used as the data output for the SPI mode. Refer to 4 SPI Interface.  SDI 40 I² LVTTL SDI: Serial Data Input This pin is used as the data input for the SPI mode. Refer to 4 SPI Interface.  TEST 32 I LVTTL This pin should be always connected to DGND in system application.  IC 9, 10, 36 LVTTL These pins should be always connected to DGND in system application.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            | l <sup>2</sup> | LVTTL | CS: Chip Select (Active Low) In SPI mode, this pin must be driven from high to low for each read/ write                                                                                                                                              |  |

| SDO 39 O LVTTL This pin is used as the data output for the SPI mode. Refer to 4 SPI Interface.  SDI 40 I² LVTTL SDI: Serial Data Input This pin is used as the data input for the SPI mode. Refer to 4 SPI Interface.  TEST 32 I LVTTL This pin should be always connected to DGND in system application.  IC 9, 10, 36 LVTTL These pins should be always connected to DGND in system application.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SCLK    | 38         | l <sup>2</sup> | LVTTL |                                                                                                                                                                                                                                                      |  |

| TEST 32 I LVTTL This pin is used as the data input for the SPI mode. Refer to 4 SPI Interface.  IC 9, 10, 36 LVTTL These pins should be always connected to DGND in system application.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SDO     | 39         | 0              | LVTTL | This pin is used as the data output for the SPI mode. Refer to 4 SPI Inter-                                                                                                                                                                          |  |

| IC 9, 10, 36 LVTTL These pins should be always connected to DGND in system application.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SDI     | 40         | l <sup>2</sup> | LVTTL | SDI: Serial Data Input This pin is used as the data input for the SPI mode. Refer to 4 SPI Interface.                                                                                                                                                |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TEST    | 32         | I              | LVTTL | This pin should be always connected to DGND in system application.                                                                                                                                                                                   |  |

| NC 35, 45, 46 NC: These pins should be left open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | IC      | 9, 10, 36  |                | LVTTL | These pins should be always connected to DGND in system application.                                                                                                                                                                                 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | NC      | 35, 45, 46 |                |       | NC: These pins should be left open.                                                                                                                                                                                                                  |  |

Note 1: The channel mapping is only valid in Normal mode and Patial Measurement mode.

Note 2: All the digital input pins except OSCI are 5 V compatible.

# 3 FUNCTION DESCRIPTION

#### 3.1 POWER SUPPLY

The M90E32AS works with single power rail 3.3V. An on-chip voltage regulator regulates the 1.8V voltage for the digital logic.

The regulated 1.8V power is connected to the VDD18 pin. It needs to be bypassed by an external capacitor.

The M90E32AS has four power modes: Normal (N mode), Partial Measurement (M mode), Detection (D mode) and Idle (I mode). In Idle and Detection modes the 1.8V power regulator is not turned on and the digital logic is not powered. When the logic is not powered, all the configured register values are not kept (all context lost) except for Detection mode related registers (10H~13H) for Detection mode configuration.

The registers in Partial Measurement mode or Normal mode have to be re-configured when transiting from Idle or Detection mode. Refer to 3.8 Power Mode for power mode details.

#### 3.2 CLOCK

The M90E32AS has an on-chip oscillator and can directly connect to an external crystal.

The OSCI pin can also be driven with a clock source.

The oscillator will be powered down in Idle and Detection power modes, as described in 3.8 Power Mode.

#### 3.3 RESET

There are three reset sources for the M90E32AS:

- RESET pin

- On-chip Power On Reset circuit

- Software Reset generated by the SoftReset register

# 3.3.1 RESET PIN

The  $\overline{\text{RESET}}$  pin can be asserted to reset the M90E32AS. The  $\overline{\text{RESET}}$  pin has RC filter with typical time constant of  $2\mu s$  in the I/O, as well as a  $2\mu s$  (typical) de-glitch filter.

Any reset pulse that is shorter than 2µs can not reset the M90E32AS.

#### 3.3.2 POWER ON RESET (POR)

The POR circuit resets the M90E32AS at power up.

POR circuit triggers reset when:

- DVDD power up with crossing the power-up threshold. Refer to Figure-24.

- VDD18 regulator changing from disable to enable, i.e. from Idle or Detection mode to Partial Measurement mode or Normal mode. Refer to Figure-23.

# 3.3.3 SOFTWARE RESET

Chip reset can be triggered by writing to the SoftReset register in Normal mode. The software reset is the same as the reset scope generated from the RESET pin or POR.

These three reset sources have the same reset scope.

All digital logics and registers except for some special registers will be subjected to reset.

- Interface logic: clock dividers

- Digital core/ logic: All registers except for some special registers. Refer to 5.3.1 Detection Mode Registers.

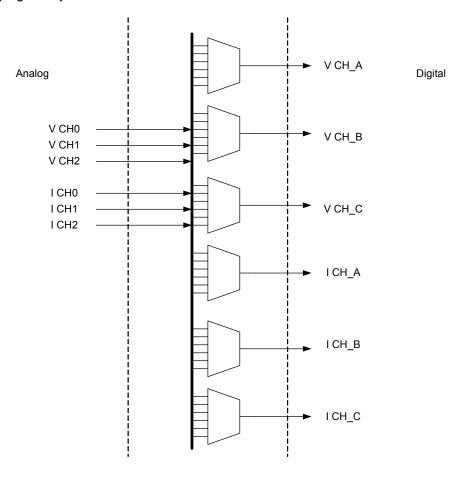

# 3.4 ANALOG/DIGITAL CHANNEL MAPPING

Analog channel to digital channel mapping:

The 6 analog ADC channels can be flexibly mapped to the 6 digital metering/measuring channels (V/I phase A/B/C). Refer to the ChannelMapI and ChannelMapI registers for configuration.

Note that channel mapping is only valid in Normal mode and Patial Measurement mode.

Flexible Channel mapping

Figure-3 Channel to Phase Mapping

# 3.5 METERING FUNCTION

Metering is enabled when any of the MeterEn bits are set.

When metering is not enabled, the CF pulse will not be generated and energy accumulator will not accumulate energy. All energy accumulation related status will be cleared, while startup/noload handling block related status will be still working.

The accumulated energy will be converted to pulse frequency on the CF pins and stored in the corresponding energy registers.

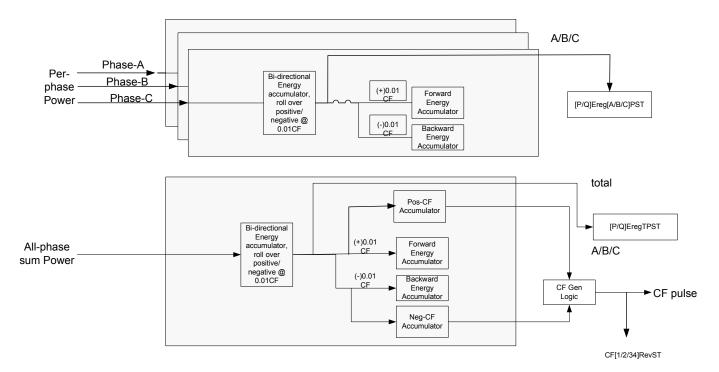

#### 3.5.1 THEORY OF ENERGY REGISTERS

The energy accumulation runs at 1 MHz clock rate by accumulating the power value calculated by the DSP processor.

The power accumulation process is equivalent to digitally integrating the instantaneous power with a delta-time of about 1 us. The accumulated energy is used to calculate the CF pulses and the corresponding internal energy registers.

The accumulated energy is converted to frequency of the CF pulses. One CF usually corresponds to 1KWh / MC (MC is Meter Constant, e.g. 3200 imp/kWh), and is usually referenced as an energy unit in this datasheet. The internal energy resolution for accumulation and conversion is 0.01 CF.

The 0.01 CF pulse energy constant is referenced as 'PL\_constant'.

Within 0.01 CF, forward and reverse energy are counteracted. When energy exceeds 0.01 pulse, the respective forward/reverse energy is increased.

Take the example of active energy. Suppose:

T0: Forward energy register is 12.34 pulses and reverse energy register is 1.23 pulses.

From t0 to t1: 0.005 forward pulses appeared.

From t1 to t2: 0.004 reverse pulses appeared.

From t2 to t3: 0.005 reverse pulses appeared.

From t3 to t4: 0.007 reverse pulses appeared.

The following table illustrates the process of energy accumulation process:

|                                  | t0      | t1     | t2     | t3     | t4    |

|----------------------------------|---------|--------|--------|--------|-------|

| Input energy                     | + 0.005 | -0.004 | -0.005 | -0.007 |       |

| Bidirectional energy accumulator | 0.005   | 0.001  | -0.004 | -0.001 |       |

| Forward 0.01 CF                  | 0       | 0      | 0      | 0      |       |

| Reverse 0.01CF                   | 0       | 0      | 0      | 1      |       |

| Forward energy register          | 12.34   | 12.34  | 12.34  | 12.34  | 12.34 |

| Reverse energy register          | 1.23    | 1.23   | 1.23   | 1.23   | 1.24  |

When forward/reverse energy reaches 0.01 pulse, the respective register is updated. When forward or reverse energy reaches 1 pulse, CFx pins output pulse and the CFxRevST bits (b3~0, EMMState0) are updated. Refer to Figure-4.

Figure-4 Energy Accumulation Diagram

For all-phase-sum total of active, reactive and (arithmetic sum) apparent energy, the associated power is obtained by summing the power of the three phases. The accumulation method of all-phase-sum energy is determined by the EnPC/EnPB/EnPA/ABSEnP/ABSEnQ bits (b0~b4, MMode0).

Note that the direction of all-phase-sum power and single-phase power might be different.

#### 3.5.2 ENERGY REGISTERS

The M90E32AS meters non-decomposed total active, reactive and apparent energy, as well as decomposed active fundamental and harmonic energy. The registers are listed as below.

#### 3.5.2.1 Total Energy Registers

Each phase and all-phase-sum has the following registers:

- Active forward/ reverse

- Reactive forward/ reverse

- Apparent energy

Altogether there are 20 energy registers. Those registers are defined in 5.5.1 Regular Energy Registers.

#### 3.5.2.2 Fundamental and Harmonic Energy Registers

The M90E32AS counts decomposed active fundamental and harmonic energy. Reactive energy is not decomposed to fundamental and harmonic.

The fundamental/harmonic energy is accumulated in the same way as active energy accumulation method described above.

#### Registers:

- Fundamental / harmonic

- all-phase-sum / phase A / phase B / phase C

- Forward / reverse

Altogether there are 16 energy registers. Refer to 5.5.2 Fundamental / Harmonic Energy Register.

#### 3.5.3 ENERGY PULSE OUTPUT

CF1 is fixed to be total active energy output (all-phase-sum). Both forward and reverse energy registers can generate the CF pulse (change of forward/ reverse direction can generate an interrupt if enabled).

CF2 is reactive energy output (all-phase-sum) by default. It can also be configured to be arithmetic sum apparent energy output (all-phase-sum).

CF3 is fixed to be active fundamental energy output (all-phase-sum).

CF4 is fixed to be active harmonic energy output (all-phase-sum).

Figure-5 CFx Pulse Output Regulation

For CFx pulse width regulation, refer to Figure-5.

Case1 T>=160ms, Tp=80ms

Case 2 10ms<=T<160ms, Tp=T/2

#### 3.5.4 STARTUP AND NO-LOAD POWER

There are startup power threshold registers (e.g. PStartTh(35H)). Refer to 5.4 Configuration and Calibration Registers. The power threshold registers are defined for all-phase-sum active, reactive and apparent power. The M90E32AS starts metering when the corresponding all-phase-sum power is greater than the startup threshold. When the power value is lower than the startup threshold, energy is not accumulated and it is assumed as in no-load status. Refer to Figure-6.

There are also no-load Current Threshold registers for Active, Reactive and Apparent energy metering participation for each of the 3 phases. If |P|+|Q| is lower than the corresponding power threshold, that particular phase will not be accumulated. Refer to the PStartTh register and other threshold registers.

There are also no-load status bits (the TPnoload/TQnoload bits (b14~15, Fundamental / Harmonic Energy Register)) defined to reflect the no-load status. The M90E32AS does not output any pulse in no-load status. The power-on state is of no-load status.

Figure-6 Active Power Startup/Noload Processing

Figure-7 Fundamental Active Power Startup/Noload Processing

Figure-8 Harmonic Active Power Startup/Noload Processing

# 3.6 MEASUREMENT FUNCTION

Measured parameters can be divided to 8 types as follows: