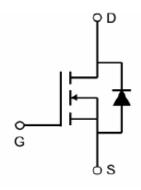

#### N-Channel Enhancement Mode Field Effect Transistor

## **Description**

The ACET4445B uses advanced trench technology to provide excellent  $R_{DS(ON)}$ , low gate charge. This device is suitable for use as a high side switch in SMPS and general purpose applications.

ACET4445B is electrically identical.

RoHS Compliant

#### **Features**

- V<sub>DS</sub> (V) = 30V

- $I_D = 38A \text{ (VGS} = 10V)$

- $R_{DS(ON)} = 6.2 \text{m}\Omega$   $(V_{GS} = 10 \text{V}, \text{Typ})$

- $R_{DS(ON)} < 8.9 m\Omega$   $(V_{GS} = 4.5 V, Typ)$

- Low Qg

- 100% Delta Vsd Tested

- 100% R<sub>g</sub> Tested

**Absolute Maximum Ratings**

| Parameter                               | Symbol                 | Max              | Unit       |     |

|-----------------------------------------|------------------------|------------------|------------|-----|

| Drain-Source Voltage                    |                        | $V_{DSS}$        | 30         | V   |

| Gate-Source Voltage                     |                        | $V_{GSS}$        | ±20        | V   |

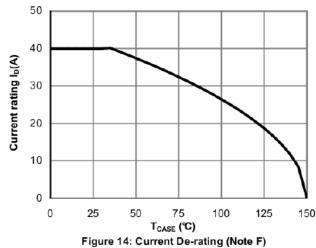

| Drain Current (Continuous)              | T <sub>C</sub> =25 °C  | ı                | 38         | А   |

|                                         | T <sub>C</sub> =100 °C | l <sub>D</sub>   | 18         |     |

| Drain Current (Pulse) <sup>C</sup>      |                        | I <sub>DM</sub>  | 60         |     |

| Drain Current (Continuous)              | T <sub>A</sub> =25 °C  | 1 .              | 11         | А   |

|                                         | T <sub>A</sub> =70 °C  | I <sub>DSM</sub> | 8          |     |

| Power Dissipation <sup>B</sup>          | T <sub>C</sub> =25 °C  | В                | 5          | ۱۸/ |

|                                         | T <sub>C</sub> =100 °C | P <sub>D</sub>   | 3.2        | W   |

| Power Dissipation <sup>A</sup>          | T <sub>A</sub> =25 °C  | В                | 2          | W   |

|                                         | T <sub>A</sub> =70 °C  | P <sub>DSM</sub> | 1.3        | VV  |

| Operating and Storage Temperature Range |                        | $T_{J,}T_{STG}$  | -55 to 150 | °C  |

| Thermal Characteristics                  |              |                 |       |      |  |  |  |

|------------------------------------------|--------------|-----------------|-------|------|--|--|--|

| Parameter                                | Symbol       | Max             | Units |      |  |  |  |

| Maximum Junction-to-Ambient <sup>A</sup> | t≦10s        | Ъ               | 25    | °C/W |  |  |  |

| Maximum Junction-to-Ambient AD           | Steady-State | $R_{\theta JA}$ | 60    | °C/W |  |  |  |

| Maximum Junction-to-Case                 | Steady-State | $R_{	heta JC}$  | 4.2   | °C/W |  |  |  |

# N-Channel Enhancement Mode Field Effect Transistor

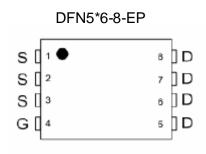

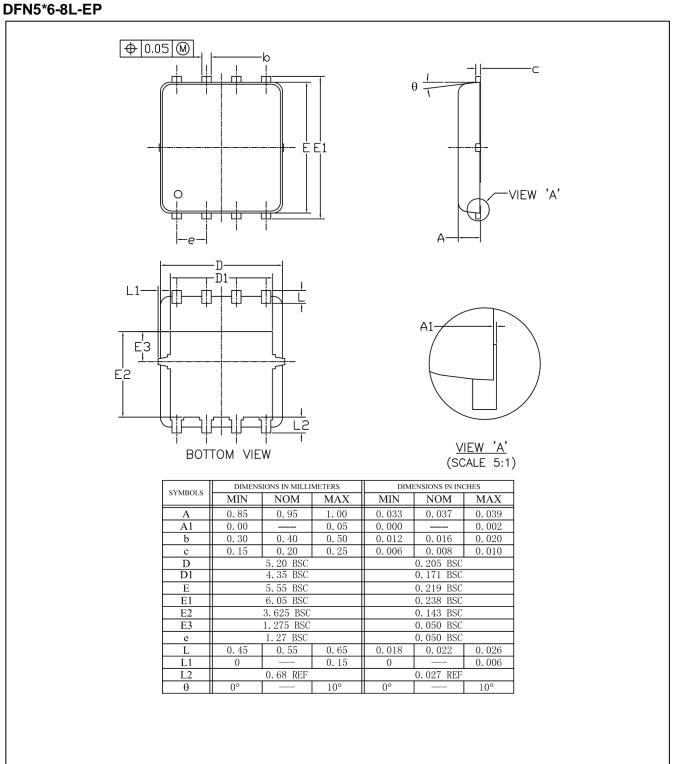

# **Packaging Type**

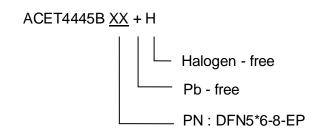

# **Ordering information**

#### N-Channel Enhancement Mode Field Effect Transistor

#### **Electrical Characteristics**T<sub>A</sub>=25 °C unless otherwise noted

| Parameter                             | Symbol              | Conditions                                                              | Min | Тур  | Max | Unit |  |  |  |

|---------------------------------------|---------------------|-------------------------------------------------------------------------|-----|------|-----|------|--|--|--|

| Static                                |                     |                                                                         |     |      |     |      |  |  |  |

| Drain-Source Breakdown Voltage        | $V_{(BR)DSS}$       | $V_{GS} = 0V, I_{D} = 250 \mu A$                                        | 30  |      |     | V    |  |  |  |

| Zero Gate Voltage Drain Current       | I <sub>DSS</sub>    | $V_{DS} = 30 \text{ V}$ , $V_{GS} = 0 \text{V}$                         |     |      | 1   | μΑ   |  |  |  |

| Gate Threshold Voltage                | $V_{GS(TH)}$        | $V_{GS}=V_{DS}$ , $I_{DS}=250\mu A$                                     | 1   |      | 3   | V    |  |  |  |

| Gate Leakage Current                  | I <sub>GSS</sub>    | $V_{GS}=\pm20V$ , $V_{DS}=0V$                                           |     |      | 100 | nA   |  |  |  |

| Drain-Source On-state Resistance      | R <sub>DS(on)</sub> | $V_{GS} = 10V , I_{D} = 12A$                                            |     | 6.2  | 8.5 | mΩ   |  |  |  |

|                                       |                     | $V_{GS} = 4.5V , I_{D} = 10A$                                           |     | 8.9  | 13  |      |  |  |  |

| Forward Transconductance              | <b>g</b> FS         | VDS=10V, ID=12A                                                         | 30  |      |     | S    |  |  |  |

| Diode Forward Voltage                 | $V_{SD}$            | ISD=2A, VGS=0V                                                          |     | 0.71 | 1.0 | V    |  |  |  |

| Maximum Body-Diode Continuous Current | IS                  |                                                                         |     |      | 2   | Α    |  |  |  |

| Switching                             |                     |                                                                         |     |      |     |      |  |  |  |

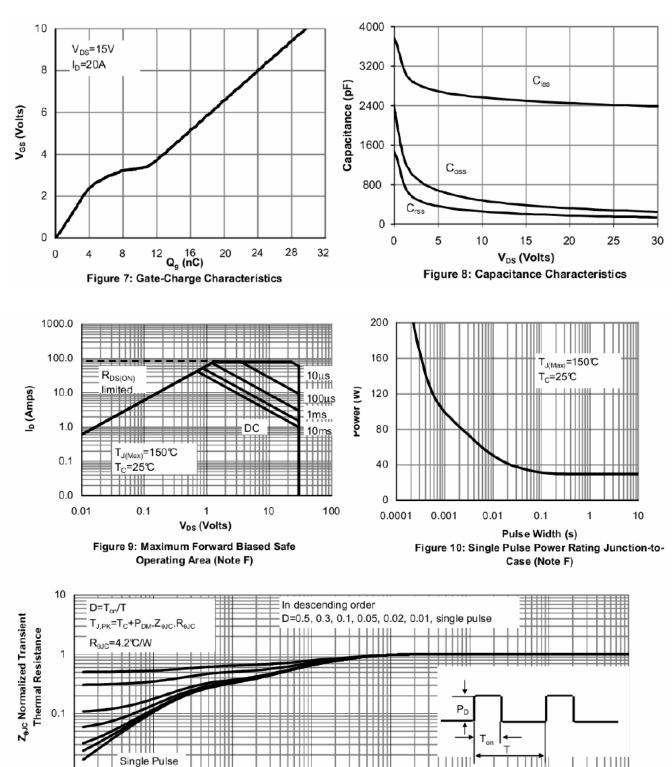

| Total Gate Charge                     | $Q_g$               | $V_{DS}$ =15V, $I_{D}$ =12A $V_{GS}$ =5V                                |     | 7.5  |     | nC   |  |  |  |

| Gate-Source Charge                    | $Q_{gs}$            |                                                                         |     | 1.3  |     |      |  |  |  |

| Gate-Drain Charge                     | $Q_gd$              | V GS-5 V                                                                |     | 4.5  |     |      |  |  |  |

| Turn-On Delay Time                    | T <sub>d(on)</sub>  | $V_{DS}$ =15V, $V_{GS}$ =10V $R_{GEN}$ =6 $\Omega$ , $R_L$ =15 $\Omega$ |     | 10   |     |      |  |  |  |

| Turn-On Rise Time                     | t <sub>f</sub>      |                                                                         |     | 8    |     | ns   |  |  |  |

| Turn-Off Delay Time                   | t <sub>d(off)</sub> |                                                                         |     | 30   |     |      |  |  |  |

| Turn-Off Fall Time                    | t <sub>f</sub>      |                                                                         |     | 5    |     |      |  |  |  |

| Dynamic                               |                     |                                                                         |     |      |     |      |  |  |  |

| Input Capacitance                     | C <sub>iss</sub>    | \/ .=15\/ \/ =0\/                                                       |     | 680  |     |      |  |  |  |

| Output Capacitance                    | C <sub>oss</sub>    | $V_{DS}$ =15V, $V_{GS}$ =0V<br>f=1MHz                                   |     | 150  |     | pF   |  |  |  |

| Reverse Transfer Capacitance          | C <sub>rss</sub>    |                                                                         |     | 70   |     |      |  |  |  |

#### Note:

- A. The value of  $R_{\theta JA}$  is measured with the device mounted on 1in² FR-4 board with 2oz. Copper, in a still air environment with  $T_A$ =25°C. The Power dissipation  $P_{DSM}$  is based on  $R_{\theta JA}$  and the maximum allowed junction temperature of 150°C. The value in any given application depends on the user's specific board design.

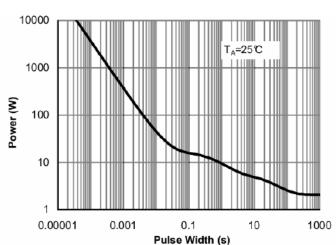

- B. The power dissipation  $P_D$  is based on  $T_{J(MAX)}$ =150°C, using junction-to-case thermal resistance, and is more useful in setting the upper dissipation limit for cases where additional heatsinking is used.

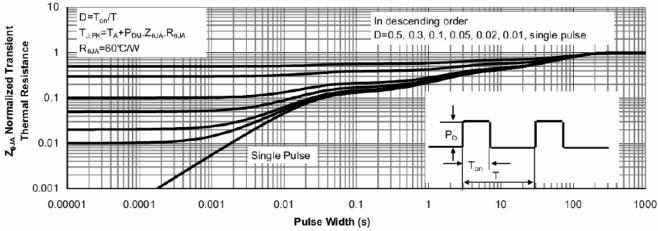

- C. Repetitive rating, pulse width limited by junction temperature  $T_{J(MAX)}$ =150°C. Ratings are based on low frequency and duty cycles to keep initial  $T_J$  =25°C.

- D. The  $R_{\theta JA}$  is the sum of the thermal impedence from junction to case  $R_{\theta JC}$  and case to ambient.

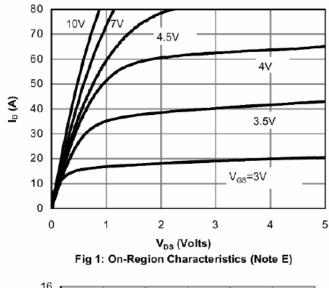

- E. The static characteristics in Figures 1 to 6 are obtained using <300µs pulses, duty cycle 0.5% max.

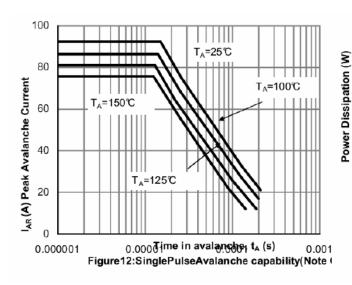

- F. These curves are based on the junction-to-case thermal impedence which is measured with the device mounted to a large heatsink, assuming a maximum junction temperature of  $T_{J(MAX)}=150$ °C. The SOA curve provides a single pulse rating.

- G. The maximum current rating is package limited.

- H. These tests are performed with the device mounted on  $1\text{in}^2$  FR-4 board with 2oz. Copper, in a still air environment with  $T_A=25^{\circ}\text{C}$

### N-Channel Enhancement Mode Field Effect Transistor

## **Typical Performance Characteristics**

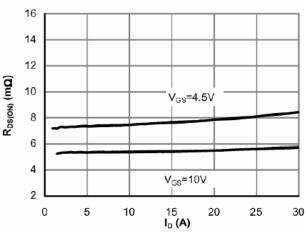

Figure 3: On-Resistance vs. Drain Current and Gate Voltage (Note E)

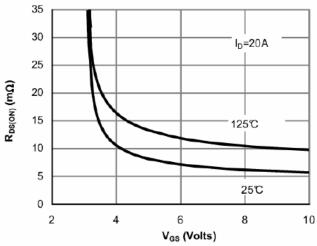

Figure 5: On-Resistance vs. Gate-Source Voltage (Note E)

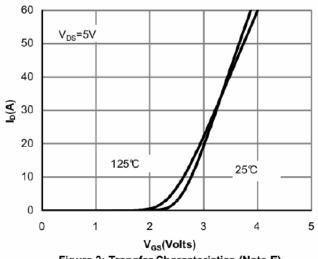

Figure 2: Transfer Characteristics (Note E)

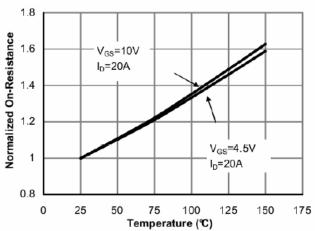

Figure 4: On-Resistance vs. Junction Temperature (Note E)

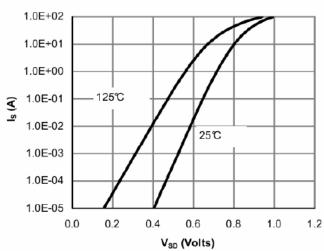

Figure 6: Body-Diode Characteristics (Note E)

0.00001

0.0001

0.001

# ACET4445B

### N-Channel Enhancement Mode Field Effect Transistor

Pulse Width (s)

Figure 11: Normalized Maximum Transient Thermal Impedance (Note F)

0.1

0.01

5

100

10

#### N-Channel Enhancement Mode Field Effect Transistor

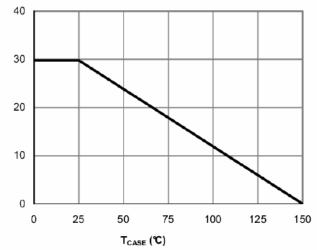

Figure 13: Power De-rating (Note F)

### **Typical Performance Characteristics**

Figure 15: Single Pulse Power Rating Junction-to-Ambient (Note H)

Figure 16: Normalized Maximum Transient Thermal Impedance (Note H)

## N-Channel Enhancement Mode Field Effect Transistor

## **Packing Information**

## N-Channel Enhancement Mode Field Effect Transistor

#### Notes

ACE does not assume any responsibility for use as critical components in life support devices or systems without the express written approval of the president and general counsel of ACE Electronics Co., LTD. As sued herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and shoes failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

ACE Technology Co., LTD. http://www.ace-ele.com/